Изобретение относится к цифровым вычислительным машинам.

Известны логические схемы, содержащие диод с накоплением заряда, один вывод которого соединен с выходом п-входовой диодной Схемы «ИЛИ и через диод - с источником синхронизирующих импульсов, а другой вывод соединен со входом - выходом триггера на туннельном диоде (ТД).

Однако в известных устройствах на выходе диода с накоплением заряда (ДНЗ) появляется токовая помеха, способная переключить триггер.

Предложенная логическая схема отличается от известных тем, что содержит разделительный диод, включенный между диодом с накоплением заряда и туннельным диодом, и обращенный диод, подключенный между точкой соединения разделительного диода с диодом с накоплением заряда и общей щиной питания.

Эти отличия новы и полезны, так как позволяют расширить функциональные возможности схемы и повысить ее надежность.

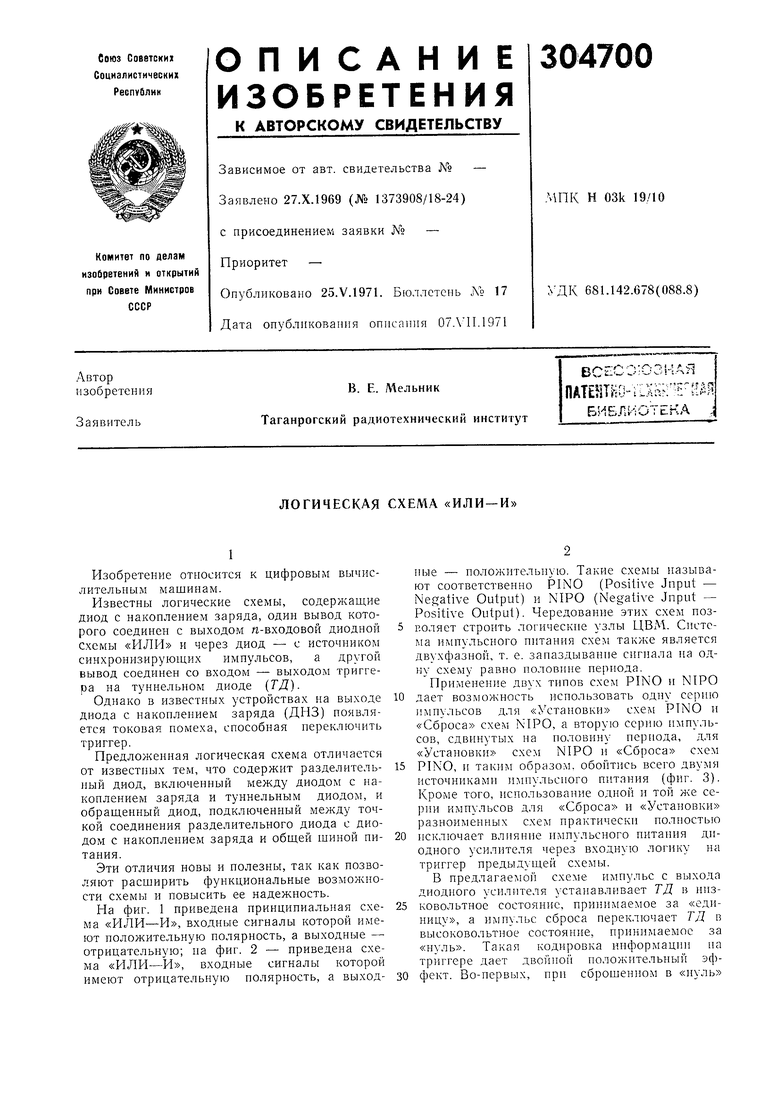

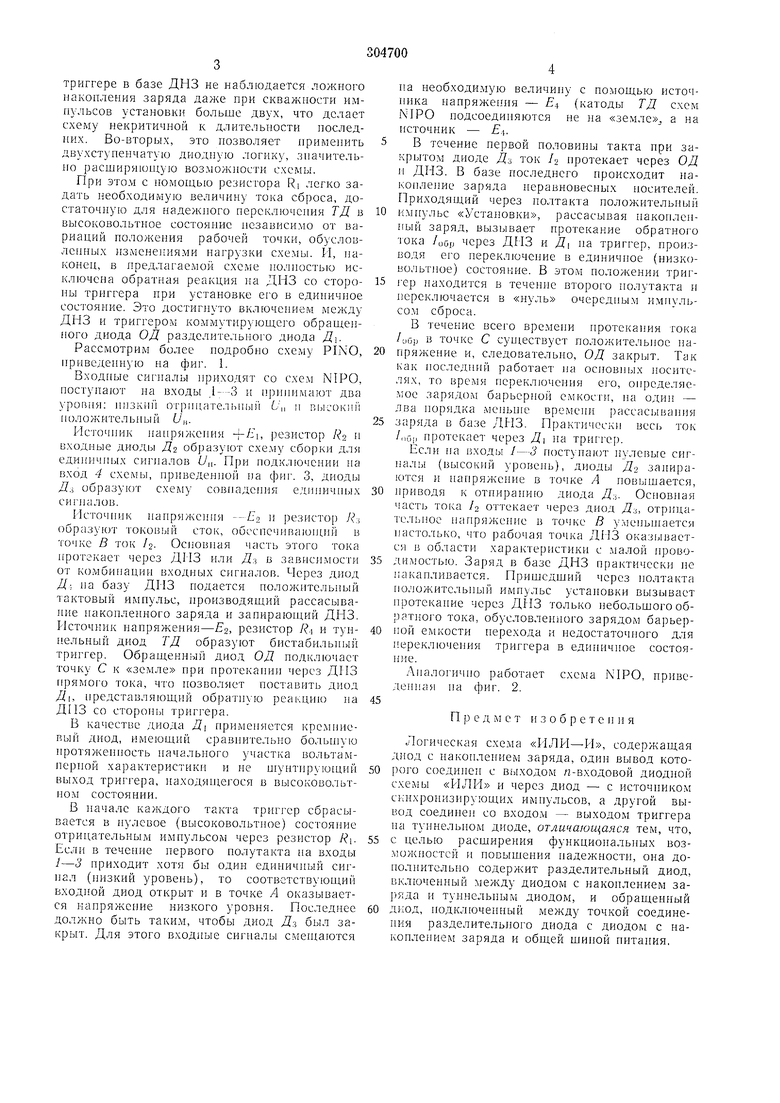

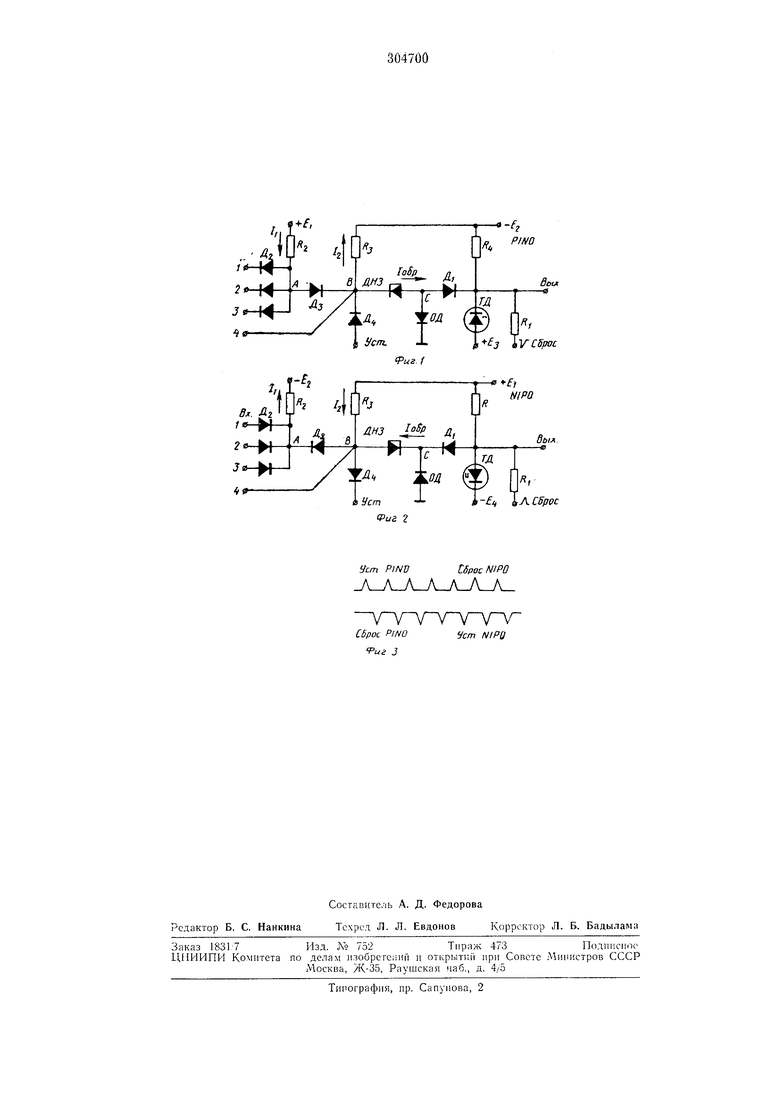

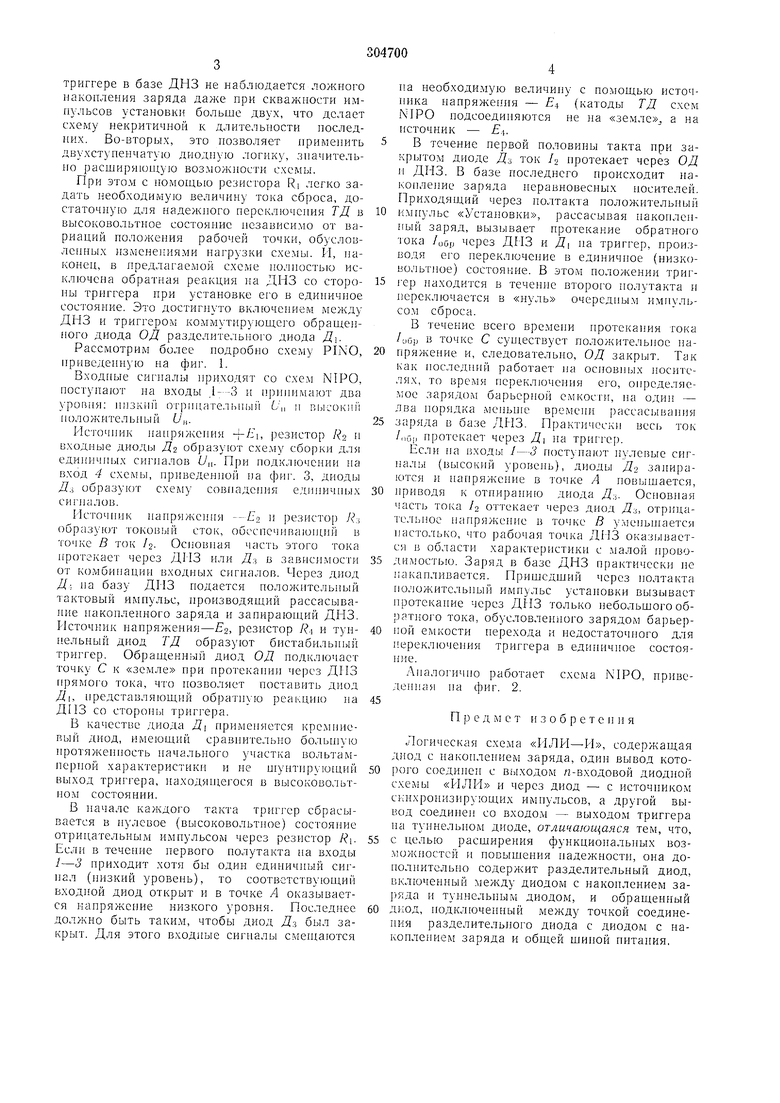

На фиг. 1 приведена принципиальная схема «ИЛИ--И, входные сигналы которой имеют положительную полярность, а выходные - отрицательную; на фиг. 2 - приведена схема «ИЛИ-И, входные сигналы которой имеют отрицательную полярность, а выходные - положительную. Такие схемы называют соответственно PINO (Positive Jnput - Negative Output) и NIPO (Negative Jnput - Positive Output). Чередование этих схем позЕоляет строить логические узлы ЦВМ. Система импульсного ннтания схем также является двухфазной, т. е. запаздывание сигнала на одну схему равно половине периода.

Применение двух типов схем PINO и NIPO

дает возможность иснользовать одну серию пмнульсов для «Установки схем PINO и «Сброса схем NIPO, а вторую серию имнульсов, сдвинутых на половин} периода, для «Установки схем NIPO и «Сброса схем

PINO, и таким образом, обойтись всего двумя источннкамп импульсного питания (фиг. 3). Кроме того, использоватше одной и той же серии имнульсов для «Сброса и «Установки разноименных схем практически полностью

исключает влияние импульсного нитаппя днодного усилителя через входную логику на триггер предыдущей схемы.

В предлагаемой схеме импульс с выхода диодного усилителя устанавливает ТД в низковольтное состояние, принимаемое за «единицу, а импульс сброса переключает ТД в высоковольтное состояние, принимаемое за «нуль. Такая кодировка информацнп па триггере дает двойной положительный эфтриггере в базе ДНЗ не наблюдается ложного накопления заряда даже при скважности импульсов установки больше двух, что делает схему некритичной к длительности последних. Во-вторых, это позволяет применить двухступенчатую диодную логику, значительно расширяияцу о возлюжпости схемы.

При этом с помощью резисгора легко задать необходимую величину тока сброса, достаточную для надежного переключения ТД в высоковольтное состояиис независимо от вариаций положения рабочей точки, обусловленных изменениями нагрузки схемы. И, наконеп, в нредлагаемой схеме нолноетью исключена обратная реакция на ДНЗ со стороны трнггера при установке его в единичное состояние. Это достигнуто включением между ДНЗ и триггером коммутирующего обран 1енfioro диода ОД разделительного днода Hi.

Рассмотрим более нодробно схему PINO, приведенную на фиг. 1.

Входные сигналы приходят со схем NIPO, ноступают на входы .1--3 и прН1И1мают два уровпя; HiOKHii отр1П1ателыП) Ln п положительный f/,,.

Источник напряжения -}-Е, резистор ч входные диоды Д-2 образуют схему сборки для единичных сигналов U. Нри подключении на вход 4 схемы, приведеппой па фиг. 3, диоды Дл образуют схему еовпадепия едппичпых сигналов.

11сточник нанряжопгя --И и резисто) образуют токовый сток, обсчнечиваю1ций в точке В ток /2. Основная часть этого тока протекает через ДМЗ или Дл в зависимости от комбипацип входных сигналов. Через диод Д; на базу ДНЗ нодается положптельный тактовый импульс, производящий рассасывание пакопленного заряда и запирающий ДНЗ. Р1сточник напряжения-Е-, резистор R и туннельный диод ТД образуют бистабильпый триггер. Обращенный диод ОД подключает точку С к «земле при протекании через ДНЗ прямого тока, что позволяет поставпть диод Д|, представляющий обратную реакцию на ДНЗ со стороны триггера.

В качестве диода Д) примепяется кремпиевый диод, имеющий сравпительно больп1ую протяженность начального участка вольтамперной характеристики и не шуптнрующий выход триггера, иаходяп1егося в высоковольтном состоянии.

В начале каждого такта триггер сбрасывается в нулевое (высоковольтное) состояние отрицательным импульсом через резистор R. Если в течеппе первого полутакта на входы /-3 приходит хотя бы один едииичный сигнал (низкий уровень), то соответствующий входной диод открыт и в точке А оказывается нанряжепие низкого уровня. Носледнее должно быть таким, чтобы диод Д, был закрыт. Для этого входные сигналы сменяются

на необходимую величину с помощью источника напряжепия - E (катоды ТД схем КЧРО подсоедиияются не па «земле а на источник - .(.

В течение первой половины такта при закрытом диоде Дз ток /2 протекает через ОД п ДНЗ. В базе последнего происходит накоплепие заряда неравновесных носителей. Нриходяпдий через полтакта положительпый импульс «Уста}ювки, рассасывая пакоплепный заряд, вызывает протекание обратного 1ока /обр через ДНЗ и Д на триггер, нроизводя его переключение в единичное (низковольтное) состояние. В этом положении триггер находится в течение второго нолутакта и перекл очается в «нуль очередпым нмпульсом сброса.

В течение всего времени протекания тока /ойр в точке С cyntecTBycT положительное напряжение и, следовательно, ОД закрыт. Так как нослед П1Й работает на основщ ьх носитеЛ5ГХ, то время переключепия eio, определяемое зарядом барьерной емкости, на один - два порядка времени рассасывания заряда в базе ДНЗ. Нрактически весь ток /,,Г)р протекает через Д па триггер.

Если па входы /-3 поступают нулевые сигналы (высокпй уровень), диоды Д запираются и напряжение в точке А повьинается, приводя к отпиранию диода Дз. Осиовная часть тока /2 оттекает через диод Дз, отр цательпое папряжепие в точке В уменьпитетея настолько, что рабочая точка ДНЗ оказывается в области характеристики с малой ироводимостыо. Заряд в базе ДНЗ практически не накапливается. Нрищсдший через 1Юлтакта положительпый импульс установки вызывает протекание через ДНЗ только небольщого обратного тока, обусловленного зарядом барьерной емкости перехода и недостаточного для переключения триггера в едипичное еостояпне.

Аналогично работает схема NIPO, приведенная на фиг. 2.

Н р е д м е т и з о б р е т е н и я

Догическая схема «НЛИ- Н, содержащая диод е накоплением заряда, один вывод кото)ого соединен с выходом «-входовой диодной схемы «НЛН п через диод - с источником синхронизирующих имиульсов, а другой вывод соединен со входом - выходом триггера на туннельном диоде, отличающаяся тем, что,

с целью расщирения функциональных возможностей и повыщения иадежпости, она дополнительно еодержит разделительный диод, включенный между диодом с накоплением зар)яда и тупнельпым диодом, и обращенный

диод, иодключе1тый между точкой соединения разделительного диода с диодом с наконлением заряда и общей щиной питания,

Сброс PINO

Ус/п N/PO Риг J

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| ВСЕСОЮЗНАЯ ПАТГ..,.Ч?СКАЙбиблиотека wsBAВ. Е. Мельник | 1972 |

|

SU336812A1 |

| Логический элемент | 1974 |

|

SU572930A2 |

| Управляемый триггер | 1974 |

|

SU541290A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| Однотактный регистр сдвига | 1972 |

|

SU447761A1 |

| Счетный триггер | 1973 |

|

SU455492A1 |

| ФОРМИРОВАТЕЛЬ СУБНАНОСЕКУНДНЫХ ИМПУЛЬСОВ | 2024 |

|

RU2822823C1 |

Даты

1971-01-01—Публикация