1

Изобретение относится к вычислительно технике и автоматике и может использоваться при иостроеиии блоков управления дискретных устройств.

Известен распределитель сигналов, содержаидий основной и всномогательный регистры, в котором выходы «1 триггеров основного регистра соединены с выходами распределителя, управляющие входы триггеров этого регистра присоединены к входу «Запись в основной регистр, ипформациоиные входы триггеров вспомогательного регистра присоединены к соответствующим щинам входа «Код распределителя.

Известный расиределитель сигиалов не обеснечивает возможность смещения «Ь при подаче сигнала сдвига на любое заданное количество позиций в соответствии с информацией (ирограммой), поступающей извне, и сложен при настройке.

Целью изобретения является упрощеиие пастройки распределителя сигналов.

Это достигается тем, что в распределитель введены схема фиксации пос.чедией единицы, входы которой соединены с выходами «Ь триггеров всиомогательпого регистра, схема задержки, подключенная к выходу схемы фиксации последней единицы, схема «НЕ, первая схема «И, первый вход KOTOpoii соединен с выходом схемы задержки и входом схемы

«НЕ, второй вход - с входом «Запись в вспо.могател ньп 1 регистр распределителя, а выход присоединен к унравляющим входам триггеров вспомогательного регистра, вторая схема «И, первьи вход KOTOpoii связей с выходом схемы «НЕ, второй вход - с вторым входом первой схемы «И, группа разрядных схем «ГЬ. выход каждой из которых соедипен с входом установки в «О соответствующего триггера вспомогательного регистра, первый вход соедииеп с выходом второй схемы «И, а BTOpoii вход - с выходо.м «1 соответствующего триггера оеповпого регистра, соединенные последовательно в кольцо разрядные логические узлы, каждый из которых содержит схему «МЛИ и две схемы «И, причем первый вход каждой схемы «ИЛИ соединен е соответствующей тиной входа «Начальная установка расн)еделителя, второй вход - с выходом нервой схемы «И логического уз.та предществующего разряда, а выход - с первыми входами первой и второй схем «И дапиого логического узла, второй вход первой схе.мы «li каждого логического узла соедипен с выходом «О триггера еоответствующего разряда .могагельного регистра, второй вход BTOpoi : схемы «Pi каждого логического узла соединен с выходом «1 триггера соответствующего разряда вспомогательного региетра, выход BTOpoii схемы «И каждого логического узла соединен с информационным входом соответствующего триггера основного регистра.

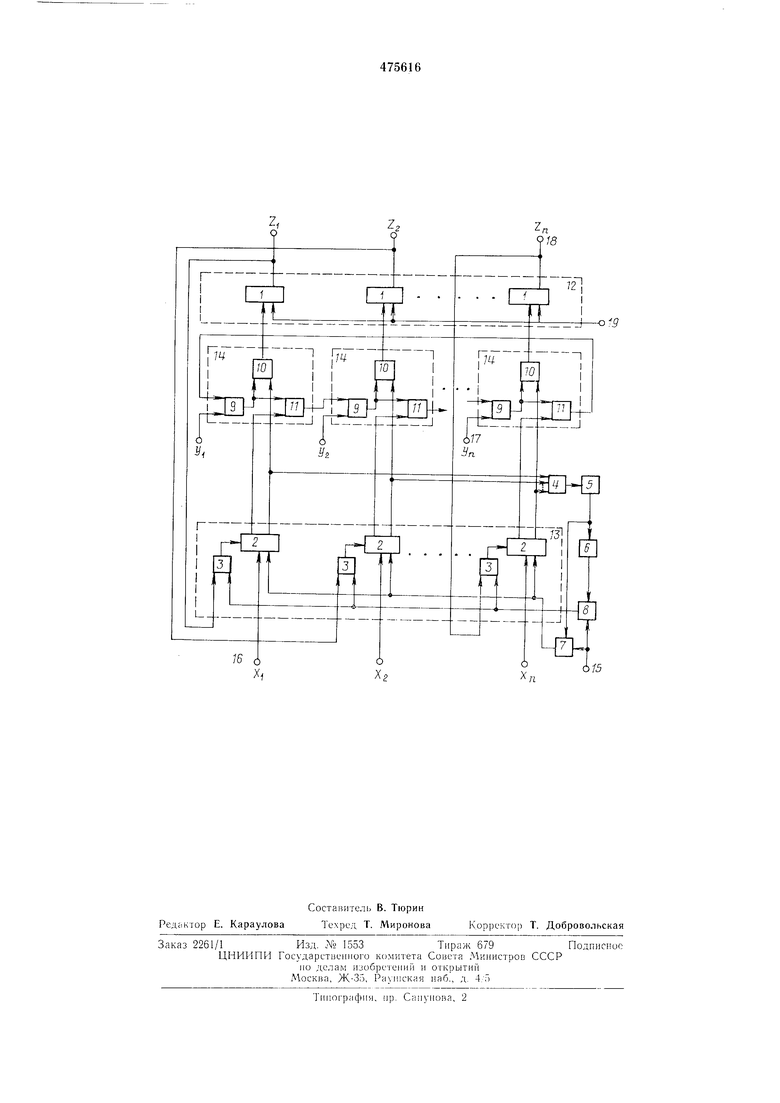

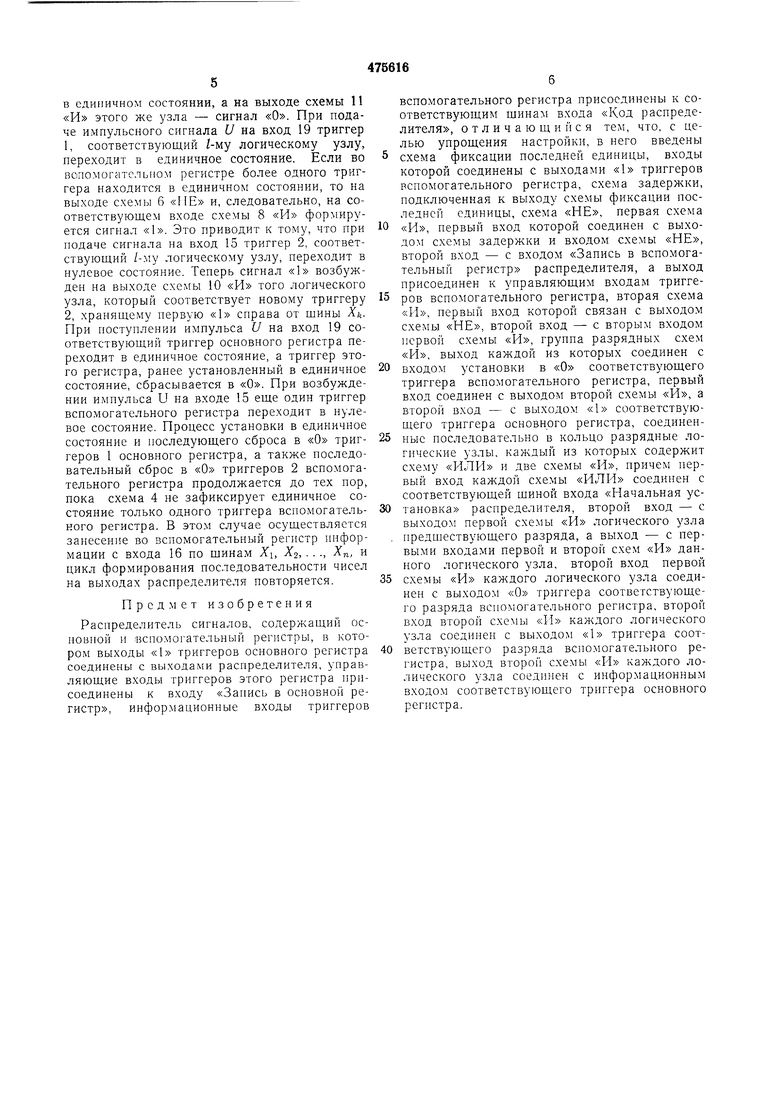

Па чертеже приведена схема предлагаемого распределителя сигналов, где 1 - триггер основного регистра, 2 - триггер вспомогательного регистра, 3 - схема «И из группы установки в «О триггеров вспомогательного регистра, 4 - схема фиксации последней единицы, 5 - схема задержки, 6 - схема «НЕ, 7 и 8 - схемы «И, 9 - схема «ИЛИ, 10 и 11 - схемы «И, 12 - основной регистр, 13 - вспомогательный регистр, 14 - логический узел, 15 - вход распределителя «Запись в вспомогательный регистр, 16 - вход распределителя «Код, 17 - вход распределителя «Начальная установка, 18 - выходные шины распределителя, 19 - вход распределителя «Запись в основной регистр.

Распределитель содержит основной регистр

12,построенный на и триггерах 1, прямые выходы которых связаны с выходами Zi, Zj,.. ., Zn распределителя, вспомогательный регистр

13,образоваинып триггерами 2, к входам установки в «и которых подсоединены схемы 3 «И, иоразрядпые логические узлы 14, логическую схему 4 фиксации последней единицы, схему задержки о, схему 6 «ИБ и схемы 7, 8 «И. В каждый логический узел 14 входит схема 9 «И /11г1 и схемы 10, И «И. Занесение инфор.мации в триггеры 1 и 2 осуществляется парафазно, причем информационные входы триггеров 2 связаны с внешними полюсами AI, А2, . . ., А„ распределителя, а управляющие входы триггеров 1 подключены к входу 19, через который поступают импульсные сигналы занесения информации в основной регистр. Выход схемы lU «И каждого логического узла подсоедипен к информационному входу соответствующего триггера 1, а выход схе.чы 11 «И - к одному из входов схемы 9 «ИЛИ еледующего логического узла (с учетом циклической связи крайних правого и левого разрядов распределителя). Вторые входы схем 9 «ИЛИ логических узлов подключены к входу 17 раснределит-еля 1 ь У2, - -, in. Одип из входов схе.м 10, И «И подключен к выходу схемы 9 «ИЛИ. Другой вход схемы 10 связан с нрямым выходом соответствующего триггера 2, а другой вход схемы И «И - с инверсным выходом этого же триггера. Ирямые выходы триггеров 2 подсоединены также к входа.м схемы 4 фиксации последней единицы, к выходу которой подключена схема задержки 5.

На один из входов схемы 7 «И ноступает сигнал с выхода схемы задержки 5; на один из входов схемы 8 «И этот же сигнал поступает через схему 6 «НЕ. Вторые входы схем 7 и 8 подключены к входу 15 раснределителя, через который поступают импульсные сигналы и, обеспечивающие изменение состояний вспомогательного регистра. Занесение информации извне в этот регистр осуществляется за счет подачи импульсного сигнала с выхода

с.хемы 7 «И па управляющие входы триггеров 2. Выход схемы 8 «И подключен к одному из входов схем 3 «И. Другой вход каждой схемы 3 «И связан с прямым выходом соответствующего триггера 1.

Распределитель сигналов обеспечивает формирование на выходах 18 Z, Za, . . ., Z последовательностей чисел в коде «1 из Л, причем в формируемых последовательностях «1 сме1цается на о;1рсдс 1еп1юе количество позиций вправо при подаче управляющего сигнала U (с учетом циклической связи крайних правого и левого разрядов распределителя) по входу 19. Закон олептенпя «1 задается с помо цыо слова в алфавите (О, 1) поданного на вход 16 Ji, 2, . ., п. При работе распределителя сигналы «1 возбуждаются только на тех его выходах, которые соответствуют входам из множества {Х, Х, . . ., Хп}, фиксирующим «1. На вход 17 У;, Y2, . . ., Yn поступает число в коде «1 из N, задающее начальное состояние распределителя.

Схема фиксации последпей едипицы, входящая в состав распределителя, реализует логическую операцию «Исключающее ИЛИ (1 и только 1). Например, для пятиразрядного двоичного кода (Х, з, Xz, Xi, JQ) эта схема реализуется в соответствии с логическим выражением

..-.„

/:- .f Х Х Х j Х Аз Х Xj Хд /

V Х Xj Х V X Х .л J Xi Х„ /

/ Х Х .л2 ,.

Конкретная реализация выражений, аналогичных приведеиному, определяется параметрами иснользуе.мой базовой системы логических эле.ментов.

Раснределитель сигналов работает следующим образом.

Перед начало.м работы все триггеры 2, кро.ме одного (любого), и все триггеры 1 устанавливаются в нулевое состояние (на функциональной схеме цепи начальной установки опущены). В результате этого на выходе схемы 4 фиксации последней единицы и, следовательно, па соответствующем входе схемы 7 «И формируется сигнал «1. При подаче импульса и на вход 15 возбуждается выход схемы 7, и нроизводится занесение информации, зафиксированной на щинах Xi, Х, . . ., Хп входа 16, в триггеры вспомогательного регистра. На щины УЬ YZ, . . ., УП входа 17 подапо чис.ю в коде «1 из Л. Предположим, что сигпал «1 возбужден на щине УА. Тогда на выходе схемы 9 «ИЛИ k-ro логического узла будет выработан сигнал «1, который распространяется до /-ГО логического узла, соответствующего щине Xi, на которой возбуждена первая «1 справа от шины Х/, (с учетом циклическо связи крайних разрядов). В частном случае / /е. На выходе схемы 10 «И 1-го логического узла формируется сигнал «1, носкольку соответствующий триггер 2 находится

в единичном состоянии, а на выходе схемы И «И этого же узла - сигнал «О. При подаче импульсного сигнала U на вход 19 триггер

1,соответствующий /-му логическому узлу, переходит в единичное состояние. Если во вспомогательном регистре более одного триггера находится в единичном состоянии, то на выходе схемы 6 «ilE и, следовательно, на соответствующем входе схемы 8 «И формируется сигнал «1. Это приводит к тому, что при подаче сигнала на вход 15 триггер 2, соответствующий /-МУ логическому узлу, переходит в нулевое состояние. Теперь сигнал «1 возбужден на выходе схемы 10 «И того логического узла, который соответствует новому триггеру

2,хранящему первую «1 справа от шины ft. При поступлении импульса U на вход 19 соответствующий триггер основного регистра переходит в единичное состояние, а триггер этого регистра, ранее установленный в единичное состояние, сбрасывается в «О. При возбуждении импульса и на входе 15 еще один триггер вспомогательного регистра переходит в нулевое состояние. Процесс установки в единичное состояние и последующего сброса в «О триггеров 1 основного регистра, а также последовательный сброс в «О триггеров 2 вспомогательного регистра продолжается до тех пор, пока схема 4 не зафиксирует единичное состояние только одного триггера вспомогательного регистра. В этом случае осуществляется занесение во вспомогательный регистр информации с входа 16 по щинам Xi, Х, . . ., Хп, и цикл формирования последовательности чисел па выходах распределителя повторяется.

Предмет изобретения

Распределитель сигналов, содержащий основной п вспомогательный регистры, в котором выходы «1 триггеров основного регистра соединены с выходами распределителя, управляющие входы триггеров этого регистра присоединены к входу «Запись в основной регистр, информационные входы триггеров

вспомогательного регистра присоединены к соответствующим щинам входа «Код распределителя, отличающийся тем, что, с целью упрощения настройки, в него введены схема фиксации последней единицы, входы которой соединены с выходами «1 триггеров вспомогательного регистра, схема задержки, подключенная к выходу схемы фиксации последней единицы, схема «НЕ, первая схема

«И, первый вход которой соединен с выходом схемы задержки и входом схемы «НЕ, второй вход - с входом «Запись в вспомогательный регистр распределителя, а выход присоединен к управляющим входам триггеров вспомогательного регистра, вторая схема «И, первый вход которой связан с выходом схемы «НЕ, второй вход - с вторым входом первой схемы «П, группа разрядных схем «И, выход каждой из которых соединен с

входом установки в «О соответствующего триггера вспомогательного регистра, первый вход соединен с выходом второй схемы «И, а второй вход - с выходом «1 соответствующего триггера основного регистра, соединенныс последовательно в кольцо разрядные логические узлы, каждый из которых содержит схему «ИЛИ и две схемы «П, причем первый вход каждой схемы «ИЛИ соединен с соответствующей шиной входа «Начальная установка распределителя, второй вход - с выходом первой схемы «И логического узла предшествующего разряда, а выход - с первыми входами цервой и второй схем «И данного логического узла, второй вход первой

схемы «И каждого логического узла соединен с выходом «О триггера соответствующего разряда вспомогательного регистра, второй вход второй схемы «И каждого логического узла соединен с выходом «1 триггера соответствующего разряда вспомогательного регистра, выход второй схемы «П каждого лолического узла соединен с информационным входом соответствующего триггера основного регистра.

Z, о

п 918

Т2

П v

74

У

IDJ П

о

y

у.

Г

П

/Ц

70

//TU

t

.

6/7

п

6/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Двоичный счетчик | 1961 |

|

SU148595A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Устройство для контроля мультиплексоров | 1987 |

|

SU1511749A1 |

| Пороговый логический элемент | 1975 |

|

SU559393A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

Авторы

Даты

1975-06-30—Публикация

1973-03-05—Подача