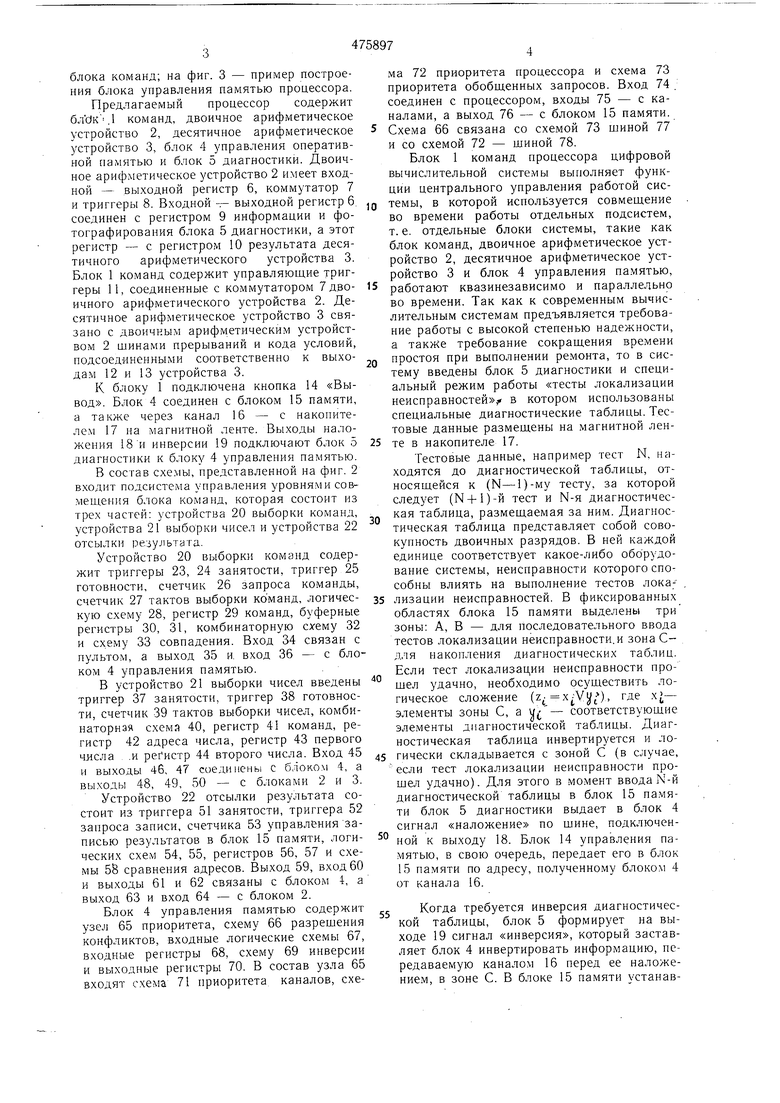

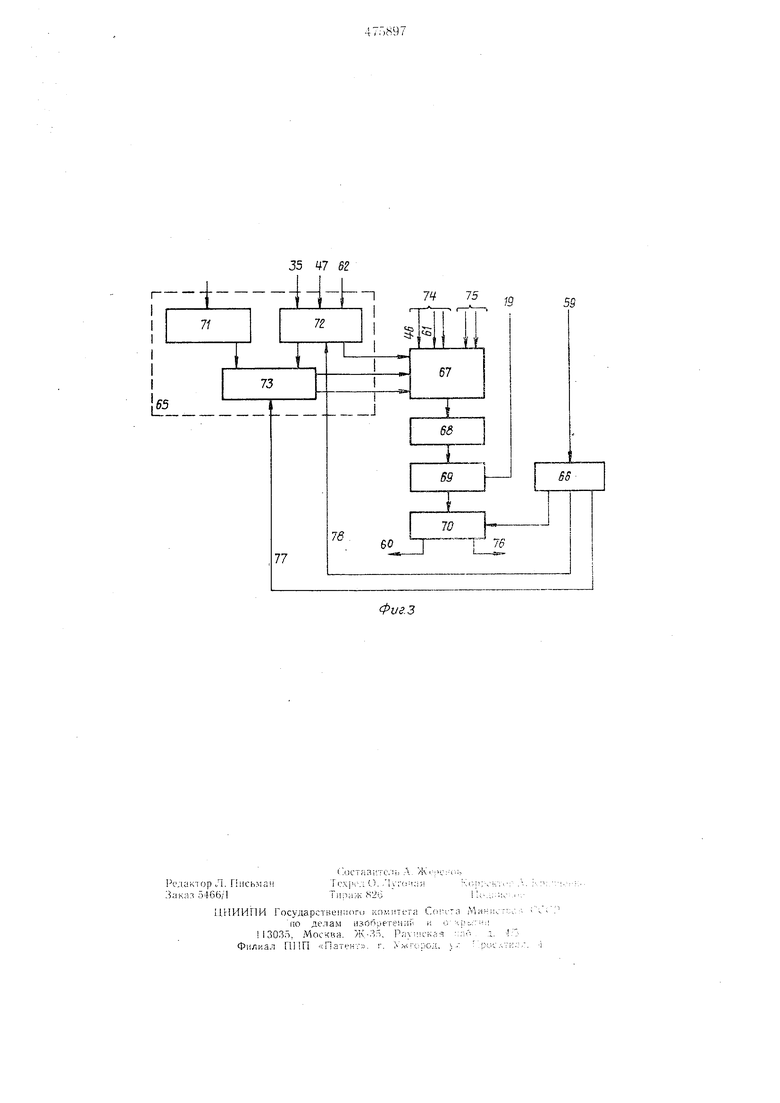

Изобретение относится к цифровой вычислительной технике, в частности к структурам центральных процессоров вычислительной системы, содержащей набор квазинезависимых блоков, работающих с совмещением во Бремени, включая встроенный блок диагностики. Известны процессоры цифровых вычислительны). систем, содержащие квазинезависимые блоки, такие как блок команд, блок управления памятью, подключенный к блоку памяти и включающий в себя входные и выходные регистры, пульт управления. Однако такие процессоры вычислительных систем имеют недостаточно высокое быстродействие, их диагностическая аппаратура сложна, что вызвано ее автономностью и универсальностью, и, кроме того, в них не испо.ьзуется оборудование местных -блоков управления, имеющихся в различных подсистемах системы, для диагностики процессора. Разделение функций контроля и диагностики процессора между отдельными подсистемами путем использования оборудования местных блоков управления этих подсистем является существенно новым и принципиально отличает данный процессор от известных. Цель изобретения - сокращение оборудования и повышение быстродействия процессора. Это достигается тем, что в процессоре выход наложения и выход инверсии блока диагностики соединены с третьим и четвертым входами блока управления памятью, информационный выход блока диагностики подключен к четвертому входу двоичного арифметического устройства, а пятый и щестой входы двоичного арифметического устройства - соответственно к выходу прерываний и выходу кода условий десятичного арифметического устройства, выход результата которого соединен с входом блока диагностики. Второй выход двоичного арифметического устройства подключен к первому входу блока команд, второй вход которого связан с вторым входом процессора. На фиг. 1 представлена блок-схема процессора цифровой вычислительной системы; на фиг. 2 приведен пример построения нодсистемы управления уровнями совмещения блока команд; на фиг. 3 - пример построения блока управления памятью процессора. Предлагаемый процессор содержит блУк-,1 команд, двоичное арифметическое устройство 2, десятичное арифметическое устройство 3, блок 4 управления оперативной памятью и блок 5 диагностики. Двоичное арифметическое устройство 2 имеет входной - выходной регистр 6, коммутатор 7 и триггеры 8. Входной-7-выходной регистр 6. соединен с регистром 9 информации и фотографирования блока 5 диагностики, а этот регистр - с регистро.м 10 результата десятичного арифметического устройства 3. Блок 1 команд содержит управляющие триггеры 11, соединенные С коммутатором 7 двоичного арифметического устройства 2. Десятичное арифметическое устройство 3 связано с двоичным арифметическим устройством 2 щинами прерываний и кода условий, подсоединенными соответственно к выходам 12 и 13 устройства 3. К блоку 1 подключена кнопка 14 «Вывод. Блок 4 соединен с блоком 15 памяти, а также через канал 16 - с накопителем 17 на магнитной ленте. Выходы наложения 18 и инверсии 19 подключают блок 5 диагностики к блоку 4 управления памятью. В состав схемы, представленной на фиг. 2 входит подсистема управления уровня.ми совмещения блока команд, которая состоит из трех частей: устройства 20 выборки команд, устройства 21 выборки чисел и устройства 22 отсылки результата. Устройство 20 выборки команд содержит триггеры 23, 24 занятости, триггер 25 готовности, счетчик 26 запроса команды. счетчик 27 тактов выборки команд, логическую схему 28, регистр 29 команд, буферные регистры 30, 31, комбинаторную схему 32 и схему 33 совпадения. Вход 34 связан с пультом, а выход 35 и. вход 36 - с блоком 4 управления памятью. В устр ойство 21 выборки чисел введены триггер 37 занятости, триггер 38 готовности, счетчик 39 тактов выборки чисел, комбинаторная схема 40, регистр 41 команд, регистр 42 адреса числа, регистр 43 первого числа .и регистр 44 второго числа. Вход 45 и выходы 4б, 47 соединены с блоком 4, а выходы 48, 49, 50 - с блоками 2 и 3. Устройство 22 отсылки результата состоит из триггера 51 занятости, триггера 52 запроса записи, счетчика 53 управления записью результатов в блок 15 па.мяти, логических схем 54, 55, регистров 56, 57 и схемы 58 сравнения адресов. Выход 59, вход 60 и выходы 61 и 62 связаны с блоком 4, а выход 63 и вход 64 - с блоком 2. Блок 4 управления памятью содержит узел 65 приоритета, схему 66 разрещения конфликтов, входные логические схемы 67, входные регистры 68, схему 69 инверсии и выходные регистры 70. В состав узла 65 входят схема 71 приоритета каналов, схема 72 приоритета процессора и схема 73 приоритета обобщенных запросов. Вход 74 . соединен с процессором, входы 75 - с каналами, а выход 76 - с блоком 15 памяти. Схема 66 связана со схемой 73 шиной 77 и со схемой 72 - шиной 78. Блок 1 команд процессора цифровой вычислительной системы выполняет функции центрального управления работой системы, в которой используется совмещение во времени работы отдельных подсистем, т. е. отдельные блоки системы, такие как блок команд, двоичное арифметическое устройство 2, десятичное арифметическое устройство 3 и блок 4 управления памятью. работают квазинезависимо и параллельно во времени. Так как к современным вычислительным системам предъявляется требование работы с высокой степенью надежности, а также требование сокращения времени простоя при выполнении ремонта, то в систему введены блок 5 диагностики и специальный режим работы «тесты локализации неисправностей,г в котором использованы специальные диагностические таблицы. Тестовые данные размещены на магнитной ленте в накопителе 17. Тестовые данные, например тест N, находятся до диагностической таблицы, относящейся к (N-1)-му тесту, за которой следует (Ы + 1)-й тест и N-я диагностическая таблица, размещаемая за ним. Диагностическая таблица представляет собой совокупность двоичных разрядов. В ней каждой единице соответствует какое-либо оборудование системы, неисправности которого способны влиять на выполнение тестов локализации неисправностей. В фиксированных областях блока 15 памяти выделены три зоны: А, В - для последовательного ввода тестов локализации неисправности.и зона Сдля накопления диагностических таблиц. Если тест локализации неисправности прошел удачно, необходимо осуществить гическое сложение (z ), где элементы зоны С, а и/ - соответствующие элементы диагностической таблицы. Диагностическая таблица инвертируется и лорически складывается с зоной С (в случае, если тест локализации неисправности прощел удачно). Для этого в момент ввода N-й диагностической таблицы в блок 15 па.мяти блок 5 диагностики выдает в блок 4 сигнал «наложение по щине, подключенНОЙ к выходу 18. Блок 14 управления памятью, в свою очередь, передает его в блок 15 памяти по адресу, полученному блоком 4 от канала 16. Когда требуется инверсия диагностической таблицы, блок 5 формирует на выходе 19 сигнал «инверсия, который заставляет блок 4 инвертировать информацию, передаваемую каналом 16 перед ее наложением, в зоне С. В блоке 15 памяти устанавливается специальный режим записи, позволяющий логически суммировать старое содержимое ячейки с записываемой вновь информацией и фиксировать новый результат в этой же ячейке. После этой операции первоначально очищенная зона С заполняется единицами. Подозреваемым неисправностям соответствуют нулевые разряды в зоне В.

В системе предусматривается возможность аппаратного выведения содержимого зоны С на внещний носитель (перфокарты, электроннолучевые трубки и т. д.). Кнопка 14 «Вывод, выполняющая эту функцию, непосредственно подключена к блоку 1, причем нажатие на кнопку имитирует инструкцию процессора «начать ввод/вывод. Адрес канала и устройство ввода/вывода (не показано на фиг. 1) задаются в этом случае от переключателей пульта, используемых при первоначальной загрузке программ.

Адресное слово канала хранится.в 72-й ячейке, и соответствующая канальная программа вывода заранее вводится в блок 15 памяти (по сигналу «первоначальная загрузка программы) одновременно с канальной программой загрузки тестов локализации неисправностей и диагностических таблиц.

Операцию логического сложения диагностических таблиц можно заменить на операцию логического умножения. В этом случае, если N-й тест локализации неисправностей не прощел, то соответствующие разряды диагностической таблицы должны логически умножаться на содержимое соответствующей ячейки зоны С. Если N-й тест локализации неисправности прошел, то проводится логическое умножение инверсии соответствующего разряда диагностической таблицы на содержимое соответствующей ячейки в зоне С. Предварительно зона С заполняется единицами. В результате этого подозреваемым неисправностям в зоне С соответствуют единичные разряды в соответствующих позициях. Операцию инверсии нецелесообразно проводить в блоке оперативной памяти, так как иначе пришлось бы вводить оборудование, осуществляющее инверсию, в каждый блок оперативной памяти в.место одного блока управления памятью. Логическое сложение или умножение можно, но нецелесообразно, перенести в блок управления памятью, так как при записи необходимо старую считанную информацию передать в блок управлен-ия па.мятью, провести в нем логическую операцию, а результат вновь направить в оперативную память.

Когда неисправность имеет неустойчивый характер, то .удачно выполненные тесты локализации неисправности несут мало полезной информации, так как в момент выполнения теста данная неисправность может отсутствовать. В общем случае в блоке 15

памяти выделяется зона С для устойчивых неисправностей и зона С. Если тест локализации неисправности выполнен неправильно, то инвертированные диагностические таб- лицы накапливаются (суммируются логически) в зоне С, а если правильно, то неинвертированные диагностические таблицы накапливаются в зоне С

При неустойчивых неисправностях в основном используется только зона С (С - как вспомогательная информация по усмотрению оператора). Для устойчивых неисправностей необходимо находить дополнительное пересечение зон С и С. Это делают либо визуально, либо путем вывода содержимого зоны С на перфокарты и репродукцией на эти перфокарты содержимого зоны С . Пульт оператора может содержать переключатель управления выводом этих зон. Для ввода в зону С и Св блоке диагностики предусмотрена специальная схема коррекции канальной программы в зависимости от удачного или неудачного прохождения теста локализации неисправности. (Схема коррекции на фиг. 1 не показана).

Предпочтительным вариантом выполнения диагностических тестов в предлагае-мой системе является вариант с использованием специального режима записи с наложением в блоке управления памятью.

Пересылками информации в процессоре и выполнение.м програ.ммы в систе.ме управляет блок команд (фиг. 1). который содержит систему управления уровнями совмещения (фиг. 2). В системе управления уровнями совмещения работой-устройств 20-22 управляют счетчик 26 запроса команды. , счетчик 27 тактов выборки команд, счетчик 39 тактов выборки чисел и счетчик 53 управления записью результатов в память. При подаче с пульта сигнала «Пуск на вход 34 пли от сигнала, поступающего со счетчика 39 на логическую схему 28. запускается счетчик 26, формирующий на выходе 35 запрос иа командх в блок 4. Счетчик 27. запускаемый сигналом со схемы 39, готовит в регистре 29 команд очередную команду. Информация для очередной команды nocTyiiaет в буферные регистры 30 и 31 с входа 36 из блока 4. Сигнал сопровождения команды, поступающий одновременно с пнфор.мацией с входа 36, устанавливает в «1 триггеры 23 и 24 занятости соответственно заполняемому регистру. С помощью комбинаторной схемы 32 происходят выборка соответствующих частей команды из буферных регистров 30 и 31 и помещение этих частей в регистр 29 команд. Триггер 25 готовности устанавливается в «О в начале работы счетчика 27 и в «1 - по оконча НИИ работы этого счетчика. Это достигается благодаря схеме 33 совпадения, которая учитывает наличие информации в регистрах 30 и 31 соответственно. Триггеры 23 и 24 обеспечивают включение счетчика 26

запроса команды в тех случаях, когда информация из регистра 31 полностью передана в регистр 29 команд.

Следующий уровень совмещения запускается при наличии в триггере 25 единицы, что указывает на готовность устройства 20 выборки команд, и нуля в триггере 37 занятости, что указывает на незанятость устройства 21 выборки чисел. При этом начинает работать счетчик 39, запускае.мый через комбинаторную схему 40, в результате чего прини.мается очередная ко.манда в регистр: 41 и формируется адрес числа в регистре 42. Адрес числа с выхода 46 и запрос числа с выхода 47 передается в блок 4. Числа, подлежащие обработке, фор.мируются в регистре 43 первого числа и в регистре 44 второго числа, поступая в эти регистры из блока памяти.

Триггер 37 устапавливается в «1 в момент начала счета в счетчике 39«и сбрасывается в «О сигналом сопровождения, поcтvнaк)( по в.ходу 45. Тр,иггер 38 готовности устанавливается в «1 сигналом, поступающим по входу 45,1 сбрасывается в «О в начале работы следующего уровня сигналом, поступающим по выходу 63. Уровень отсылки результата начинает работать при условии, что триггер 38 находится в «1 и при наличии «О в триггере 51 занятости уровня, что обеспечивается логической схемой 55. Этот ровень принимает адрес отсылки результата в регнст|1 56 из регистра 42 и команду в регистр 57 из регистра 41.

rioii пь полнении первого такта счетч ка 53 фо|)п1р етси ciiiiia.T начала операции На выходе 63 и осуществляется передача чисел по выходам 48 , 49 и ко.манды по выходу 50 в блоке 2 и 3.

Дальнейшая работа устройства 22 начинается с четвертого такта счетчика 53 либо по сигналу «конеп работы арифметического устройства, поступающему по входу 64 в том случае, когда нет записи в память, либо по сигналу «результат записан, проходящему по входу 60 из блока 4, если имела место запись в память, что обеспечивается логической схе.мой 54 на входе четвертого разряда счетчика 53. Запрос на запись в блок 4 подается -с выхода 62 от триггера 52 запроса записи, а адрес записи - с выхода 61 в блок 4.

Триггер 51 занятости устанавливается в «1 при нача.те счета в счетчике 53 и сбрасывается в конце работы этого счетчика.

Для разрен епия конфликтных ситуаций, .возникающих при совпадении адреса отсылки результата с адресом числа, для регистров 42, 56 предусмотрена схема 58 сравнения адресов. При совпадении адресов в этих регистрах схема 58 вырабатывает сигнал отмены запроса числа, поступаюаи1Й в блок 4 с выхода 59. Конфликтные снтуации не нсчерпываются о1П;санной, но для

анализа и разрещения других конфликтных ситуаций не требуется отмена запроса.

Команда «Вывод с пульта (от кнопки) реализуется путем засылки в регистр 56 инфор.мации с пульта и принудительного исполнения инструкции вывода информации из канала.

Блок команд обращается в блок 15 памяти для Чтения команд и операндов и записи результатов выполнения операции. Так как запросы на обращение в память .могут возникнуть в различных блоках одновременно, то их обработку необходимо осуществлять в приоритетном порядке. Запросы от каналов 16 подаются на схему 71

приоритета каналов, а запросы от блока 1 - на схему 72 приоритета процессора. Управление узлом 65 осуществляется сигналами сброса по щине 77 и сигналами блокировки по щине 78, поступающими со схемы 66 разрещения конфликтов на схему 73 приоритета обобщенных запросов и схему 72 приоритета процессора соответственно. Выходные сигналы узла 65 управляют работой входных логических схем 67, на которые проходят входные данные от процессора по

5 входу 74 и входные данные от каналов по входам 75.

Узел 65 разносит по времени выполнение этих запросов в блоке 4. На входные регистры блока 4 принимаются входные данные от того абонента процессора, который в данный момент получил .приоритет. Схема 66 разрещения конфликтов выделяет код номера устройства блока памяти, к которому в данный момент проводится обращение, и анализирует состояние этого устройства. При занятости устройства блока памяти его номер запоминается в схеме 66, а в узел 65 посылаются сигналы сброса схемы 73 и блокировки схемы 72, которые вызывают начало просмотра запросов каналов. Как только устройство блока памяти, в которое обращался данный блок процессора, освобождается, схема 66 посылает в узел 65 сигнал, который в случае отсутствия запросов от каналов вновь устанавливает приоритет проц ессора. Если дан- ный абонент процессора обращается в свободное устройство блока памяти, то это устройство запускается, и в соответствующий абонент процессора посылается сигнал «Ответ. По этому сигналу абонент процессора формирует следующий запрос в блок памяти.

При обнаружении конфликта Между обращениями от различных блоков процессора вырабатываются сигналы отмены запроса в блок памяти, который поступает на схему 66 разрещения конфликтов блока 4. В случае наличия этого сигнала сбрасывается соответствующий запрос в узле 65 и если этот запрос уже начал обрабатываться, его обработка прекращается, а узел 65 приоритета переходит к просмотру следующих запросов. При этом сигнал «Ответ COOTIKMствующему абоненту по входу 60 от выходного регистра 70 не выдается.

Инверсия информации осуществлясчея в схеме 69. При подаче этой инверсии с входных регистров 68 блока 4 па его выхо,1.яыс регистры 70 и наличии соответствующего сигнала на выходе 19 блока 5 диа1-| истпки. Информация, записанная во входном регистре 68, инвертируется схемой 69 и переписывается в выходные регистры 70 связанные с блоком памяти по выхо;и 76.

Выход 18 наложения транзито: пр1л одит через блок 4 управления памятью нз соответствующие вентили, осуществляющие управление регенерацией инфор.ации в блоке памяти. Эти вентили на фкг. 3 не показаны.

С пелыо сокращения чис.ча BXU,.UJB ;.; блоке 4 входной-выходной регисг; -i устройства 2 связан с регистрсмм 9. :j iiocледний, в свою очередь, - с выходным регистро.м 10 устройства 3. Это позволяет вместо трех входов по информации на блок 4 (от устройств 2 и 3 и блока 5) ммсть один - от устройства 2. Последоватсмьная пересылка результата из усгройства 3 п блока 5 ли.митирована по врелгени (десятичные опера 1ии и режи. диагп(:;стлк 1 с.габо влияют на производительность спстем,;. Кроме того, регистр 9 информации i-. cpOTi)графированяя используется д,1я ocDOca состояний основных регистров процессора iip; диагностике с последующей записью- в ф-иг,сированнуй зону памяти.

УпроЩ1ение стр -ктуры блока до.стгмяотся помещением в устройство 2 комАПтятора 7, управление которым осуцяеств,;яется от управляющих триггеров 11 блока 1 команд. Ко.ммутатор 7 организует перепись операндов так, чтобь( упрост ггь иос.ледующую обработку н запись результата в регистры общего назначения блока 1 (не показаны на фиг. 1). Применение комм г.атора позволяет повысить быстродействие .за счет совмещения приема и выставления операндов в трёбуемчЮ 3OHv вх()дного-вь ходного регистра f- без последующе -о уноря узчеПИЯ распо.южении икформацип н регистре. Д.чя того, чтобы лаксималько npocтить блок 1 выход 2 прерываний и выхо.:1 13 кода усло)зий (для операций фггрматя с заданием одного о:;ср.1;;да в команде и выборки другог; С11ер,.;;:да ил памяти, а также фс;рл;ата. в которол; оба о 1ераида размеП1;::о-:ся в блске i;5- па.1яти) ycTpoiicTBa 3 чере-з ре;т1стры и триггеры 8 стропства 2 соединены t: 6.;(JK(.)M i км а;-:д.

В цифровой з;,1чис.иг; мьной системе исгю.1ьзовано ирограм: ;ное 15ычисле1 не текущего В;)ел;ени. В ячейке б,ичча хранится 3 1;:-е1;;;е raiiMepa. Коррекгировка этиго зиаисиин осуи1еетвляется с иох1ои1ью счетчикоь таил,ера (не показан на чертежах) ii .Ь: «Таймер-;-, который В1ярабатывается 6.U) 1 и поступает в устройство 2, где ио .1 «Taihiep выполияется инст|)уки(я Быч тание с плавающей -;-; пятой.

1 роцессор ци1р;н К Й вычпс.1Ите:1Ы1ОЙ системе;, содержащий o.iOK диагности1 и. блок уиравлеиия памятью, соединещ ый е блоком Г1ал:ятп ч блоком команд, выход которого по.:,ключе1; ;-. первым входам деея-гичиого ап ;ф ч1и;-.-.; иo устройства i дво :чиого ари( иччЧ-чо ; - -стр01 ет15а. второй и третий Bxo,u,i )i:iporo соединены соответственно с iJ;Чlp: i i и третьим выходами б.кзка КОМУ..;. 1;егвь:й и второй входы блока ч1рав,енич runiSiiino подключены соот|;етот;кч1Ич к иемкпл входу процессора и ;С1: ВОл; БЫХОД .iBc. арифмепгческого хстройст а, oт. i u :цu i. тем, что, с целью сокраиеиия (;г:ич1я и иоььцнещ я быстродействие;, в 15ипчод на.тожепия н выход инверсии блока Д ;аг1остики соединены соответственно с трсп-ил н четвертым входами блока управ,:еи1 н иамяг|,ю, ин(|)ормационный вь:ход б, диагности1-;и по.тключек к чегйсотом входу )1чз apiujnieтического устройства, иятьп; и ineeToii, вхо ды KOTOi oi4j г одклкчц-иь соответствеино к выходх иресь:ся;И ; и иь ходх кода ус.ловий десятичного л;)иф :е; 1-:еско:ч1 устройства, (Д .ibTaTa ко;чч ; го сосд1п- ен с вход(;м блока диагностики, второ,й выход двоичиого ариазметическд-U .стройства иодк,-почеи к пегзо ;. блока команд, второй вход которого соединен со вторым входом nponeeeoj a.

l

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в блоках контроля процессора | 1980 |

|

SU903886A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955060A1 |

I

Авторы

Даты

1978-10-05—Публикация

1971-06-14—Подача