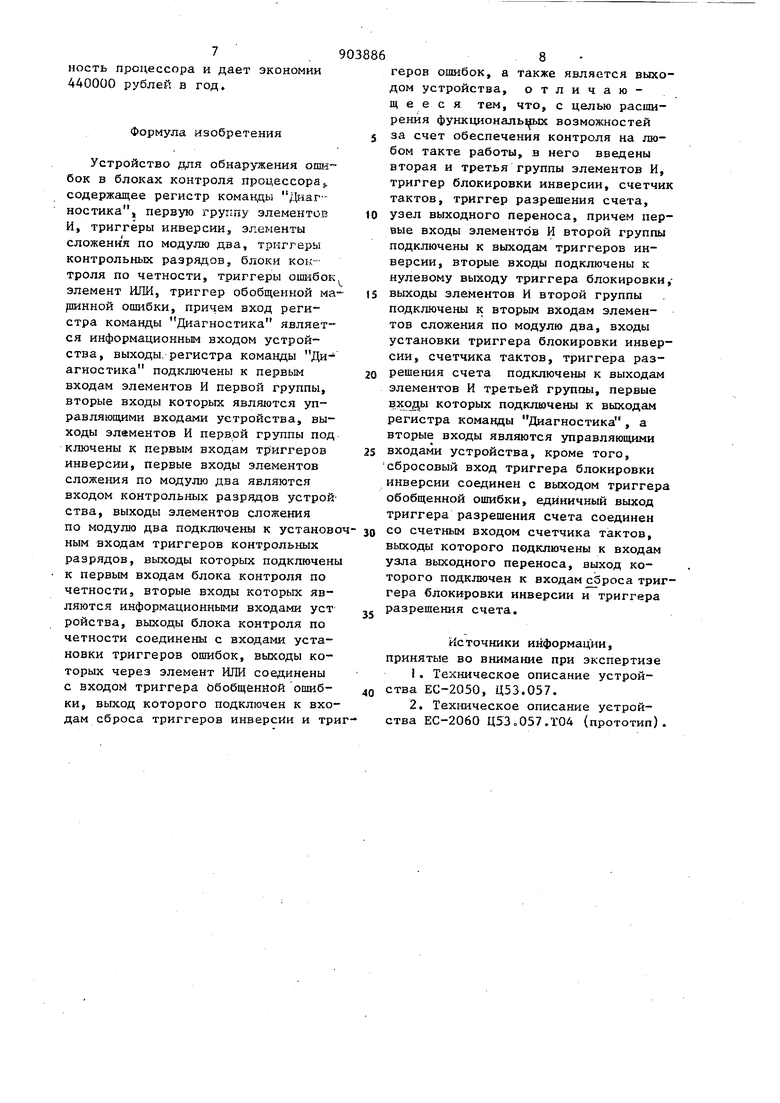

(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В БЛОКАХ КОНТРОЛЯ ПРОЦЕССОРА Изобретение относится к вычислительной технике и может быть исполь зовано в процессорах универсальных цифровых машин для обнаружения ошиб ки в блоках контроля по четности. Известно устройство контроля, содержащее ре;гистр команды Диагностика и триггеры, инвертирующие контрольные разряды на входах блоко контроля по четности в процессоре. Установка триггеров инверсии производится при выполнении команды Диагностика, содержащей .соответствующий код в управляющем слове О Недостатком устройства является то, что оно не обеспечивает достато ную надежность работы процессора, так как фиксирует только наличие ошибки и не регистрирует момент воз никновения ошибки. Наиболее близким по технической сущности к предлагаемому является устройство контроля, входящее в сос тав процессора ЕС2060. Это устройство содержит регистр команды Диагностика, первую группу элементов И, триггеры инверсии, элементы сложения по модулю два, триггеры контрольных разрядов, блоки контроля по четности, триггеры одшбок, элементы ИЛИ, обобщенный триггер машинной ошибки, причем входы регистра команды Диагностика соединены с шиной информации блока управления памятью (.УП), выходы регистра команды Диагностика соединены со вторыми входами первой группы элементов, первые входы которых соединены с шиной управления блока центрального управления (ЦУ), выходы первой группы элементов И соединены с входами установки триггеров инверсии, входы сброса которых соединены с триггером обобщенной машинной ошибки, выходы триггеров инверсии соединены с вторыми входами элементов по модулю два, первые входы которых соединены с ши39нами контрольных разрядов, выходы элементов по модулю два соединены с входами триггеров контрольных разрядов, выходы которых соединены с первыми входами блоков контроля по четности,.а вторые входы блоков контроля по четности соединены с информационными гайками блоков арифметического и центрального управления, выходы блоков контроля по четности соединены с вxoдa и установки триггеров ошибок блоков ЦУ и арифметического, выходы которых через элемент ИЛИ соединены с входами установки триггера обобщенной 11ашинной ошибки, соединенного с входами сброса триггеров oiiniбок и 1гиной прерывания по контролю Недостатком этого устройства кон троля является то, что устройство не обеспечивает достаточной надежности работы процессора, так как он проверяет работу блоков контроля процессора только в строго определе ные интервалы времени, а именно в течение первых шести тактов, работы процессора, непосредственно следующих за командой Диагностика, что не гарантирует надежную .работу процессора на остальных тактах его работы. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля на любом такт работы. , . . Эта цель достигается тем, что в устройство, содержащее регистр ком ды Диагностика первую группу эл ментов и, триггеры инверсии, элементы сложения по модулю два, триг геры контрольных разрядов, блоки контроля по четности, триггеры оши бок, элемент ИЛИ и триггер обобщен ной машинной ошибки, причем вход р гистра команды Диагностика является информационным входом устройства, выходы регистра команды Диагностика подключены к первым вхо дам элементов И первой группы вто рые входы которых, являются управля ющими входами устройства, выходы элементов И первой.группы подключе ны к первым входам триггеров инверсии, первые, входы элементов сло жения по модулго два являются входо контрольных разрядов.устройства, элементов сложения по модул два подключены к установочным входам триггеров контрольных разрядов, выходы которых подключены к первым входам блока контроля по четт нести, вторые входы которых являются информационными входами устройства, выходы блока контроля по четности соединены с входами установки триггеров ошибок, выходы которых через элемент ИЛИ соединены с входом триггера обобщенной ошибки, выход которого подключен к входам сброса триггеров инверсии и триггеров ошибок, а также является выходом устройства, введены вторая и третья группы элементов И, триггер блокировки инверсии, счетчик тактов, триггер разрешения счета, узел выходного переноса, причем первые входы элементов И второй группы подключены к вьЬсодам триггеров инверсии, вторые входы подключены к нулевому выходу триггера блокировки, выходы элементов И второй группы подключены к вторым входам элементов сложения по модулю два, входы установки триггера блокировки инверсии, счетчика тактов, триггера разрешения счета подключены к выходам элементов И третьей группы, первые входы которых подключены к выходам регистра команды Диагностика, а вторые входы являются управляющими входами устройства, кроме того, сбросовый вход триггера блокировки инверсии соединен с выходом триггера обобщенной ошибки, единичный выход триггера разрешения счета соединен со счетным входом счетчика тактов, выходы которого подключены к входам узла выходного переноса, выход которого подключен к входам сброса триггера блокировки инверсии и триггера разрешения,счета. На чертеже представлено устройство для обнаружения ошибок в блоках контроля процессора. Устройство содержит регистр 1 команды Диагностика, первую группу 2 элементов И, .триггеры 3 инверсии, вторую группу 4 элементов Иг элементы 5 сложения.по модулю д.аа, триггеры 6 контрольных разрядов, блоки 7 контроля по четности, триггеры 8 ошибок, элемент 9 ИЛИ, триггер 10 обобщенной машинной оыибки, третью- группу элементов И, триггер.12 блокировки инверсии, счетчик 13 тактов, триггер 14 разрешения счета, узел 15 выходного переноса, шину 16 информации блока уп5равления, шину 17 управления блока центрального управления (ЦУ), шину 18 контрольных разрядов, информационные шины 19 блоков арифметического и ЦУ, шину 20 прерывания по контролю. Устройство работает следующим образом. С помощью команды Диагоностика, содержащей признаки инверсии контрольных разрядов, имитируются ошибки в блоках контроля по четности, которые затем обрабатыва ются в блоке прерывания как прерывание по контролю. В момент выполнения команды Диагностика производится выборка из оперативной памяти управляющего слова команды, которое содеркит информацию о признаках инверсии, о блокировке инверсии, о разрешении счета и о тактах блокировки инверсии. Управляющее слово команды Диагностика по шине информации блока 16 управления памятью поступает на регистр I команды Диагностика. Зате:-; из блока ЦУ по шине 17 управления блока ДУ поступает упра ляющий сигнал на первые входы элементов И первой группы 2 и элементов И третьей группы 1I. При наличии этого сигнала и единичном состоянии разрядов регистра 1 команды Диагностика, содержащих информацию о признаках инверсии, блокировке инверсии, разрешении счета и о тактах блокировки инверсии, срабатьшают первая и гтретья I1 группы элементов И, производится установка в единичное состояние соотве ствующих триггеров 3 инверсии, три гера 52 блокировки инверсии, триггера 14 разрешения счета и занесение на счетчик 13 тактов соответ ствующего количества тактов блокировки инверсии. Нулевой уровень ин версного выхода триггера I2 блокировки инверсии блокирует вторую группу 4 элементов.И. Единичное состояние триггера 14 разрешения с та поступает на счетный вход счетчика 13 тактов, вследствие чего сч чик 13 тактов начинает считать так ты работы процессора. Сигнал выход ного переноса узла 15 выходного пе носа производит сброс в нулевое со тояьше триггера 12 блокировки инве сии и триггера 14 разрешения счета При этом единичный уровень инверсного выхода триггера 12 блокировки инверсии совместно с единичными сигналами триггеров 3 инверсии формирует сигналы инверсии на выходе второй группы 4 элементов И, которые при сложении с сигналами контрольных разрядов, поступающих но шине 18;. контрольных-разрядов на элементы 5 сложения по модулю два, производят инвертирование контрольных разрядов и установку инверсного кода на триггеры 6 контрольных разрядов. Блоки 7 контроля по четности следят за соответствием состояния.тригге ров 6 контрольных разрядов и информационных разрядов, поступающих по информащюнной шине 19 блоков арифметического устройства и ЦУ, Установка инверсного кода на триггеры контрольных разрядов приводит к тому, что блоки контроля по четности выбарабатывают сигналы ошибки, устанавливающее в состояние ошибки соответствующие триггеры 8 ошибки и через элемент 9 ИЛИ триггер 10 обобш,енной машинной ошибки. От триггера 10 обобщенной машинной ошибки формируется сигнал сброса в нулевое состояние триггеров 8 ошибки, триггеров 3 инверсии триггера 12 блокировки инверсии и вьщается сигнал в шину 20 прерывания по контролю два обработки его блоком прерывания. Блок прерьшания организует переход к выполнению специального теста, который анализирует информацию о коде ошибки и моменте ее обнаружения. Задавая различные ко1ды на счетчик 13 тактов, можно с помощью признаков инверсии формировать сигналы ошибок в интервале времени до 2,68 с. На любом такте работы процессора, заданном управляющим словом команды Диагностика, тест проверяет наличие сигнала ошибки, а на других тактах - отсутствие сигнала ошибки, что позволяет своевременно обнаружить неисправности блоков 7 контроля по четности процессора. Технико-экономический эффект от использования предлагаемого устройства состоит в том, что добавление небольшого количества оборудования к уже имекнцемуся дает возможность выявить все неисправные элементы блоков контроля оборудования процессора, что значительно повышает эксплуатационную надеа:7ность процессора и дает экономии 440000 рублей в год. Формула изобретения Устройство для обнаружения оши бок в блоках контроля процессора содержащее регистр команды /.1иагностика, первую группу элементов И, триггеры инверсии, элементы сложения по модулю два, триггеры контрольных разрядов, блоки кок троля по четности, триггеры ошибок элемент ИЛИ, триггер обобщенной ма ршнной ошибки, причем вход регистра команды Диагностика является информационным входом устройства, выходы, регистра команды Ди агностика подключены к первым входам элементов И первой группы, вторые входы которых являются управляющими входами устройства, выходы элементов И первой группы под ключены к первым входам тр1иггеров инверсии, первые входы элементов сложения по модулю два являются входом контрольных разрядов устрой ства, выходы элементов сложения по модулю два подключены к установ ным входам триггеров контрольных разрядов, выходы которых подключен к первым входам блока контроля по четности, вторые входы которых являются информационными входами уст ройства, выходы блока контроля по четности соединены с входами установки триггеров ошибок, выходы которых через элемент ИЛИ соединены с входом триггера обобщенной ошибки, выход которого подключен к вхо дам сброса триггеров инверсии и тр геров ощибок, а также является выходом устройства, отличающееся тем, что, с целью расширения функционалы гх возможностей за счет обеспечения контроля на любом такте работы, в него введены вторая и третья группы элементов И, триггер блокировки инверсии, счетчик тактов, триггер разрешения счета, узел выходного переноса, причем первые входы элементов И второй группы подключены к выходам триггеров инверсии, вторые входы подключены к нулевому выходу триггера блокировки,выходы элементов И второй группы подключены к вторым входам элементов сложения по модулю два, входы установки триггера блокировки инверсии, счетчика тактов, триггера разрешения счета подключены к выходам элементов И третьей групоь, первые входы которых подключены к выходам регистра команды Диагностика , а вторые входы являются управляющими входами устройства, кроме того, сбросовый вход триггера блокировки инверсии соединен с выходом триггера обобщенной ошибки, единичный выход триггера разрешения счета соединен со счетным входом счетчика тактов, выходы которого подключены к входам узла выходного переноса, выход которого подключен к входам 5роса триггера блокировки инверсии и триггера разрешения счета, Ис точники информации, принятые во внимание при экспертизе 1.Техническое описание устройства ЕС-2050, Ц53.057. 2.Техническое описание устройства ЕС-2060 Ц53о057.Т04 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля передачи информации между каналом и процессором | 1980 |

|

SU960824A1 |

| Устройство для сигнализации между процессорами | 1991 |

|

SU1837304A1 |

| Устройство для диагностики ошибок ЭВМ | 1980 |

|

SU1012260A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Процессор цифровой вычислительной системы | 1971 |

|

SU475897A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

Авторы

Даты

1982-02-07—Публикация

1980-06-25—Подача