(54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ЛОГИЧЕСКИХ СУББЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для формирования тестов субблока логического блока | 1983 |

|

SU1088000A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

1

Предлагаемое устройство относится к области цифровой контрольной аппаратуры и может быть использовано при производстве цифровой аппаратуры или при обслуживании вычислительных систем.

Известны устройства для проверки логических субблоков, содержащие счетчик, регистр воздействия, блок клапанов, входной регистр, узел контроля, блок анализа и индикации и узел управления.

Недостатком известных устройств является необходимость эталонного блока, недопустимо большое время проверки или необходимость построения специальных тест программ для каждого типа логических субблоков.

Предлагаемое устройство отличается тем, что оно содержит коммутатор этапов, коммутатор выходов, первые ;входы которого соединены с выходами входного регистра, а второй вход - со вторым выходом узла управления, клапан выхода, первый вход которого соединен с выходом коммутатора выходов. Второй вход соединен с первым выходом узла управления, а выход - со входом узла контроля. Выход блока сменных констант соединен со входом выходного регистра, причем коммутатор этапов, блок клапанов и выходной регистр выполнены из ряда секций, а каждая секция блока клапанов и выходного регистра выполнена из двух подсекций. Выходы подсекций блока клапанов соединены с соответствующими входами подсекций выходного регистра, а выходы секций блока клапанов - с выходами соответствующих секций коммутатора этапов. Третий выход узла управления соединен с входом блока сменных констант ,и с нервыми входами коммутатора этапов, вторые входы которого соединены с выходом счетчика и входом узла

управления.

Другим отличием предлагаемого устройства является то, что в нем узел управления содержит переключатель режимов и последовательно соединенные дещифратор окончания

цикла, счетчик выходов, дешифратор выходов, счетчик этанов и дешифратор номера этапа.

Это позволяет использовать единый алгоритм при проверке различных логических субблоков. Для субблоков с больщим числом входов удается осуществить проверку за сравнительно небольщое время без разработки специальных тестовых программ с использованием дорогостоящего программного обеспечения и без использования эталонных субблоков.

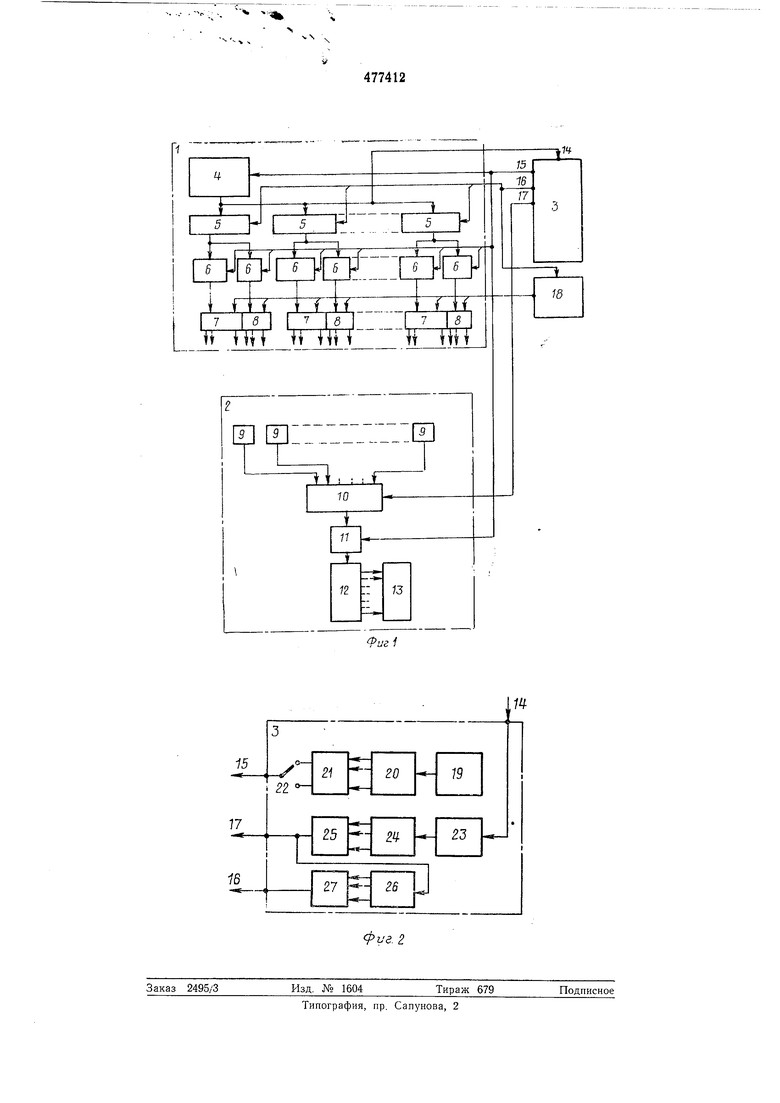

Па фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - структурная схема узла управления предлагаемого устройства.

Устройство для проверки логических субблоков содержит узел воздействия на контролируемый объект 1, узел фиксации состояния выходов 2 и ззел управления 3. Объект 1 включает в себя счетчик 4, коммутатор этапов 5, блок клапанов 6 и подсекции 7 и 8 выходного регистра устройства воздействия. Узел фиксации состояния выходов объекта 2 содержит входной регистр 9, коммутатор выходов 10, клапан выхода 11, узел контроля 12 и блок 13 анализа и индикации. Узел управления 3 для связи с другими блоками содержит входные шины 14, выходные тактовые шины 15, выходные эталные шины 16, выходные шины «Контроль выходов 17 и блок 18 сменных констант. Узел управления 3 содержит задающий генератор 19, счетчик тактов 20, дешифратор тактов 21, переключатель 22 рода работы, дешифратор окончания цикла 23, счетчик выходов 24, дешифратор выходов 25, счетчик этапов 26 и дешифратор номера этапа 27.

При проверке комбинационных субблоков, что соответствует одному из положений коммутатора этапов, предлагаемое устройство работает следующим образом.

Под действием сигналов, поступающих на вход счетчика 4 с тактовой шины 15, состоя, ние его выходных сигналов меняется от 0,0, ..., О до 1,1, ..., 1. Тестовый набор, соответствующий произвольно выбранному рабочему такту, поступает через исполнительные элементы-подсекции 7 на входы объекта. В течение рабочего такта сигнал с выхода объекта, избранного с помощью коммутатора 10, поступает через открытый клапан выхода 11 на узел контроля 12 (например, суммируется на счетчике). После повторения этого процесса 2 раз, что соответствует перебору всех тестовых наборов от 0,0, ..., О до 1,1, ..., 1, процесс с помощью узла управления прекращается, и на блоке 13 индикации и анализа высвечивается и анализируется с целью определения исправности и диагностики причины неисправности объекта проверки, сумма единиц, накопленная в контроле 12. Разрядность счетчика 4 может быть меньше числа выходов контролируемого субблока. На остальные входы подаются сигналы с блока 18. Затем коммутатор выходов 10 переключает вход узла контроля на следующий выход объекта проверки, выходы счетчика 4 подаются на другие входы субблока. В течение времени заполнения счетчика 4 узел контроля 12 формирует контрольную сумму, например, сумму единиц, -служащую критерием исправности второго выхода и так далее, пока не будут проверены все выходы контролируемого субблока. При проверке субблоков с логической памятью (второе положение переключателя 22) работа происходит в два такта: подготовительный и рабочий. Благодаря работе блока клапанов 6 на подготовительном такте на выходной регистр подается только часть сигналов с выхода счетчика 4, и соответственно

работает только часть (подсекция) 8 выходного регистра, часть (подсекция) 7 регистра обнулена. Клапан выхода II закрыт, поэтому узел контроля ,не накапливает информации.

К подсекции 8 выходного регистра подключают входы элементов логической памяти объекта. Таким образом, в подготовительном такте логическая память объекта устанавливается в одно из возможных состояний, соответствующее тестовому набору, поступающего со счетчика 4.

В следующем, рабочем такте, состояние счетчика 4 остается неизменным, но под действием блока клапанов 6 подсекция 8 выходного регистра обнуляется, а на подсекции 7 подается тестовый набор со счетчика 4.

В рабочем такте комбинационная часть схемы объекта подвергается совместному действию внешних сигналов с подсекции 7

выходного регистра и внутренних сигналов обратной связи, соответствующих состоянию логической памяти, заданному на подготовительном такте.

Состояние счетчика 4 в режиме проверки

объектов с логической памятью -должно оставаться неизменным в течение подготовительных и рабочего тактов; после заполнении счетчика 4 часть объекта, соответствующая избранному набору его входов и выходу, провернется на полном переборе входных сигналов для каждого из возможных состояний логической памяти объекта.

Необходимая последовательность работы блоков схемы обеспечивается: задающим генератором 19 устройства управления, частота которого определяет длительность рабочего такта устройства; счетчиком тактов 20, дешифратором тактов 21 и переключателем 22 рода работ, благодаря которым осуществляется работа устройства в режиме проверки чисто комбинационных схем и схем с логической памятью; дещифратором окончания цикла 23, счетчиком выходов 24 и дещифратором выходов 25, благодаря которым происходит

переключение на новый выход объекта после окончания цикла работы счетчика 4.

Так как время цикла перебора значений счетчика 4 очень сильно зависит от числа его разрядов п, то для увеличения числа исполнительных схем выходного регистра без существенного увеличения времени проверки предусмотрен коммутатор этапов 5, счетчик этапов 26, дещифратор номера этапа 27 и блок 18 сменных констант. В начале проверки под действием коммутатора этапов сигналы со счетчика 4 поступают только на первую секцию исполнительных схем выходного регистра. На все остальные исполнительные схемы регистра под действием узла управления 3 подаются сигналы, соответствующие константе № 1, хранящейся в блоке 18 сменных констант. Эти сигналы обеспечивают отсутствие сигналов, поступающих с непроверяемых на

данном этапе частей субблока. Сигналы константы обеспечивают чувствительность путей от проверяемых входных полюсов к контролируемому выходу. После завершения этапа, что соответствует получению контрольной суммы для данного выхода, с помощью коммутатора этапов 5 происходит переключение выходов счетчика 4 на вторую группу исполнительных схем выходного регистра и вызов константы № 2 из блока 18 сменных констант. Проверка закончится после прохождения всех этапов.

Предмет изобретения

выхода, первый вход которого соединен с вЫходом коммутатора выходов, второй вход соединен с первым выходом узла управления, а выход - со входом -узла контроля, блок сменных констант, выход которого соединен со входом выходного регистра, причем коммутатор этапов, блок клапанов и выходной регистр выполнены из ряда секций, а каждая секция блока клапанов и выходного регистра

выполнена из двух подсекций, выходы подсекций блока клапанов соединены с соответствующими входами подсекций выходного регистра, а входы секций блока клапанов - с выходами соответствующих секций коммутатора этапов, третий выход узла управления соединен с входом блока сменных констант и с первыми входами коммутатора этапов, вторые входы которого соединены с выходом счетчика и входом узла управления.

477412

Авторы

Даты

1975-07-15—Публикация

1972-04-30—Подача