1

Изобретение относится к вычислительной технике и может быть использовано для управления работой по программе специализированной ЦВМ или для реализации стандартных подпрограмм в ЦВМ общего назначе ния.

Работа ЦВМ по фиксированной программе обычно реализуется с помощью известной структуры, содержащей следующие основные функциональные блоки:

распр)еделитель,реализующий работу ЦВМ по программе путем возбуждения одной из своих выходных щин (каждой команде в программе соответствует свой выход распределителя|;.

регистр, адреса первой команды, необходимый для образования прямых и инверсных сигналов кода адреса команды (через этот регистр поступает код адреса при безусловных и условных переходах);

регистр адреса второй команды, хранящий адрес команды, к которой необходимо обратиться после выполнения стандартной подпрограммы при двухранговом режиме работы;

постояпяное запоминающее устройство, в котором хранятся команды;

дешифратор адреса команды, на вхой которого поступает адрес очередной команды из регистров команд и с выхода кото- ; рого возбуждается одна из ячеек постоян-

ного запоминающего устройства; - регистр кода операпии, служащий для храения кодовой части команды, поступающей из остоянного запоминающего y тpoйctвa;

дешифратор кода операции, обеспечивающий выполнение одной команды путем выдачи необходимой последовательности управляющих сигналов;

регистр адреса первого операнда, а в случае двух- или трехадресной системы команд еще и регистры адреса второго и третьего операндЬв;

дешифратор адреса операндов, получающий информацию из регистров адресов oneрандов в виде кода 1 из 2 в каждом разряде и возбуждающий своими выходным сигналом одну из ячеек оперативного запоминающего устройства процессора.

Каждый из перечисленных блоков явля функционально, а часто и конструктивно самостоятельным устройством, поэтому известнь е управляющие устройства весьма сложны.

Цель изобретения - упрощение устройства н повышение его экономичности.

Достигается это за счет совмещения функций некоторых перечисленных блоков в других блоках.

Сущность изобретения достигается в том, что в устройстве каждый выход распределителя подключен к соответствующим входам записи дешифратора адреса операнда регистров адреса операнда, дешифратора кода операции и регистров ад}реса команды. Это дает возможность выподнить функции постоянного запоминающего устройства, одного регистра адреса операнда и регистра кода операции в системе шин Связи распределителя с другими блоками и исключить три упомянутых функциональных блока.

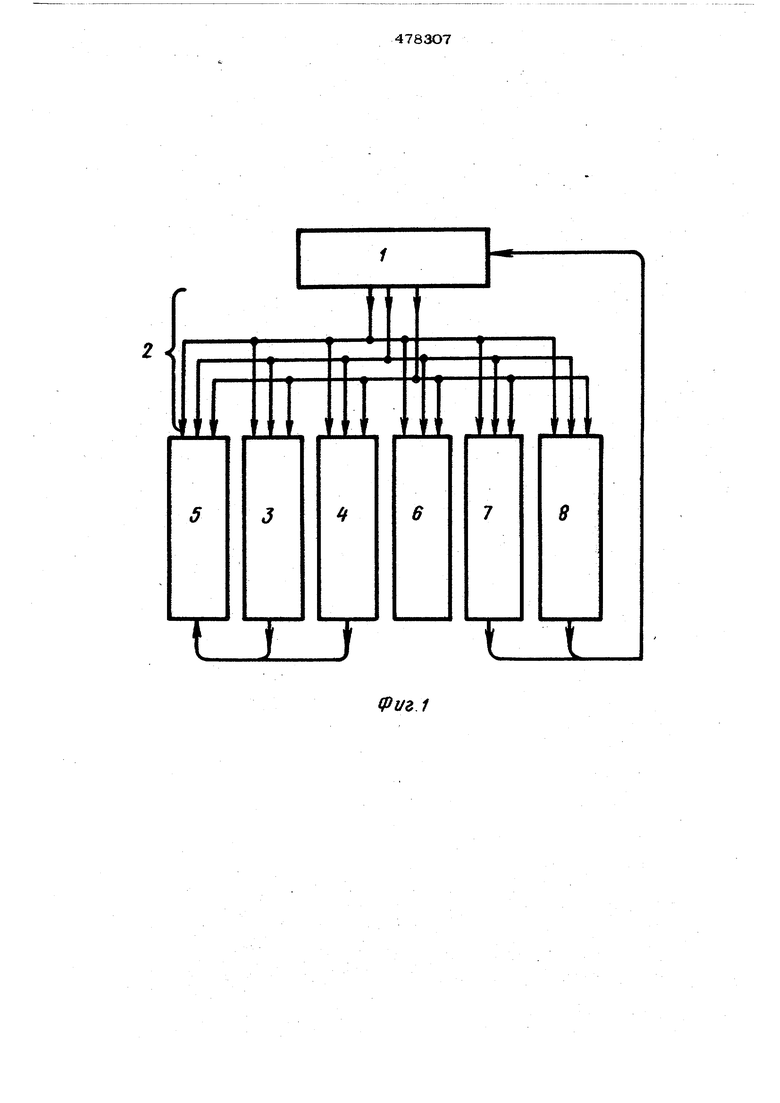

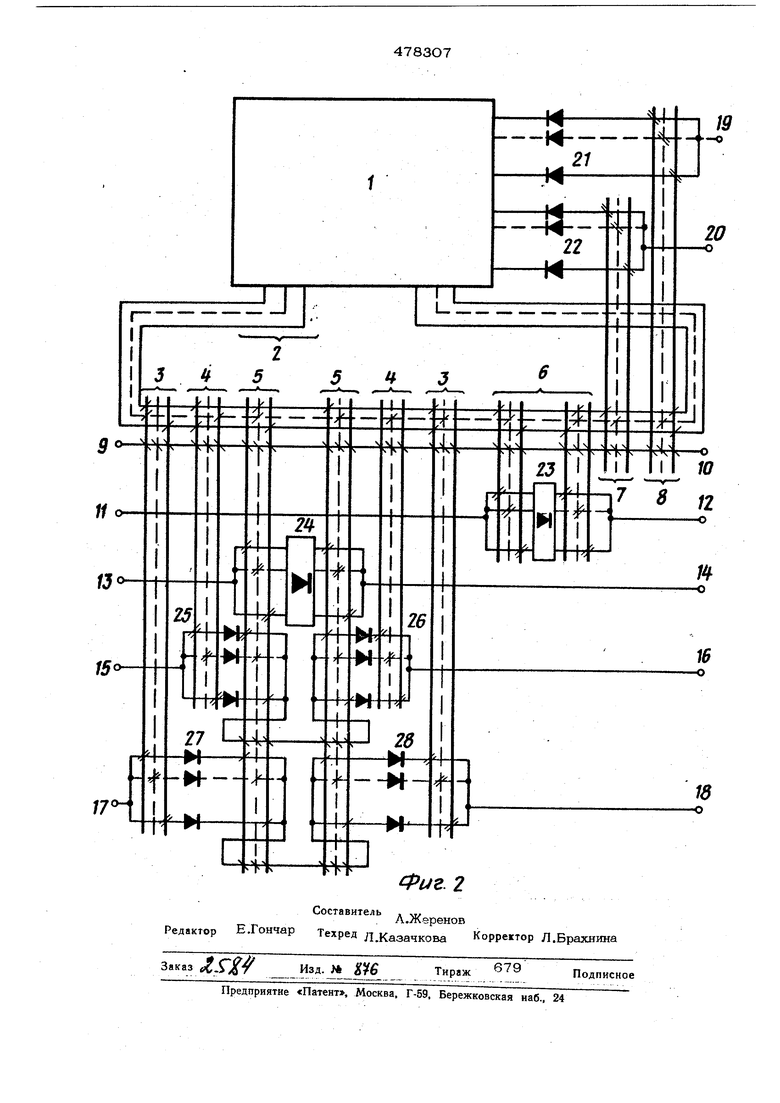

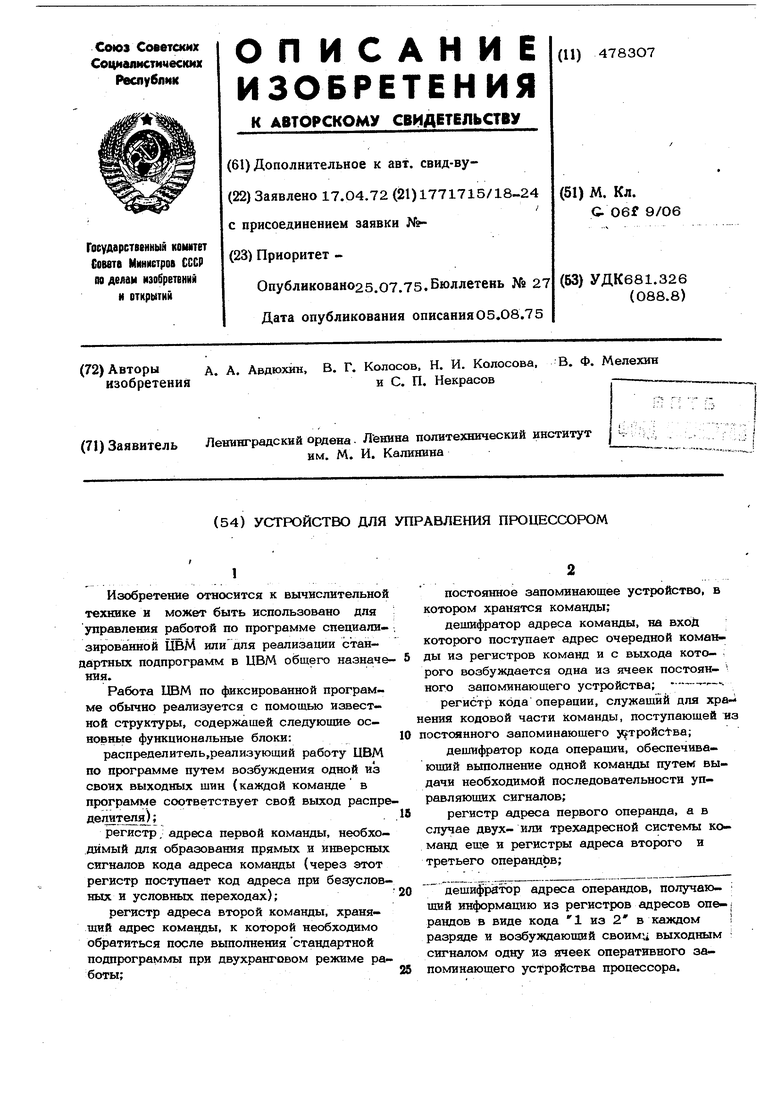

На фйгП приведена блок-схема устройства; на фиг. 2 - схема устройства с применением магнитных переключателей тока.

Устрюйство содержит распределитель 1, построенный, например, по распространенной схеме из счетчика и дешифратора, реализуюигай поочередную передачу импульсов на свои выходные 2; регистры адреса операнда 3, 4, соединенные известным образом с дешифратором адреса операнда; дешифратор адреса операнда 5, дешифратор кода операции 6, регистры адреса команды 7, 8, соединенные известным образом с распределителем.

Входы устройства и соответствующие им выходы 9 и 1О, 11 и 12, 13 и 14, 15-. и 16, 17 и 18, входы 19, 2О устройства: диодные матрицы 21-28.

Количество регистров адреса операнда зависит от адресности команд и составля|ет величину от нуля при одноадресной

системе до двух при трехадресной. Количество регистров адреса команды равно числу рангов управления в программе.

Изображенная на чертеже структура соответствует трехадресной системе команд при двухранговом управлении. ,

Работает устройство следующим образом. В процессе реализации программы на одной из выходных шин 2 распределителя 1 появляется сигнал. При появлении на выходе распределителя сигнала обеспечивается: .запись В дешифраторе адреса операнда 5 адреса первого операнда, в .дальнейшем с помошью дешифратора 5 считывается оперативное запоминающее

устройство (на чертеже не показано); за-. пись информации в регистры адреса операнда 3,4, в дальнейшем эта информация будем переписана в дешифратор адреса операнда 5 для ; считывания содержимого оперативного запоминающего устройства по соответствующему адресу; запись информации в дешифратор кода операции 6,

в дальнейшем с его выходов будут сформированы сигналы в другие узлы процессора, обеспечивающие выполнение команды; запись информации в регистры адреса команды 7, 8, в дальнейшем эта информация поступит в распределитель 1 для осуществления условного или безусловного перехода в программе, в том числе на новый ранг программы (из подпрограммы или в подпрограмму) .

Таким образом, в структуре устройства исключены постоянное запоминающее устройство, один регистр адреса операнда и регистр кода операции.

Рассмотренная структура устройства может быть реализована на различных логических элементах. Однако особенно эффективно у в данном случае применение магнитных переключателей тока в конструктивном оформлении с отверстиями через сердечники, сохраняемыми после заливки элемента компаундом. Параметры импульса тока на выходе распределителя рассчитываются таким образом, что для подготовки перекгаочателей достаточно одного витка. В этом случае цепь каждого из выходов 2

распределителя 1 представляет собой шину, проходяшую без промежуточных паек через все необходимые сердечники блоков 5, 3, 4, 6, 7, 8.

В схеме (фиг. 2) дешифратор адреса операнда 5 и дешифратор кода операции 6 выполнены двухступенчатыми с диодной матрицей.

При работы схемы подачей импульсов 1ток;а по цепи 9-10 обеспечивается начальная установка; по цепи 11-12 - считывание дешифратора кода операции 6; по цепи 13-14 - считывание дешифратора адреса операнда 5; по цепи 15-16 - передача информации из регистра адреса операнда 4 в дешифратор адреса 5; по цепи 1718 - передача информации из регистра адреса операнда 3 в дешифратор адреса операнда 5; по цепям 19-20 - передача адреса команды в распределитель 1 из регистров адреса команды 7 и 8.

По окончании выполнения очередной , манды по цепи 9-10 производится установка блоков 3-8 в исходное состояние.

В случае выполнения команд переходов (условного или безусловного) адрес команды, к которой возможен переход, записывается в регистр адреса команды 7, Тогда, если условие перехода выполнено, то в конце выполнения данной команды по иепв 2О считывается содержимое регистра 7 и адрес перехода вводится в распределитель 1. Если необходимо перейти к вьшолнению подпрограммы младшего ранга, то для запоминания адреса команды программы старшего ранга, к которой осуществляется (Возврат, этот адрес вводится в регистр адреса команды 8. После выполнения подпрограммы младшего ранга производится считывание содержимого регистра 8 по цепи 19 и в распределитель 1 вводится адрес возврата.

Запись информации в регистры и дешифраторы осуществляется путем установки определенных сердечников переключателей тока в проводящее направление. При этом готовится единственный путь для тока в цепях считывания этих устройств, определяемый комбинацией из двух проводящих сердечников, если устройство имеет два переключателя тока (по одному сердечнику в каж; дом переключателе, например в блоках 3-6), или одним проводящимсердечником, если устройство имеет один переключатель тока. (например, в регистрах 7, 8). Это относится как к начальному вводу инфор- махши в блоки 3-8 из распределителя 1 по обмоткам записи, включенным в цепи выходов распределителя, так и к передаче информации из регистров 3 и 4 в дешифратор адреса операнда 5 при считывании регистров 3 и 4 по цепям 15 -. 16 и 17- 18. При этом отпадает необходимость

двоичного кодирования, а при вводе информации в дешифраторы 5 и 6 - необходим мость перевода каждого двоичного разряда в код 1 из 2. Кроме того,в устрюйстве функции одного регистра адреса полностью возложены на дешифратор 5.

При одноадресной системе команд регистры адреса операнда 3 и 4 отсутствуют вовсе. Функции регистра кода операции возложены на дешифратор кода операции 6. Функции постоянного запоминающего устройства распределены между всеми блоками 3-8 и выполняются системой их об-я, моток записи.

Сердечники всех блоков 3-8 не являются специально введенными с целью организации на них постоянного запоминающего устройства, они являются неотъемлемой частью самих блоков.

Предмет изобретения

Устройство для управления процессором , содержащее распределитель, регистры адреса операнда, дешифратор адреса операнда,; входы которого подключены к соответствующим выходам регистров адреса операнда, регистры адреса команды, выходы которых соединены с соответствующими входами распределителя, и дешифратор кода операции, отличающееся тем, что, с целью упрощения устройства и повышения его экономичности, в нем каждый выход распределителя подключен к соответствующим входам записи дешифратора адреса операнда, регистров адреса операнда, дешифратора кода операции и регистров адреса команды.

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Устройство для формирования исполнительных адресов цифровой вычислительной машины | 1978 |

|

SU728129A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU521588A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Система числового программного управления | 1972 |

|

SU448789A1 |

| Устройство управления | 1976 |

|

SU650079A1 |

| Программируемый контроллер | 1987 |

|

SU1537016A1 |

| Устройство для сбора телеметрителеметрической информации | 1975 |

|

SU527727A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

r

fpi/г 1

Авторы

Даты

1975-07-25—Публикация

1972-04-17—Подача