(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ТЕЛЕМЕТРИЧЕСКОЙ

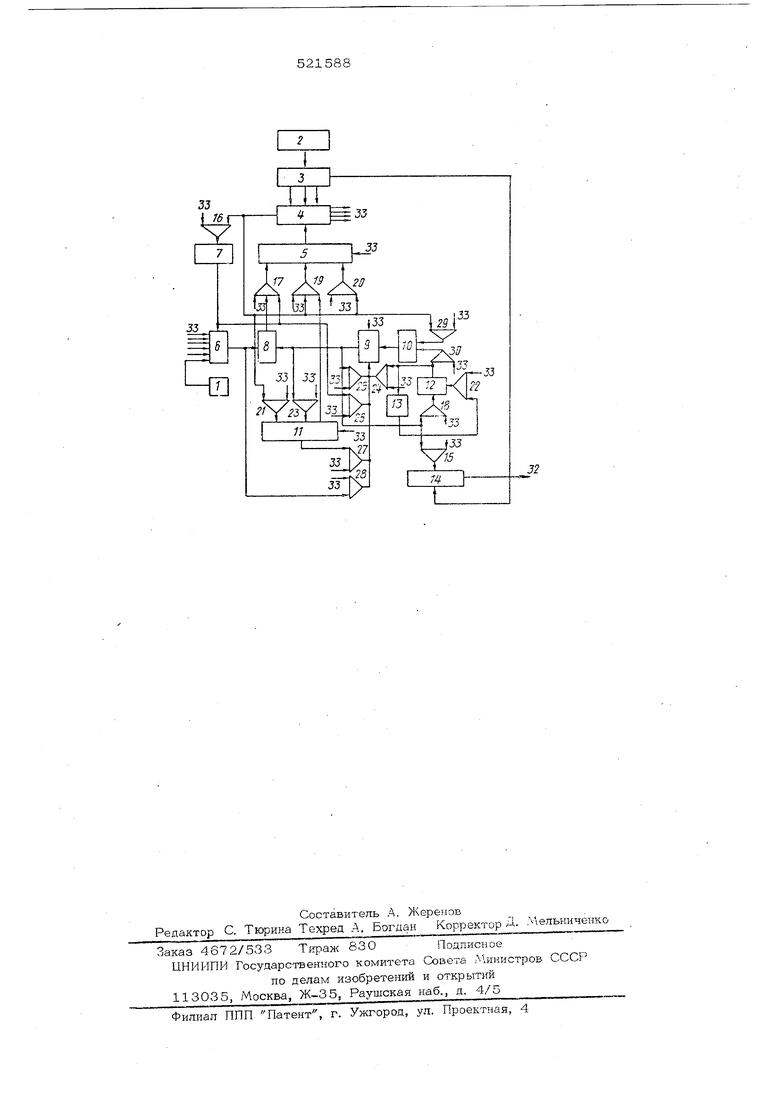

ИНФОРМАЦИИ со своим ин|)ормащюнным входом, управляющие входы упомянутых ключей, адресного регистра управления, оперативного запомина шего блока и блока вычислений соединены с выходом блока управления. Известные устройства характеризуются большими затратами оборудования, связаннь;- ми с наличием автономного буферного эапо минаюшего блока выполняющего уплотнение поступившей в устройство инфор ла1П и для равномерного вьшода ее в канал связи, а также трудностью орд-анизаШ1и лрограммировалного вьшода информаиии в каиал связи. В частности, в нем отсутствует возможност задержки вьюода отдельных массивов ииформации в канал связи при неблагоприятном состоянии канала связи даже при наличии на входе устройства данных о состоянии канала связи в виде показаний тех или иных телеметрических датчиков. Целью изобретечия является упрошеиие и повышение коэфс1)ИШ{ента 1 СпользоЕаиш оборудования усгройства. В оиисьшдемо / устройстве это цосачггается , что оно со держит иидексньш регистр, регистр сдвига, дешифратор единичного набора и дополиитель яые ключи, причем у1травляю1ций вход регист ра сдвига подключен ко второ :у выходу рас пределителя тактовь Х И; ;иульсоБ, вход че рез одиннадцатый ключ соединен с вь:хопом оперативного чаполи-таюилего блока, выход подключен к выходу устройства, первый вх&д индексного регистра через цвйнаддатым клю соединен с выходол операт;1Биого запоки -иаюшего блока, выход подключе;; ко входу дешифратора едиш1чиого i;a6opa, а череа тринадцатый ключ соединен с информашонным входом оперативного запоминающего блока и через четырнадцатый ключ - со ETO входом адресного регистра оперативного aanotvn-fHaMniero блока вь;хоа дешифратора единичного набора пятнадцатый ключ подсоединен ко второму входу индексного регистра, информаш- онный вход оператив;юго заиомииаюжего блока через и1естнадиатый ключ соединен с выходок; адресргого регистра коммутаторе. украЕЛЯЮшие входы ключей с одигаадцато О ио шестаадиатьй соед1;иеиы с выходом блока упраплепия. Этим цостигается возможкость выполпеник оперетивньг 1 запоминающ М блоком функций буфер}ого заг:о «;инающего блока с программируехгым выводом накоплет-юй s информаш-ги че рез регистр сдвига в калап сиязи управляв мьгм на основе ..анньгх, поступающих в устройство от телел;етрическик д.a.гчлкoвJ подключенных ко входу устройства. На чертеже 11редст влена схема описы ваемого зстройстъа. Оно содержит генераторi i 1 и 2 импульсов, распределитель 3 тактовых импульсов, блок 4 управления, адресный регистр 5 управлеиия, коммутатор 6, адресный регистр 7 коммутатора, блок 8 анализа, оперативньй запоминающий блок 9, адресньш регистр 10оператив-юго запоминающего блока, блок 11вычислений, индексный регистр 12, де- 1иифратор 13 еди-ничиого иабора, регистр сдвига 14, ключи 15-30, вход 31 и вы ход 32 устройства, управляющие цепи связи 33 выхода блока 4 управления с узла - MJ: устройства. Блок 4 управления представляет собой иостоянное зацсминающее устройство резистивного диодного, трансфор аториого или любого другого извест1:ого типа с автоиомн} 1м узлом управления и дешифрирования команд. Гене ратор 1 импульсов обеспечивает иа своем выходе наличие сигнала тииа геандр с периодом смены уровией, равным требуемой дискретности отсчета текущего времени в устройстве. Блок 8 аиализа обесиечивает выдачу управляющего сигнала на своем выходе в случае, если числа н его входах не сравниваются Гчгеждз - собой по некоторому заданному критерию. Оперативный запоминаюИ1ИЙ блок 9 имеет адресную стр ктуру и может быть выполнен по любому известному гринципу. Включение блока на режим загжси и,;г считывания осуществляется подачей соответствующего сигнала иа его управляю- вход с командного выхода блока 4. Блок J-1 обеспечивает выпо-лнение операций суммироБания и сраидеиия ио равенству двух Чисел, поданных на его входы через .: 21 Г; 23, Переключение режима работы блока (,;мирование или сравнение) осуществляется подачей командного сигнала с выхода блока 4. Включение управляющего выхода блока ир.оиззоаится только в режиме сравнения (сигнал на этом выходе появляется в случае неравенства сравниваемых чисел). Разрядная сетка блока 11 равна раз ГКдиой сетке оперативного запоминающего блока О. Адресньш регистр 5 выпоянея по схеме счетчика, содержимое которого уве.ч; чг;вается на едиш-щу сн налом с кокганд- ного вьгхода блока 4, подаваемы. иа счет- ьш вход регисра в каждом цикле обраше- иия к блоку 4, что позволяет организовать в устройстве естественный порядок вьгаол нения команд, записанных в опоке 4. Итдексный регистр 12 также выполнен ио схеме счогчика, содержимое которо:го увеличивает ся иа единицу сигналом с командного выхо- . да. блока 4, иодаваемым на счетный вход регистра но оконча и-ш считьюания записанного в нем чгтсла в каждох случае обращения к регистру. Дешифратор 13 единичного набора обеспечигвает наличие сигнала на его выходе в случае, если в числовом наборе, поданном на его входе, содержится хотя бы один нулевой символ. Регистр сдвига 14 находится постоянно в режиме сдвига за счет подачи на его тактирующий вход последовательности импульсов с выхода распре делителя 3 тактовых импульсов. Скорость сдвига определяет скорость вью ода симво лов числовых кодов, образующих выходную информацию устройства, в канал связи. Часть ячеек блока 9 отведена для хране - ния служебной информации, используемой в устройстве для вьшесения решений о вьюо- де принимаемой от датчика информации в канал связи или ее гашении. Оставшаяся часть памяти служит для хранения информации, отобранной для вьтода в канал связи, т. е. буферного запоминания этой информа ции. Программа работы устройства, записанная в памяти блока 4, содержит комплект подпрограмм, в том числе: подпрограмму А Циклического опроса, входных каналов с анализом избыточности каждой выборки, под программа А имеет начальньй адрес а и заканчивается командой,безусловной пере - дачи управления по адресу набор подпрограмм Б , каждая из которых содержит перечень операций, выполняемых устройство при обнаружении нензбыточной выборки по любому из входных каналов, опрашиваемых в процессе выполнения подпрограммы А, начальный адрес каждой из подпрограмм Bi равен адресу соответствующего входного канала, каждая из подпрограмм данного набора заканчивается командой безусловной передачи управления по адресу подпрограмму С с начальным адресом, равным адресу входного канала, к которому подклю чен выход генератора 1, включающую в себя перечень операций, выполняемых устройством при обнаружении неизбыточной выборки по этому входному каналу, и заканчиваю щуюся командой безусловной передачи управ ления по адресу а. Таким образом, после выполнения любой из подпрограмм (А, В: и / или С) в процессе работы устройства осуществляется пе реход к подпрограмме А. В процессе вьшолнения подпрограммы А осуществляется последовательное выполне - ние следующих операшгй: передача через ключ 16 с информационного выхода блока 4 на адресный регистр 7 коммутатора адреса входного канала и передача полученной выборки с выхода коммутатора 6 на вход блока 8; передача через ключ 29 с информационного выхода блока 4 на адресный регистр 10 оперативного запоминающего блока адреса ячейки, размещенной в участке хранения служебной информации опера - тивного запоминающего блока 9, в котором содержится значение предьщушей выборки, полученной по каналу; включение оперативного запоминающего блока 9 на режим считьюагшя путем подачи на его управляющий вход соответствующего сигнала с командного выхода блока 4 и передача числа, записанного в данной ячейке, на вход блока 8; вьшолнение блоком 8 сравнения нового и старого значений выборок и подача на управляющий вход ключа 17 разрешающего сигнала в том случае, если вновь поступившая выборка признана неизбыточной; передача адреса из адресного регистра 7 коммутатора через ключ 17 в адресный регистр 5, если ключ 17 открыт (выборка признана неизбыточной), или переход к выполне нию следующей команды подпрограммы А, если ключ 17 закрыт (выборка признана избыточной). В последнем случае осущест вляется вывод на адресньй регистр 7 коммутатора адреса следующего входного канала и т. д. В случае обнарзжения неизбыточной выборки в адресный регистр 5 записьгоаеть. ся адрес входного канала, по которому поступила неизбыточная выборка, равный на чальному адресу соответствующей подпро граммы Б t В каждой из таких подпрограмм может быть записано вьшолнение следующих действий: запись в оперативный запоминающий блок 9 в участок хранения служебной информапии нового значения выборки, полученной по входному каналу, по адресу, установленному на адресном регистре 10 оперативного запоминающего блока, путем открывания ключа 28 и подачи сигнала, включающего режим записи, на управляющий вход оперативного запоминающего блока 9 с соответствующего командного выхода и блока 4; запись в буферный участок памяти оперативного запоминающего блока 9 адреса вход ного канала, по которому получена неизбыто ная выборка, с адресного регистра 7 коммутатора путем подключения его через ключ 26 к информационному входу оперативного запоминающего блока 9; запись в буферный участок блока 9 значения неизбыточной БЬ борки с выхода коммутатора 6 путем подключения его через ключ 28 к информа 1шонному входу блока 9; запись в буферный участок блока 9 значения числа, идентифишфующего величину текущего времени в устройстве и зфанящегося в одной или в нескольких ячейках участках зфанения служебной

информащп-i оперативного запомикающегю блока 9, подключения выхода этого блока к его числовому входу через ключ 25. Выполиеьие последних трех операшгй осуществляется с помощью специальных про раммных блоков, входящих в состав выполняемой подпрограммы Б и имеющих свое целью размеще ше записывае /ых чисел (адрес канала, по которому получена неизбыто шая выборка, значения самой выборш и значения текущего времени ее обнаружения) в ячейки буферного участка памяти блока 9 с последовательно возрастающими адресами. Действие этих блоков основано на использовании TeKjiiiero адреса записи (ТАЗ), хранимого в одной из ячеек участка памяти блока 9, причем в процессе записи любого числа в этот участок осуществляется выполнение следующих операщ1Й: передача с блока 4 через ключ 29 адреса ячейки, в которой хранится значение ТАЗ, в адресньш регистр 10 оперативного запоминающего блока; считьтание значения ТАЗ и передача его с выхода блока 9 через клю 18 в индексный регистр 12; передача значения ТАЗ из индексного регистра 12 че рез ключ 30 в адрес1 ЫЙ регистр 10 оперативного запоминающего блока, если при этом значение ТАЗ содержит хотя бы один разряд, не равный единице, т. е. ТАЗ не равен конечному адресу буферного участка памяти блока 9. на выходе дешифратора 13 единичного набора присутствует разрешающий сигнал, открьюающ.ий ключ 22, в резул тате чего сигнал с выхода блока 4, осуществляющий перепись ТАЗ из индексного регистра 12 в адресньп регистр 10 оператив ного запоминающего блока, поступает на счетный вход индексного регистра 12; задним фронтом этого сигнала ос тдествляется увеличение значения ТАЗ, записанного в индексном регистре 12, на единицу т. е. вьшолняется операция индексации ТАЗ; запись числа, поданного на информационный вход onepaTi-fflHoro запоминающего блока 9, в ячейку с адресом, равным неиндексиро ванному значению ТАЗ, записанному в ад - ресном регистре 10; вновь передача с блок 4 адреса ячейки, в которой .ранится зна чение ТАЗ, в адресный регистр 10 опера тивного запоминающего блока через ключ 29 и запись индексированного значения ТА из индексного регистра 12 в эту ячейку через ключ 24 и подача на управляющий вход блока 9 сигнала с выхода блока 4, включающего режим записи, В случае, если осуществляется запись в буферный участок памяти блока 9 нескол ких чисел подряд, передача значения ТАЗ из блока 9 в индексный регистр 12 осуществляется только перед записью первого из этих чисел, а запись в блок 9 индексированного соответствующее количество раз значе 01Я ТАЗ с индексного регистра 12 - только по окончании записи всей группы чисел. Начальпое значение ТАЗ, равное га -v 1 вводится в блок 9 из блока 4 при включении устройства. Таким образом, в процессе работы устройства ос}тцествляется последовательное заполнение буферного участка памяти блока 9 информацией, подлежащей выводу в канал связи. Емкость этого участка выбирают из условия того, что в промежутках между двумя смежными сеансами вывода информации в канал связи общее количество информации, помещаемой в буферный участок, не превысит его емкости. В случае, если по непредвиденным обстоятельствам объем информации, направляемой в буферный участок памяти блока 9, превысит его емкость, индексация ТАЗ прекращается, как только его значение становится равным значению П., т. е. содержащим единицы во всех раз - рядах, В этом случае при записи такого значения ТАЗ в индексный регистр 12 на выходе дещифратора 13 единичного набора появляется сигнал, запирающий ключ 22 и исключающий тем самым прохождение сигнала с выхода блока 4 в момент перезаписи значения ТАЗ из индексного регистра 12 в адресный регистр 10 на счетный вход индексного регистра 1.2, При этом, очевидно, индексация значения ТАЗ прекращается, и запись всей последующей ипформаиии производится в ячейку с адресом П оперативного запоминающего блока 9. Таким образом, исключается возможность искажения информации, содержащейся в участке хранения служебной информации блока 9 в случае переполнения буферного участка за счет присвоения ТАЗ значений, соответствующих первому участку. В процессе выполнения подпрограммы Ь. могут выполняться также следующие опера1В1и: последовательная передача с блока 4 адресов входных каналов, по которым дол жен быть произведен дополнительный сбор информации, на адресньй регистр 7 коммутатора через ключ 16 и записи полученных значений выборок с выхода коммутатора 6 в буферный участок блока 9 по ТАЗ; задание времени проведения очередных измереНИИ по любому из входных каналов путем прибавления к числу, идентифицирующему значение текущего времени, хранящемуся в блоке 9 и вводимому в блок 11 через ключ 23, ЧЕСсла, определяющего требуемую задержку выполнения этих измерений по отноше нию к моменту получения данной неизбыточной выборки, выраженную в единицах отсчета текущего времени, вводимого в блок 11 с блока 4 через ключ 21, и последующей зашюи результатов суммирования через ключ 27 в отведенные для этого ячейки участка хранения алужебной информации блока 9, адреса которых через ключ 29 предварительно вводятся в адресный регистр 10 этого блока с информационного выхода блока 4. Каждая из программ Ь заканчивается выполне1шем команды беаусловной передачи управления по адресу а вьтолняемой путем передачи значения адреса а с информа ционного выхода блока 4 через ключ 2О на адресный регистр 5.

В процессе работы устройства происходит периодическое изменение сигнала на выходе коммутатора 6, к которому подключен выход генератора 1, что воспринимаетс устройством как получение избыточной выборки по этому каналу. В этом случае осуществляется передача адреса с адресного регистра 7 коммутатора через ключ 17 в адресньА регистр 5 и переход к вьтолне - нию подпрограммы С.

При выполнении подпрограммы С осуществляется сначала суммирование числа, идентифицирующего значение текущего времени и хранящегося в блоке 9, с константой, вводимой в блок 11 с информационного выхода блока 4, причем результат суммирования помещается в те же ячейки участка хранения служебной информации блока 9. Далее подпрограммой С осуществляется ъыполнение следующих оп.ерацлй: последовательное сравнение чисел, идентифицирующих время вьшолнения измерений по различным вхоным каналам, записанных в определенных ячейках блока 9, с Ч1-;(слом, идентифицирующим значение текущего времени, путем задания адресов соответствующих ячеек в адресный регистр 10, ввода содержимого этих ячеек в блок 11 и задания режима срав нения - блок 11 сигналом с выхода блока 4; в случае, если сравниваемые числа равны (на выходе блока 3.1 запрещающий сигнал, ключ 19 - закрыт), продолжается выполнение программы в естественном порядке, т. е. описанным выще путем осущест - вляется выполнение измерений по тем каналам, для которых определена необходимость выполнения измерений, с записью значений адресов этих каналов и полученных выборок в буферный участок памяти блока 9 по ТАЗ в случае, если сравниваемые числа не равны (на выходе блока 11-разрешающий сигнал и ключ 19 - открыт), передача адреса из блока 4 чер.ез ключ 19 в адресный регистр 5 и переход к другой части подпро граммы С (например, к сравнению другой

уставки, записанной соответственно в другой ячейке блока 9, с числом, идентифицирующим значение текущего времени). В случае, если в процессе вьшолнения подпрограммы А устройством будет принята неизбыточная выборка от какого-либо из датчиков, свидетельствующая о возникновении щэоводящего состояния канала связи, или в процессе выполнения подпрограммы С будет установлена необходимость по времени вьтода накопленной в буферном участке памяти блока 9 информации, устройством осуществляется переход к подпрограмме вывода информации, заключающейся в выполнении следующих операций: передача с информационного выхода блока 4 адреса ячейки памяти блока 9, в которой хранится значе ше текущего адреса считывания (ТАС), на адресный регистр 10 через ключ 29; считьтание значения ТА С и передача его с выхода блока 9 в индексный регистр 12 через ключ 18; перезапись значения ТАС из индексного регистра 12 в адресный регистр 10 с одновременной индексацией ТАС в индексном регистре 12 тем же путем, что осуществлялась индексация ТАЗ; считывание числа из ячейки буферного участка памяти блока 9 с адресом, равным ТАС, и передача его в регистр сдвига 14 через ключ 15, после чего это чисс- ло в последовательном коде вьтодится из регистра 14 через выход 32 устройства в канал связи.

В качестве начального значения ТАС выб1фается, как и в случае ТАЗ, адрес .

Во время вьтода числа из регистра 14 устройством с помощью уже описанных вььще приемов осуществляется перезапись индексированного значения ТАС в блок 9 и

затем его сравнение в блоке 11 либо со значением адреса п, вводимы -) в блок 11 через ключ 21 из блока 4, либо со значением ТАЗ, записанным к начал} момента вьтода информации из буферного участка памяти блока 9, Если в результате этого сравнения блоком 11 будет установлено неравенство сравниваемых адресов, что означает, что ТАС в процессе индексации еще не достиг значения ТАЗ или п , на выходе блока 11 появляется разрешающий сигнал, ключ 19 открывается и в адресный регистр 5 из блока 4 вновь вписьтается начальньй адрес подпрограммы вывода информации. После этого осуществляется вывод из буферного участка памяти блока 9 на регистр 14 очередного числа, ТАС вновь индексируется в индексном регистре 12 и т. д. В случае равенства ТАС значению ТАЗ или тп на выходе блока 11 формируется запрещающий сигнал, закрьтающий ключ 19, в результате чего осуществляется переход к очередной команде подпрограммы вывод;: в качестве которой записана команда безусловной передачи управления по адресу, т. е, вьшолнение подпрограммы вьюода информации оканчивается и осуществляется переход к подпрограм ме А. Формула изобретения Устройство для передачи телеметричес кой информации, содержащее коммутатор, первый вход которого соединен со входом устройства, адресный регистр коммутатора, выход которого подключен ко второму входу коммутатора и через первый ключ - к первому входу адресного регистра управления, генераторы импульсов, выход первого из ко торых подключен ко входу распределителя тактовых импульсов, выход второго - к третьему входу коммутатора, оперативный запоминающий блок, вход которого соединен с выходом адресного регистра оперативного запоминающего блока, информационный вход через второй ключ соединен с выходом коммутатора, блок анализа, входы которого сое динены соответственно с выходами комму - татора и оперативного запоминающего блока, выход подключен к соответствующему входу первого ключа, блок вычислений, первый вход которого через третий ключ сое динен с выходом оперативного запоминаю шего блока, управляющий выход через чет вертьй ключ соединен со вторым входом ад ресного регистра управления, информационный выход через пятый ключ подсоединен к информационному входу оперативного за поминающего блока, блок управления, первы вход которого подключен к первому выходу распределителя тактовых импульсов, второй вход - к выходу адресного регистра управления, информационный выход через .шестой ключ соединен со входом адресного регистра коммутатора, через седьмой ключ - со вторым входом блока вычислений, через восьмой ключ - с первым входом адресного регистра оперативного запоминающего блока, через девятый ключ - с третьим входом адресного регистра управления, соот - ветствующий вход четвертого ключа соединен с информационньгм выходом блока управления, выход оперативного запоминающего блока через десятый ключ соединен со своим информационны входом, управляющие входы упомянутых ключей., адресного регистра управления, оперативного запоминающего блока и блока вычислений соединены с выходом блока управления, отличающеес я тем, что, с целью упрощения и повьгшения коэффициента использования оборудования устройства, оно содерж.ит индексный регистр, регистр сдвига, дешифратор единичного набора и дополнительные ключи, при чем управляющий вход регистра сдвига подключен ко второму выходу распределителя тактовь1Х импульсов, вход через .одиннадцатый ключ соединен с выходом оперативного запоминающего блока, выход подключен к выходу устройства, первый вход индексного регистра., через двенадцатый ключ соединен с выходом оперативного запоминающего блока, выход подключен ко входу дешифратора единичного набора, а через тринадцатый ключ соединен с информационным входом оперативного запоминающего блока и через четырнадцатый клкчч - со вторым входом адресного регистра оперативного запоминаю щего блока, выход дешифратора единичного набора через пятнадцатый ключ подсоединен ко второму входу индексного регистра, информационный вход оперативного запоминающего блока через шестнадцатый ключ сое - динен с выходом адресного регистра коммутатора, управляющие вход.ы ключей с одиннадцатого по шестнадцатый соединены с выхо - дом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора телеметрителеметрической информации | 1975 |

|

SU527727A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU512484A1 |

| Устройство для передачи телеметрической информации | 1976 |

|

SU652598A1 |

| УСТРОЙСТВО ДЛЯ УПЛОТНЕНИЯ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ | 1974 |

|

SU432566A1 |

| УСТРОЙСТВО ДЛЯ СБОРА ТЕЛЕМЕТРИЧЕСКОЙ ШФОНУ1АЦИИ | 1973 |

|

SU433523A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Авторы

Даты

1976-07-15—Публикация

1974-06-17—Подача