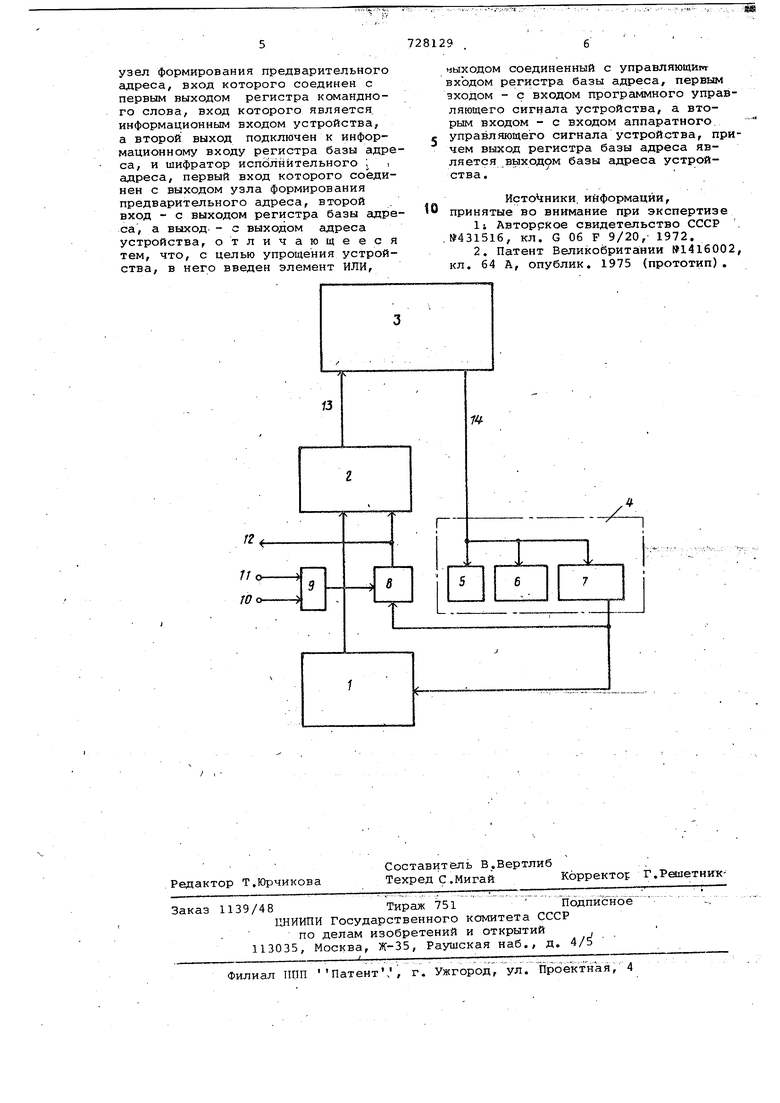

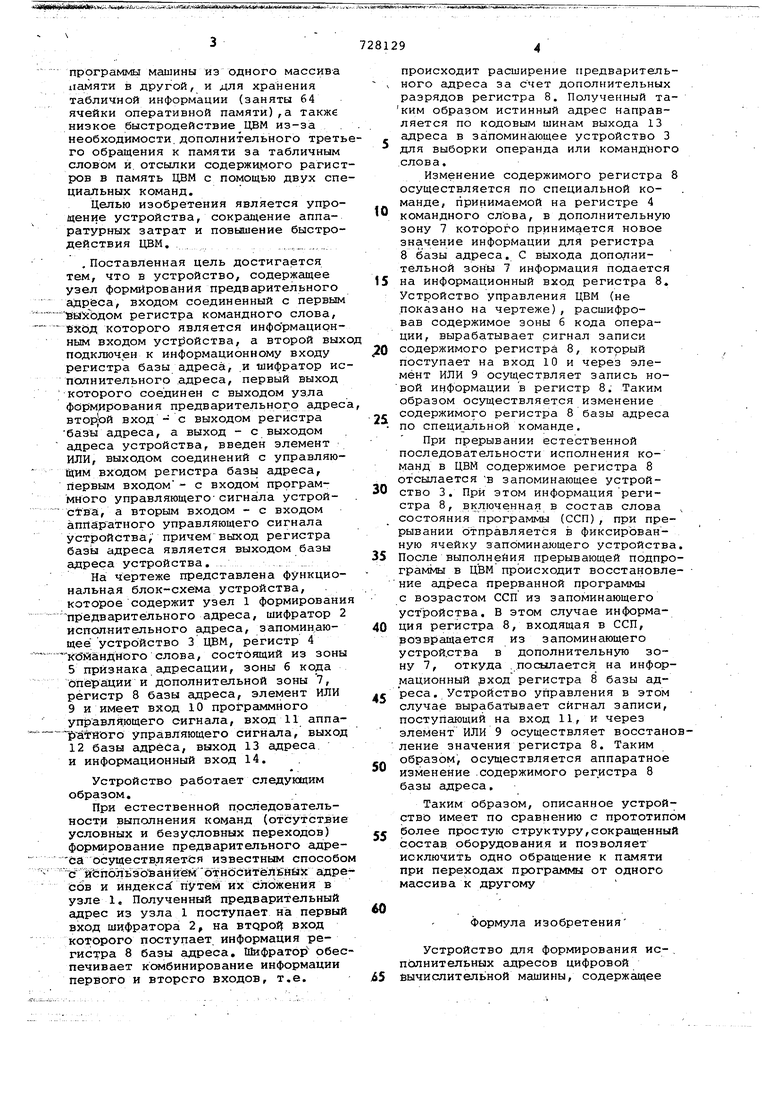

Изобретение относится к области вычислительной техники. Устройство может быть использовано в цифровых вычислительных машинах (ЦВМ), работающих с относительной адресацией.. Известны устройства 1 для формирования исполнительных адресов, содержащие регистр команд, коммутатор, индексный регистр, регистр базового адреса, основной и дополни тельный сумматоры, четыре блока связи, соединенные таким образом, что получение исполнительного . адре образуется путем алгебраического сложения относительного адреса, име щегося в составе команды, и индекса на основном сумматоре или путем сум мирования относительного адреса с с держимым регистра базового адреса на дополнительном сумматоре с выдач полученного исполнительного адреса через регистр адреса в адресную магистраль. Недостатком этих устройств является потеря времени на формирование исполнительного с1дреса путем суммирования значения базового адреса с относительным адресом команды на дополнительном Ьумматоре, что снижает быстродействие устройства и ув личивает затраты оборудования на реализацию дополнительного сумматора и .блоков звязи. Наиболее близким к изобретению по сущности технического решения является устройство для формирования исполнительных адресов ЦВМ с запоминаемой программой 2, содержащее бпок формирования предварительного адреса, включающий регистр адреса, счетчик команд, сумматор, регистры сумматора и второго операнда и индексные регистры, дешифратор ащреса, регистр командного слова, включающий зону признака адресации, зону.кода операции и дополнительную зону, регистр расширения адреса (регистр базы адреса), три дополнительных регистра, соединенных таким образом, что при обращении к памяти формирование истинного адреса осуществляет. ся комбинированием исполнительного адреса н содержимого регистра базы адреса. Недостатками этого устройства являются его сложность к большие затраты оборудования, требуемые для реализации трех дополнительНЕох регистров, хранящих информацию расширяющего регистра при переходе программы машины из одного массива ламяти в другой, и для хранения табличной информации (заняты 64 ячейки оперативной памяти),а также низкое быстродействие ЦВМ из-за необходимости, дополнительного трет го обращения к памяти за табличным словом и. отсылки содержимого рагис ров в память ЦВМ с помощью двух сп циальных команд. Целью изобретения является упро щение устройства, сокращение аппаратурных затрат и повышение быстро действия ЦВМ. . Поставленная цель достигается тем, что в устройство, содержащее узел формирования предварительного адреса, входом соединенный с первым ы5сЬдом регистра командного слова, вхЬд которого является информационным входом уст15ойства, а второй вых подключен к информационному входу регистра базы адреса, .и шифратор ис полнительного адреса, первый выход которого соединен с выходом узла формдоования предварительного адрес втор;ой вход - с ВЫХОДОМ регистра базы адреса, а выход - с выходом адреса устройства, введен элемент ИЛИ, выходом соединений с управляющим входом регистра базь адреса, первым входом- с входом программного управляющего-сигнала устрой , а вторым входом - с входом аппаратного управляющего сигнала устройства, причем выход регистра базы адреса является выходом базы адреса устройства. На чертеже представлена функциональная блок-схема устройства, . которое содержит узел 1 формировани предварительного адреса, шифратор 2 исполнительного адреса, запоминающее устройство 3 ЦВМ, регистр 4 (Зйандного слова, состоящий из зоны 5 признака адресации, зоны б кода операции и дополнительной зоны 7, регистр 8 базы адреса, элемент ИЛИ 9 и имеет вход 10 программного управляющего сигнала, вход 11 аппа рйтгйото управляющего сигнала, выход 12 базы адреса, выход 13 адреса и информационный вход 14. Устройство работает следующим образом. При естественной последовательности выполнения команд (отсутствие условных и безусловных переходов) формирование предварительного адре са осуществляется известным способо с Шпольэс ванйёМ 6тнЬ сйтёльных ад сов и индекс путем их сложения в узле 1, Полученный предварительный адрес из узла 1 поступает на первый вход шифратора 2, на BTQpoJ вход которого поступает информация регистра 8 базы адреса. Шифратор обес печивает кс бинирование информации первого и второго входов, т.е.

728129 происходит расширение предварительного адреса за счет дополнительных разрядов регистра 8. Полученный таким образом истинный адрес направляется по кодовым шинам выхода 13 адреса в запоминающее устройство 3 для выборки операнда или командного слова. Изменение содержимого регистра 8 осуществляется по специальной команде, принимаемой на регистре 4 командного слова, в дополнительную зону 7 которого принимается новое значение информации для регистра 8 базы адреса. С выхода дополнительной зоны 7 информация подается на информационный вход регистра 8. Устройство управления ЦВМ (не показано на чертеже), расшифровав содержимое зоны 6 кода операции, вырабатывает сигнал записи содержимого регистра 8, котррый поступает на вход 10 и через элемент ИЛИ 9 осуществляет запись новой информации в регистр 8. Таким образом осуществляется изменение содержимого регистра 8 базы адреса по специальной команде. При прерывании естественной последовательности исполнения команд в ЦВМ содержимое регистра 8 отсылается в запоминающее устройство 3. При этом информациярегистра 8, включенная в состав слова состояния программы (ССП), при прерывании отправляется в фиксированную ячейку запоминающего устройства. После выполнейия прерывающей подпрограммы в ЦВМ происходит восстановление адреса прерванной программы с возрастом ССП из запоминающего устройства. В этом случае информация регистра 8, входящая в ССП, возвращается из запоминающего устройства в дополнительную зону 7, откуда .посылается на информационный эход регистра 8 базы адреса. Устройство управления в этом случае вырабатывает сигнал записи, поступающий на вход 11, и через элементИЛИ 9 осуществляет восстановление значения регистра 8. Таким образом, осуществляется аппаратное изменение .содержимого регистра 8 базы адреса. Таким образом, описанное устройство имеет по сравнению с прототипом более простую структуру,сокращенный состав оборудования и позволяет исключить одно обращение к памяти при переходах программы от одного массива к другому Формула изобретения Устройство для формирования ис-. поянительных адресов цифровой вычислительной машины, содержащее

узел формирования предварительного адреса, вход которого соединен с первым выходом регистра командного слова, вход которого является информационнЕЛМ входом устройства, а второй выход подключен к информационному входу регистра базы адреса, и шифратор исполнительного ;. адреса, первый вход которого со единен с выходом узла формирования предварительного адреса, второй вход - с выходом регистра базы адревыходом адреса

са, а ВЫХОД- устройства, отличающееся тем, что, с целью упрощения устройства, в негр введен элемент ИЛИ,

чыходом соединенный с управляющийвходом регистра базы адреса, первым зходом - с входом программного управляющего сигнала устройства, а вторым входом - с входом аппаратного, управляющего сигнала устройства, причем выход регистра базы адреса является выходом базы адреса устройства.

Исто 1ники, ийформацйи, принятые во внимание при экспертизе

1; Авторркое свидетельство СССР . .№431516, кл. G Об F 9/20,- 1972.

2, Патент Великобритании №1416002, кл. 64 А, опублик. 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Устройство для формирования адреса | 1979 |

|

SU860072A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

Авторы

Даты

1980-04-15—Публикация

1978-11-22—Подача