(54) УСТРОЙСТВО ДЛЯ СБОРА ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМ АЦИИ

ко второму входу индексного регистра. Первый вход программатора подключен к выходу адресного регистра программатора, а другие входы - к выходам распределителя тактовых импульсов. Выход программатора через тринадцатый элемент И соединен со входом адресного регистра коммутатора, через четырнадцатьш элемент И со вторым входом шестого элемента И, с пятнадцатым элементом И и через шестнадцатый элемент И со вторым входом адресного регистра оперативного запоминающего блока, а соответствующие командные выходы программатора подключены к первому входу адресного регистра программатора, к третьему входу оперативного запоминающего блока, к третьему входу операционного блока и к другим входам всех элементов И.

Недостатком этого устройства является возможность больших разрьшов в процедуре сбора информации от телеметрических датчиков, вызванных проведением сеансов вьшода накопленной информации в капал связи, длительность которых при использовании канала связи с малой пропускной способностью может быть весьма велика. При этом возможна потеря информации о кратковременных процессах, регистрируемых теми или иными датчиками, при совпадении их по времени с сгансами передачи.

Целью изобретения является расширение функциональных возможностей устройства.

Эта цель достигается тем, что в предложенное устройство введены буферный регистр, индикатор разрешения передачи группа элементов И и инвертор. Объединенные выходы первого, шестого и пятнадцатого элементов И через семнадцатый элемент И подключены ко второму входу адресного регистра программатора и через восемнадцатый элемент И ко входу буферного регистра, выход которого через девятнадцатьш элемент И соединен с третьим входом адресного регистра программатора, выход индикатора разрешения передачи подключен к первому входу двадцатого элемента И, второй вход которого соединен с выходом распределителя тактовых импульсов, третий вход - с соответствующим выходом программатора, а выход двадцатого элемента И подключен к четвертому входу адресного регистра программатора, через восемнадцатый элемент И ко входу буферного регистра и через последовательно соединенные инвертор семнадцатый элемент И ко второму входу адресного регистра программатора. Вход индикатора разрешения передачи и второй вход девятнадцатого элемента И соединены с соответствующими командными выходами программатора.

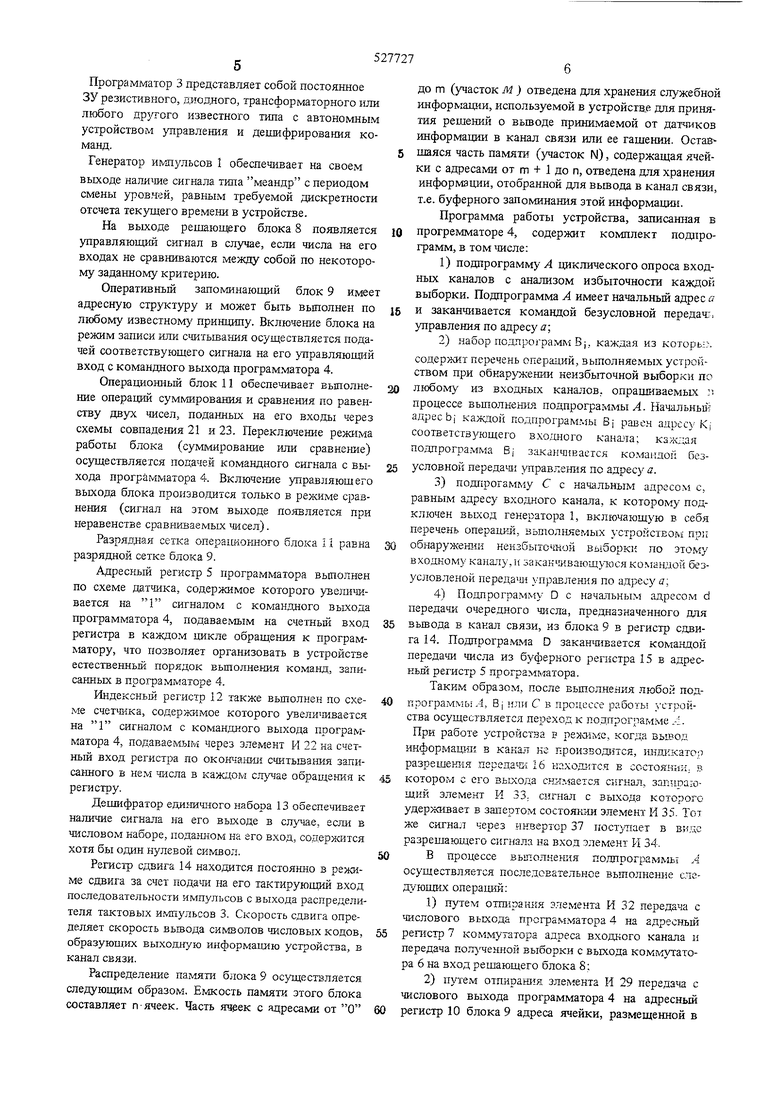

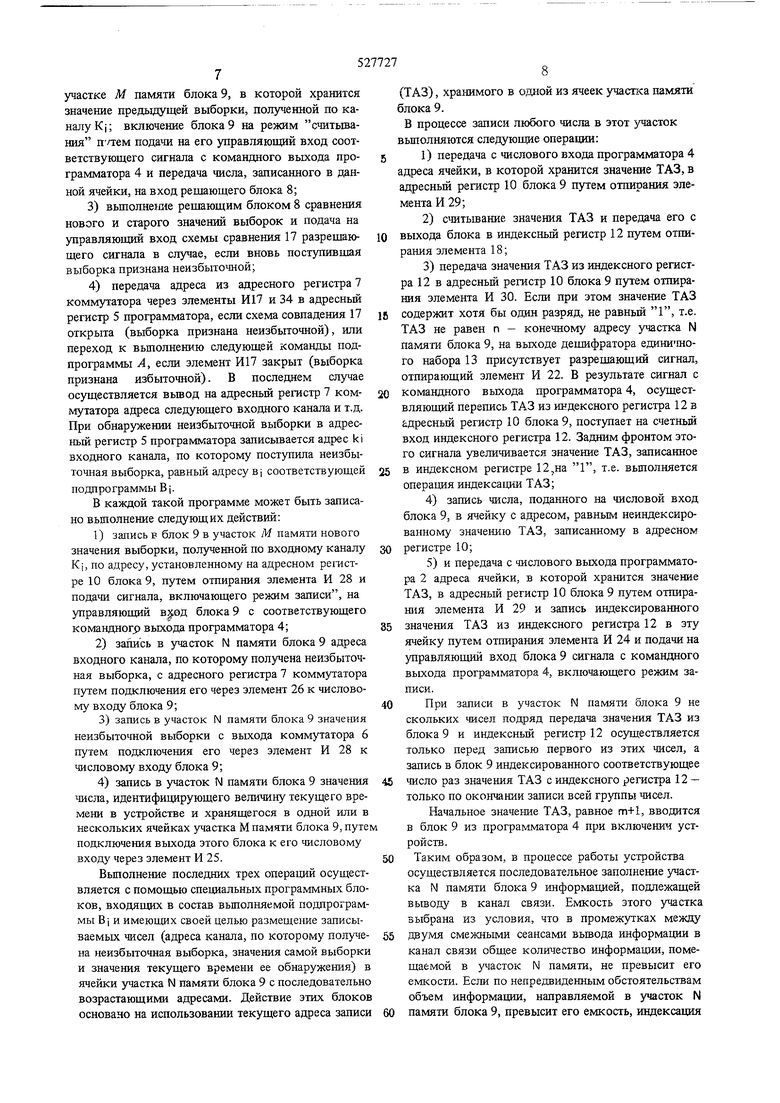

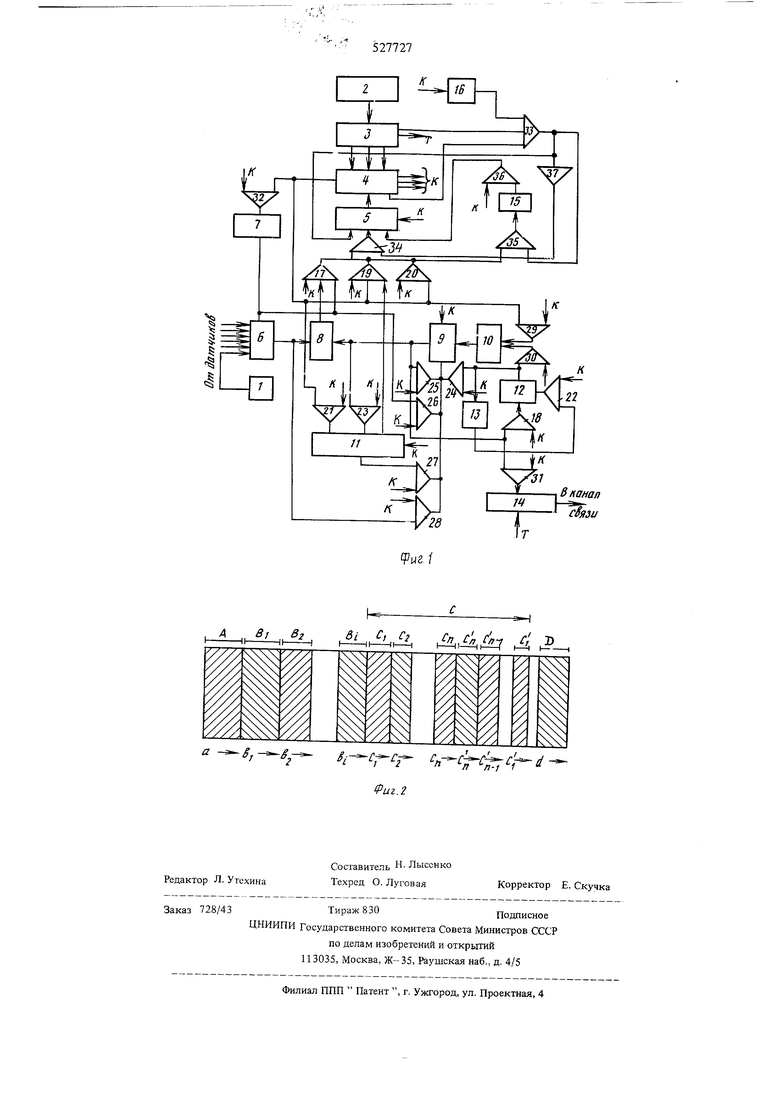

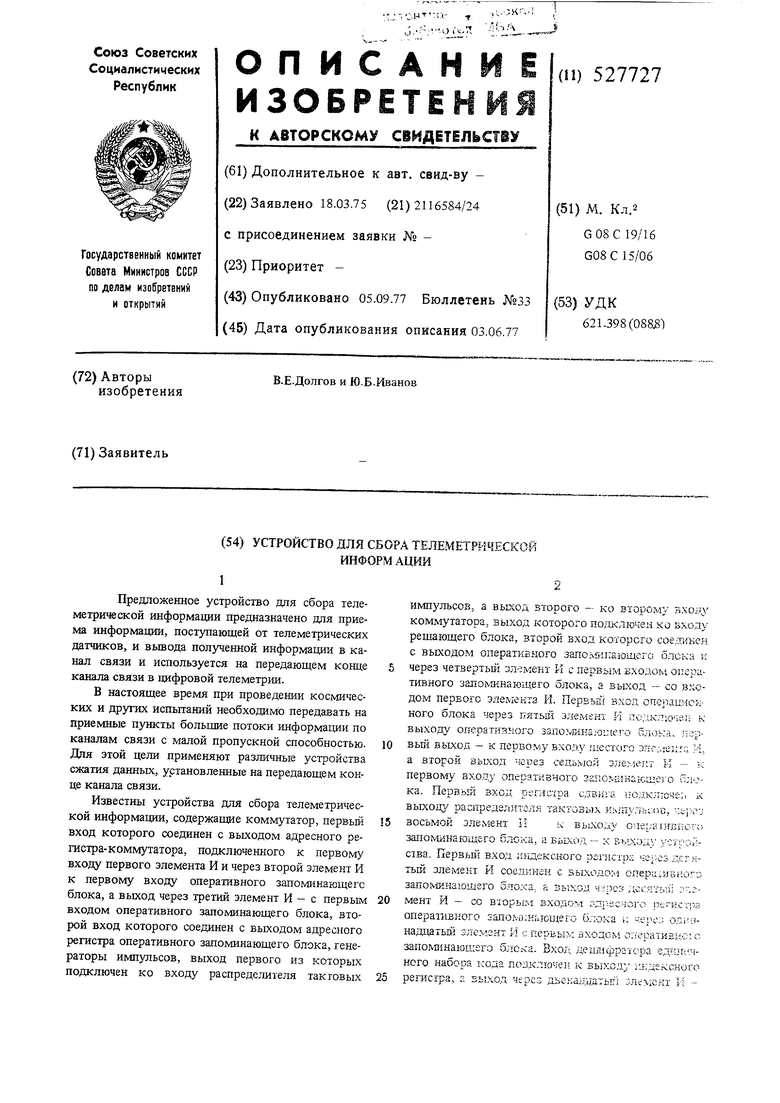

На фиг. 1 представлена схема устройства; на фиг. 2 - структура построения программы работы устройства.

Устройство содержит генераторы импульсов 1 и 2, распределитель тактовых импульсов 3, программатор 4, адресный регистр 5 программатора, коммутатор входных каналов 6, адресный регистр 7 коммутатора, решающий блок 8, оперативньш запоминающий блок 9, адресньш регистр 10 оперативного запоминающего блока, оперативный блок, индексньш регистр 12, дешифратор единичного набора кода 13, регистр сдвига 12, буферный регистр 15, инидкатор разрешения передачи 16, элементы И 17-36 и инвертор 37.

Выход генератора импульсов 2 через распределитель тактовых импульсов 3 подключен к программатору 4, числовой выход которого через элементы И 32, 21 и 29 подключен соответственно к адресному регистру 7 коммутатора, одному из входов оперативного блока 11 и адресному регистру 10 оперативного запоминающего блока, а также через элементы И 19 и 20 и через элементы И 34 и 35 соответственно к входам регистров 5 и 15.

Командные выходы программатора 4 подключены к управляющим входам элементов И 17-32, 36 ,к управляющим входам блока 9, оперативного блока 11, и:шдкатора разрешения передачи 16 и к счетному входу адресного регистра 5 программатора (на фиг. 1 эти связи обозначены буквой /О

Выход разряда хранения признака прерьшания программатора 4 через элемент И 33 подключен к установочному входу адресного регистра программатора, к входу элемента И 35 и через инвертор 37 ко входу элемента И 34.

Один из выходов распределителя тактовых импульсов 3 подключен к тактирующему входу регистра сдвига 14 (связь на фиг. 1 обозначена буквой J), а другой - к одному из входов элемента И 33.

Выход коммутатора 6 подключен к одному из входов решающего блока 8 и через элемент И 28 к числовому входу блока 9. Выход решающего блока 8 через элементы И 17, 34 и 35 подключен соответственно к регистрам 5 и 15.

Выход блока 9 подключен к другому входу решающего блока 8 и через элементы И 25, 23, 18 и 31 соответственно к числовому входу этого блока, одному из входов операционного блока 11, индексному регистру 12 и регистру сдвига 14. Числовой выход операционного блока 11 через элемент И 27 подключен к числовому входу блока 9, управляющий выход - к элементу И 19.

Выход адресного регистра коммутатора через элемент И 26 подключен к числовому входу блока 9.

Выход индексного регистра 12 подключен к дешифратору единичного набора 13 и через элементы И 24 и 30 соответственно к числовому входу блока 9 и адресному регистру 10 этого блока.

Выход дешифратора единичного набора 13 через элемент И 22 подключен к счетному входу индексного регистра 12.

Выход регистра сдвига 14 подключен к выходу устройства. Выход буферного регистра 15 через элемент И 36 подключен ко входу адресного регистра 5 программатора.

Программатор 3 представляет собой постоянное ЗУ резистивного, диодного, трансформаторного или любого другого известного типа с автономным устройством управления и дешифрирования команд.

Генератор и лпyльcoв I обеспечивает на своем

выходе сигнала типа меандр с периодом смены уровней, равным требуемой дискретности отсчета текущего времени в устройстве.

На выходе решающего блока 8 появляется управляющий сигнал в случае, если числа на его входах не сравниваются между собой по некоторому заданному критерию.

Оперативньш запоминающий блок 9 имеет адресную структуру и может быть вьшолнен по любому известном принщшу. Включение блока на режим записи или считывания осуществляется подачей соответствующего сигнала на его управляющий вход с командного выхода программатора 4.

Операционный блок 11 обеспечивает вьшолнение операщш суммирования и сравнения по равенству двух чисел, поданных на его входы через схемы совпадения 21 и 23. Переключение режима работы блока (суммирование или сравнение) осуществляется подачей командного сигнала с выхода программатора 4. Включение управляющего выходд блока производится только в рейшме сравнения (сигнал на этом выходе появляется при неравенстве сравьшваемых чисел).

Разрядная сетка операгшонного блока i i равна разрядной сетке блока 9.

Адресньш регистр 5 программатора вьшолнен по схеме датчика, содержимое которого увеличивается на 1 сигналом с командного выхода программатора 4, подаваемым на счетный вход регистра в каждом цикле обращения к программатору, что позволяет организовать в устройстве естественный порядок вьшолнения команд, записанных в программаторе 4.

Индексный регистр 12 также вьшолнен по схеме счетчика, содержимое которого увеличивается на 1 сигналом с командного выхода программатора 4, подаваемым через элемент И 22 на счетный вход регистра по окончании считывания записанного в нем числа в каждом случае обращения к регистру.

Дешифратор единичного набора 13 обеспечивает наличие сигнала на его выходе в слу-чае, если в числовом наборе, на его вход, содержится хотя бы один нулевой символ.

Регистр сдвига 14 находится постоянно в режиме сдвига за счет пода1ш на его тактирующий вход последовательности импульсов с выхода распределителя тактовых импульсов 3. Скорость сдвига определяет скорость вьшода символов числовых кодов, образующих выходную информащ ю устройства, в канал связи.

Распределение памяти блока 9 осуществляется следующим образом. Емкость памяти этого блока составляет п-ячеек. Часть яарек с адресами от О

до m (участок М ) отведена для хранения служебной информации, используемой в устройств.е для принятия решений о вьшоде принимаемой от датчиков информации в канал связи или ее гашении. Остав щаяся часть памяти (участок N), содержащая ячейки с адресами от m + 1 до п, отведена для хранения информации, отобранной для вьшода в канал связи, т.е. буферного запоминания этой информации.

Программа работы устройства, записанная в прогремматоре 4, содержит комплект подпрограмм, в том числе:

1)подпрограмму Л циклического опроса входных каналов с анализом избыточности каждой выборки. Подпрограмма А имеет начальньш адрес а и заканчивается командой безусловной передач, управления по адресу а;

2)набор подпрограмм ВJ, каждая из которь;.:-.

содержит перечень операций, выполняемых устройством при обнар}окешж неизбыточной выборки по любому из входных каналов, опрашиваемых л процессе вьшолненкя подпрограммы А. Начальньш адрес Ь| каждой подпрограммы В; равен адресу К соответствующего входного канта; каждая подпрограмма Bj заканч 1вается командой безусловной передачи управ.т:ения по адресу а.

3)подпрогамму С с начальным адресом с, равным адресу входного канала, к которому подключен выход генератора 1, включающую в себя перечень операций. вьтол1 яе.мых устройством npi; обнаружеш и неизбыточной выборки по этому входному каналу, н заканчивающуюся командой безусловленой передаш управления по адресуя;

4)Подпрограмму D с начальным адресом d передачи очере.дного , предназначенного д;тя вьшода в канал связи, из блока 9 в регистр сдвига 14. Подпрогра.мма D заканчивается командой передачи числа из буферного регистра 15 в адресный регистр 5 программатора.

Таким образом, после вьшолнения любой подпрогра., Bj или С в процессе работы устройства осуществляется переход к подпрограмме .-1. При работе устройства в режиме, когда вьшод информацш; в канал кг произБОД11Тся, индикатор разрешени.ч передав 16 находится в состоянии; в котором с его выхода сни.{ается сигнал, залирающий элемент И 33; сигнал с выхода которого удерживает в запертом состоя1О1и элемент И 35. Тот же сигна.т через инвертор 37 поступает в виде разрещающего сигнала на вход элемент И 34.

В процессе зьколнения подпрограммы А осуществляется последовательное вьшолнение следующих операщж:

1)путем отпирания элемента И 32 передача с числового выхода npoi-paMMaTopa 4 на адресный penicTp 7 ком.мутатора адреса входного канала и передача пол ченной выборки с выхода коммутатора 6 на вход решающего блока 8;

2)путем отпирашя элемента И 29 передача с числового выхода программатора 4 на адресный регистр 10 блока 9 адреса ячейки, размещенной в

участке М памяти блока 9, в которой хранится значение предыдущей выборки, полученной по каналу KJ; включение блока 9 на режим считьюания П/тем подачи на его управляющий вход соответствующего сигнала с командного выхода программатора 4 и передача числа, записанного в данной ячейки, на вход решающего блока 8;

3)вьшолне1ше рептющим блоком 8 сравнения нового и старого значений выборок и подача на управляющий вход схемы сравнения 17 разрешающего сигнала в случае, если вновь постзшившая выборка признана неизбыточной;

4)передача адреса из адресного регистра 7 коммутатора через элементы И17 и 34 в адресньш регистр 5 программатора, если схема совпадения 17 открыта (выборка признана неизбыточной), или переход к вьшолнению следующей команды подпрограммы А, если элемент И17 закрыт (выборка признана избыточной). В последнем случае осуществляется вьшод па адресньш регистр 7 коммутатора адреса следующего входного канала и т.д. При обнаружении неизбыточной выборки в адресный регистр 5 программатора записывается адрес ki входного канала, по которому поступила неизбыточпая выборка, равньш адресу в j соответствующей подпрограммы Bj.

В каждой такой программе может быть записано вьшолнение следующих действий:

1)запись в блок 9 в участок М памяти нового значения выборки, полученной по входному каналу Kj, по адресу, установленному на адресном регистре 10 блока 9, путем отпирания элемента И 28 и подачи сигнала, включающего режим записи, па управляющий блока 9 с соответствующего командного выхода программатора 4;

2)запись в участок N памяти блока 9 адреса входного канала, по которому получена неизбыточная выборка, с адресного регистра 7 коммутатора путем подключения его через элемент 26 к чисповому входу блока 9;

3)запись в участок N памяти блока 9 значения неизбыто1шой выборки с выхода коммутатора 6 путем подключения его через элемент И 28 к числовому входу блока 9;

4)запись в участок N памяти блока 9 значения числа, идентифицирующего величину текущего времени в устройстве и хранящегося в одной или в нескольких ячейках участка М памяти блока 9, путе подключения выхода этого блока к его числовому входу через элемент И 25.

Выполнение последних трех операщ1Й осуществляется с помощью спещ1альных nporpaMiviHbix блоков, входящих в состав вьшолняемой подпрограммы Bi и имеющих своей целью размещение записываемых чисел (адреса канала, по которому получена неизбыточная выборка, значения самой выборки и значения текущего времени ее обнаружения) в ячейки участка N памяти блока 9 с последовательно возрастающими адресами. Действие этих блоков основано на использовании текущего адреса записи

(ТАЗ), хранимого в одной из ячеек участка памяти блока 9.

В процессе записи любого числа в этот участок вьшолняются следующие операции:

1)передача с числового входа программатора 4 адреса ячейки, в которой хранится значение ТАЗ, в адресньш регистр 10 блока 9 путем отпирания элемента И 29;

2)считывание значения ТАЗ и передача его с выхода блока в индексньш регистр 12 путем отпирания элемента 18;

3)передача значения ТАЗ из индексного регистра 12 в адресньш регистр 10 блока 9 путем отпирания элемента И 30. Если при этом значение ТАЗ содержит хотя бы один разряд, не равный 1, т.е. ТАЗ не равен п - конечному адресу участка N памяти блока 9, на вьтоде дешифратора единишого набора 13 присутствует разрешающий сигнал, отпирающий элемент И 22. В результате сигнал с командного выхода программатора 4, осуществляюпщй перепись ТАЗ из индексного регистра 12 в адресньш регистр 10 блока 9, поступает на счетный вход индексного регистра 12. Задним фронтом этого сигнала увеличивается значение ТАЗ, записанное в индексном регистре 12,на 1, т.е. вьшолняется операпия индексации ТАЗ;

4)запись числа, поданного па числовой вход блока 9, в ячейку с адресом, равным неиндексированпому значению ТАЗ, записанному в адресном регистре 10;

5)и передача с числового выхода программатора 2 адреса ячейки, в которой хранится значение ТАЗ, в адресный регистр 10 блока 9 путем отпирания элемента И 29 и запись индексированного значения ТАЗ из индексного регистра 12 в эту ячейку путем отпирания элемента И 24 к подачи на управляющий вход блока 9 сигнала с командного выхода программатора 4, включающего режим записи.

При записи в участок N памяти блока 9 не скольких чисел подряд передача значения ТАЗ из блока 9 и индексный регистр 12 осзтцествляется только перед загшсью первого из этих чисел, а запись в блок 9 индексированного соответствующее число раз значения ТАЗ с индексного регистра 12 - только по окончании записи всей группы чисел.

Начальное значение ТАЗ, равное т+1, вводится в блок 9 из программатора 4 при включении устройств.

Таким образом, в процессе работы устройства осуществляется последовательное заполнение участка N памяти блока 9 информацией, подлежащей вьшоду в канал связи. Емкость этого участка выбрана из условия, что в промежутках между двумя смежными сеансами вьшода информации в канал связи общее количество информации, помещаемой в участок N памяти, не превысит его емкости. Ес:г1и по непредвиденным обстоятельствам объем информации, направляемой в участок N памяти блока 9, превысит его емкость, индексация ТАЗ прекращается как только его значение станет равным значению п, т.е. содержащим единицы во всех разрядах. При записи такого значения ТАЗ в индексный регистр 12 на выходе дещифратора единичногб набора 13 появляется сигнал, запирающий элемент И 22 и исключающий тем самым прохождение сигнала с командного выхода программатора 4 в момент перезаписи значения ТАЗ из индексного регистра 12 в адресньш регистр 10 на счетный вход индексного регистра 12. При этом индексация ТАЗ прекращается, и запись всей последующей информации производится в ячейку с адресом п блока 9. Таким образом, исключается искажение информации, хранящейся в участки М памяти блока 9, в случае переполнения участка N за счет присвоения ТАЗ значений, соответствующих участку М. В процессе выполнения подпрограммы В| могут быть вьшолнены следующие операции: 1) последовательная передача с числового выхода программатора 4 адресов входных каналов, по которым должен быть произведен дополнительный сбор информации, на адресньш регистр 7 коммутатора путем отпирания элемента 32 и записи полученных значения выборок с выхода коммутатора 6 в зчасток N памяти блока 9 по ТАЗ; 2) задание времени проведения очередных измерений по любому входному каналу путем прибавления к числу, индентифицирующему значение текущего времени, хранящемуся в участке М памяти блока 9 и вводимому в операдионньш блок 11 через элемент И 23, числа, определяющего требуемую задержку вьшолнения этих измерений по отнощению к моменту получе1ш.к данной неизбыточной выборки, выраженную в единицах отсчета текущего времени, вводимого в операционный блок 11с числового выхода программатора 4 путем отпирания элемента И 21, и последующей записи результатов суммирования через элемент И 27 в отведенные для этого ячейки участка М памяти бло ка 9, адреса которых через элемент И 29 предзарительно введены в адресньй регистр 10 этого блока с числового выхода программатора 4. Каждая программа ВI заканчивается выполнением команды безусловной передачи управления по адресу А, вьшолняемой путем передачи значения адреса а с числового выхода программатора 4 через элементы И 20, и 34 на адресньш регистр 5 программатора. В процессе работы устройства периодически изменяется сигнал на выходе коммутатора б, к которому подключен выход генератора 1, что воспринимается устройством как получение неизбыточной вьйорки по этому каналу. В этом случае адрес KC с адресного регистра 7 коммутатора передается через элементы И 17 и 34 в адресный регистр 5 программатора и осуществляется переход к вьшолнению подпрограмгупз С. При вьшолнении подпрограммы С осущ ествляется сначала суммирование числа, идентифици рующего значение текущего времени и хранящегося в участке М памяти блока 9, с константой L, вводимой в операционньш блок 11 с числового выхода программатора 4, причем результат суммирования помещается в те же ячейки участка Л/ памяти блока 9. При вьшолнении подарограммы С осуществляются следуюпдие операции: 1)последовательное сравнение чисел, идентифицирующих время вьшолнения измерений по различным входным каналам и записанных в опреде ленных ячейках участка М памяти блока 9, с числом, идентифирующим значение текзтцего времени, путем задания адресов соответствующих ячеек в адресньш регистр 10 блока 9, ввода содержимого этих ячеек в операционный блок 11 и задания режима сравнгжя в этот пло:; сигналом с командного выхода прогрямг.;аго,а -:. 2)при равенстве глгчпгг.кэяемьтх Ш1сел (на управляющем выходе CliepauiivKLrtOj о о/юка и -запрещаюидай сигнал li cxcivu со1;лад;;1й1й 19 закрыта), продолжается Быгюлпенке игЗ-к - 1ь:з естественном порядке, i.e. aiii;c3ii4i;; i. .; ;:y;e;,i выполняются измерения по reivT каналам, для которых определена необхо,аимость вьгпол -енкя .нзмерени. с записью значений адресов этих кэшшов и нол хенных выборок в участок liuAiHrji блока - ли ГАЗ; 3)при неравенстзе сразнкзаемььч чисе;:; на управляющем вь.сде ouepr;ui;o;:;;, о.,0;-,;.ч I; разрешающл1Й сигкол, j; эле,снт 1-1 i9 откр;.мт). производится лерезачз адреса . ,;,::л;;ьогс ьъ;,од,. программатора 4 через .леме;:,; i-1 9 и З---}.- адресный регастр 5 программатора к переход к дру-сй части программы С (Ks.iipMMep, к сравкгшгю другое; установки, 3airacaRbio;i соотвегсгвеико в Apyriui ячейке }частка MiiarviAiM блока 9. с вислом, идентифицирующим значение текущего времени) „ Если 3 процессе выт1олке5-п-1,с под;1рограммь; А устройство примет избытс п ую Ht iDopKy от KSKoro-либо датчика св}1Дс;.ельс7ву1о;1; ю с is проводящего состоя1У1Я какал;, гнлзк. се вьшолнгжтя подпрограммы С f:-u.c необходимость по зрсмени г НБОла и участке N па.ят11 5лок; О ипфсрмп-л: путем подзч cooTBer;;r5r;oLuCi .-о;-;: ла с кома:шкого выхо л ::л1- -; ливает ицодкатор pcr poiiicHH f яг-лс-д;; ние, при котором HI вылоли -С: ШаюЩИЙ сигнал. ПССГ ь-ЛОГГ:-.:} - :i;;. элемента I-i 3.3. Ка друге;; схо : :л:. л.;, -:: -. :, времени раболъл у;лро:.- /; г :; -ел., ля импульсой 3 ич.стЛг л ;л;;:- ,: , периодом, paBiidjr :;-:.,;.. ЛЛЛ.-Л:-Ч;; выходе Т распрс;л-:л1лл.л-- у ;;л:- -..| рядность регисгу -... ., Л1 начальной часгл 1.Щ1М., а в конечно;; част,: :jjp..;;:;;-;i.;:- л. При зтол- д;Ш1сльнис1ь разрешающей частя сиГс нала выбрана из условия превышения ею длительности вьшолыения любой в отдельности программы А, Bj или Cj.

Таким образом, независимо от того, какой участок программы, записанной в программаторе 4, выполняется в момент возникновения разрешающего сигнала на данном выходе распределителя 3, до его окончания на командных входах программатора 4 возникает набор сигналов, соответствующих командам условной или безусловной передачи управления, отпирающих одну из схем совпадения 17, 19 или 20. Одновременно с этим с выхода разряда хранения признака прерьшагшя программатора 4 снимается разрешаюпшй сигнал, отпирающий элемент И 33. Сигнал с его выхода поступает на установочный вход адресного регистра 5 программатора осуществляет принуоительный ввод в него адреса d и отпирает элемент И 35, в результате чего адрес перехода через соответствующие открытые элементы и 17, 19 или 20 записывается в буферный регистр 15 и через инвертор 37, запирающий элемент И 34,исключает запись того же адреса в адресный регистр 5 программатора.

При очередном обраще1тии к программатору 4 с выхода разряда храпения признака прерывания вновь считывается разрешаюпдай сигнал.

В результате в адресном регистре 5 программатора удерживается адрес d, и работа устройства тормозится в описанном состоя1-ши до возникковения на входе элемента И 33 запрещающего сигнала с выхода распределителя 3. После задирания элемента И 33 разблокируется адресный регистр 5 программатора. Затем устройство вновь переходит в нормальный режим работы с естественным порядком вьшолнегшя команд.

При этом устройство начинает вьшолнять подпрограмму и осуществляются следующие операции:

1) передача с числового выхода программатора 4 адреса ячейки из участка М памяти блока 9, в которой хранится значет1е текущего адреса считываш1Я (ТАС), на адресный регистр 10 через элемент И 29;

2) считьша ше значения ТАС и передача его с выхода блока 9 в индексньш регистр 12 через элемент И 18;

3) перезапись значения ТАС из индексного регистра 12 в адресньш регистр 10 блока 9 с одновременной ивдексадией ТАС в индексном регистре 12 так осуществлялась индексащ{я ТАЗ;

4) считьшание числа из ячейки участка N памяти блока 9 с адресом, равным ТАС, и передача его в регистр сдвига 14 через элемент И 31, после чего это число в последовательном коде выводится из регистра 14 через выход устройства в канал связи.

В качестве начального значения ТАС выбраны как и в случае ТАС, адрес т-И.

Во время вьшода числа из регистра 14 устройство как описано выще осуществляет перезапись ивдексированного значения ТАС в блок 9 и затем

сравнивает его в операционном блоке 11 либо со значением адреса п, вводимым в блок 11 через элемент И 21 из программатора 4, либо со значением ТАЗ, записанным к началу момента вьтода информации из участка N блока 9. Если в результате этого сравнения операционным блоком 11 будет установлено неравенство сравниваемых адресов, означающее, что ТАС в процессе индексации еще не достиг значения ТАЗ или управляющем выходе операционного блока 11 появляется разрешающий сигнал, отпирающий элемент И 19,и в адресньш регистр 5 программатора с числового выхода программатора 4 вписывается адрес конца подпрограммы D, заверщающейся командой передачи управления по адресу, записанному в буферном регистре 15. Последняя осуществляется путем отпирания схемы совпадения 36, после чего устройство переходит к продолжению вьшолнения программы своей работы с того места, где было вьшолнено прерьшание сигнала с выхода разряда хранения признака прерывания программатора 4. Устройство продолжает работу до момента нового совпадения разрешающих сигналов на входах элемента И 33, причем за это время число из регистра сдвига 14 вьшодится в канал связи. Далее наступает повторное прерывание и вьшолнение всех сопровождающих его операций, описанных выще.

Если в очередном цикле вьшолнения подпроrpa.MFvibi D обнаружено равенство ТАС значению ТАЗ или п, па з равляющем выходе операnKOfflioro блока 11 возникает запрещаюпщй сигнал, запирающий элемент И 19. В результате осуществляется переход к очередной команде подпрограммы, D, 3 качестве которой записана команда гаще1ЖЯ индикатора разрещения передачи 16, вьшолняемая путем подачи сигнала с командного выхода программатора 4 на соответствующий вход зтого индикатора. Индикатор 16 переходит в состояние, при котором на его выходе устанавливается запрещающий сигнал, запирающ11Й элемент И 33. При этом вьшолнеш-1е подпрограммы D заканчивается и; устройство переходит к нормальному режиму работы.

Формула изобретения

Устройство для сбора телеметрической информации, содержащее коммутатор, первьш вход которого соединен с выходом адресного регистра коммутатора, подключенного к первому входу первого элемента И и через второй элемент И к первому входу оперативного запоминающего блока, а выход коммутатора через третий элемент И соединен с первым входом оперативного запоминающего блока, второй вход которого соединен с выходом адресного регистра оперативного запоминающего блока, генераторы импульсов, выход первого из которых подключен ко входу распределителя тактовых импульсов, а выход второго - ко второму

входу коммутатора, выход которого подключен ко входу решающего блока, второй вход которого соединен с выходом оперативного заттогушнающего блока и через четвертьш элемент И с первым входом оперативного запоминающего блока, а выход - (Х входом первого элемента И, первый вход операционного блока через пятый элемент И подключен к выходу оперативного запоминающего блока, первый выход операционного блока соединен с первым входом щестого элемента И, а второй выход через седьмой элемент И соединен с первым входом оперативного запоминающего блока, первый вход регистра сдвига подключен к выходу распределителя тактовых импульсов, второй вход через восьмой элемент И - к выходу оперативного запоминающего блока, а выход - к выходу устройства, первый вход индексного регистра через девятый элемент И соединен с выходом оперативного запоминающего блока, а выход через десятый элемент И соединен со вторым входом адресного регистра оперативного запоминающего блока и через одиннадцатьш элемент И с первым входом оперативного запоминающего блока, вход дешифратора единичного набора кода подключен к выходу индексного регистра, а выход через двенадцатый элемент И - ко второму входу индексного регистра, первый вход программатора подключен к выходу адресного регистра программатора, а другие входы - к выходам распределителя тактовых импульсов, выход программатора через тринадцатый элемент И соединен со входом адресного регистра коммутатора, через четырнадцатый элемент И со вторым входом щестого элемента И,

пятнадцатым элементом И и через шестнадцать элемент И - со вторым входом адресного регистра оперативного запоминаюш;его блока, а соответствующие командные выходы программатора подключены к первому входу адресного регистра программатора, к третьему входу оперативного запоминающего блока, к третьему входу операционного блока и к другим входам всех элементов И, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены буферный регистр, индикатор разрешения передачи, группа элементов И и HtmepTOp; объеданенные выходы первого, шестого и пятнадцатого элементов И через семнадцатьш элемент И подключены ко второму входу адресного регистра программатора и через восемнадцатый элемент И ко входу буферного регистра, выход которого через девятнадцатый элемент И сое;л1неь с ретьил; входом адресного регистра программатора; индикатора разрешения передачи подключен к первому входу двадцатого элемента И, второй вход которого соединен с выходом распределителя тактовых импульсов, третий вход - с соответствующим выходом программатора, а выход двадцато1Ч) элемента И подключен к четвертому входу адресного регистра программатора, через восемнадцатый элемент И ко входу буферного регистра и через последовательно соединенные инвертор н семнадцатый элемент И ко второму входу адресного регистра программатора; вход индикатора разрешеш1я передачи и второй вход девятнадцатого элемента И соединены с соответствующими командными входами программатора.

/J7 Т

,S канал

/ Т соязи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1974 |

|

SU521588A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU512484A1 |

| Устройство для передачи телеметрической информации | 1976 |

|

SU652598A1 |

| УСТРОЙСТВО ДЛЯ УПЛОТНЕНИЯ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ | 1974 |

|

SU432566A1 |

| УСТРОЙСТВО ДЛЯ СБОРА ТЕЛЕМЕТРИЧЕСКОЙ ШФОНУ1АЦИИ | 1973 |

|

SU433523A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Авторы

Даты

1976-09-05—Публикация

1975-03-18—Подача