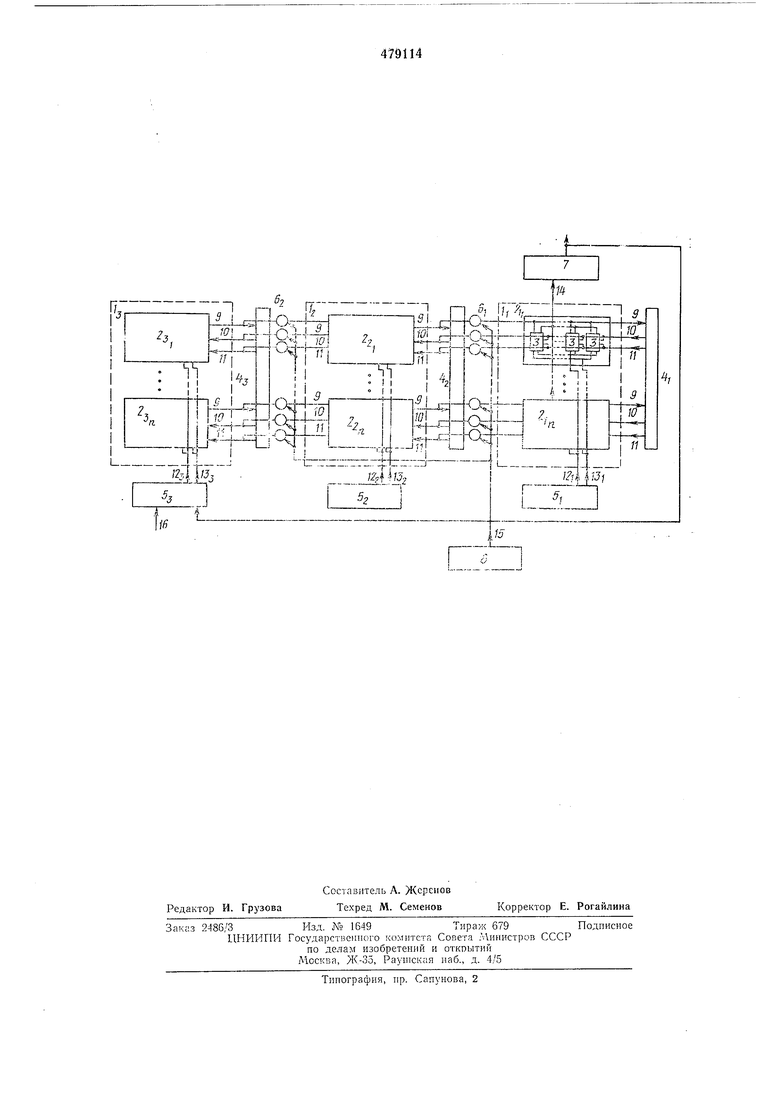

гические схемы, обеспечивающие запись внешней информации в триггер, считывание без разрушения информации и сравнение содержимого триггера с входной информацией. На выходе сравнения элемента 3 вырабатывается единичный сигнал, если на этот разряд наложена маска, или когда информация, содержащаяся в триггере, совпадает с входной информацией, поступающей от одноименного разряда регистра опроса, входящего в состав схемы входного устройства.

Выходы сравнения элементов 3 и входы разрешения записи и разрешения считывания в каждой строке матрицы объединены общими горизонтальными шинами сравнения 9, разрешения записи 10 и разрешения считывания 11 соответственно. Строка считается выбранной, если на шине 9 сравнения этой строки появляется единичный сигнал.

В вертикальном направлении элементы объединены в столбцы шинами опроса записи и считывания.

Работа происходит следующим образом.

По шинам 12i-13з опроса из входных устройств 5i-5з к элементам 3 матрицы подается число, которое содержит признак опроса. По признаку опроса отыскивается (выбирается) строка, содержащая этот признак. При этом из местных устройств 4i-4з управления на шину разрешения записи 10 или разрешения считывания 11 выбранной строки поступает единичный сигнал.

Подавая по шинам опроса и записи из входного устройства в определенной последовательности микропрограммы, составленные из признаков опроса и кодов записи, можно выполнять групповые арифметические и логические операции параллельно над парами чисел, размещенными в отдельных строках матрицы, проводить последовательно по строкам считывание чисел из матрицы в выходной регистр 7 или запись чисел из входного устройства в строки матрицы, осуществлять параллельные пересылки чисел между соседними строками в матрице и т. д.

Структурное моделирование алгоритмов решаемых задач в ассоциативной памяти проводится в два этапа.

На первом этапе отдельные группы строк ассоциативной памяти настраиваются на реализацию заданных алгоритмов. На втором этапе выполняется одновременное вычисление задач в предварительно настроенных (запрограммированных) строках ассоциативной памяти.

Настройка состоит из записи в отдельные строки ассоциативной памяти признаков типа вычислений, обеспечивающих реализацию в этих строках заданного множества операций, определяемого составом алгоритма решаемой в этих строках задачи, а также из записи признаков типа связей, обеспечивающих .пересылки чисел между отдельными строками матриц ассоциативной памяти или между матрицей ассоциативной памяти и внешними устройствами в соответствии с топологией связей схем алгоритмов решаемых задач.

Метод структурного моделирования алгоритмов рещения задач можно проиллюстрировать на примере использования разностных уравнений вида:

(1)

i l

или формул Горнера:

yi 2 yi+i- i+i+ i,i-. (2)

Подбором коэффициентов Oj через выражения (1), (2) можно вычислять интегралы, определять значение элементарных тригонометрических функций и т. д.

Задачи статистической обработки данных, цифровой фильтрации случайных процессов, моделирование импульсных систем и регуляторов и многие другие задачи целиком или по частям могут быть представлены совокупностью уравнений (1) и (2).

Настройка процессора, используемого для решения задач, выраженных через уравнения

(1) и (2), выполняется с учетом того обстоятельства, что матрица Ь используется для ввода массива данных, матрица 12 - для обработки, а матрица li - для вывода массива данных. Поэтому в каждой строке матрицы ввода выделены две зоны элементов: одна - для записи значений входных переменных, другая - для записи признаков «ввода и «имени входной переменной в тех строках, которые должны принять эту переменную.

В каждой строке матрицы вывода также имеются две зоны элементов: одна для записи значений выходной переменной, другая - для записи признаков «вывода и «имени выходной переменной в тех строках, которые

должны передать эту переменную.

В каждой строке матрицы обработки есть несколько зон для записи значений множителя, множимого, произведения (которое затем становится первым слагаемым), второго слагаемого и суммы. Причем, если в /-строку в соответствующие зоны помещены коэффициент иг и переменная Хг, то в соседнюю снизу строку записаны uj+i и Xi+i и т. д. Кроме того, в группы строк, реализующие

выражение (1), заносится признак тип вычисления «1, а в строки, реализующие выражение (2),-признак тип вычисления «О. При этом в крайние сверху и крайние снизу строки каждой группы строк вводятся признаки начала группы и конца группы, запрещающие в

этих строках прием числа от соседней сверху

строки и передачу числа в соседнюю снизу

строку соответственно.

Процесс вычисления задач состоит в том,

что в устройстве параллельно проводятся и циклически повторяются две процедуры: процедура пересылки чисел из матрицы вывода в матрицу ввода и процедура вычислений в матрице обработки. Процедура пересылок состоит в последовательном считывании вычисленных значений выходных переменных к их имен из строк матрицы вывода, помеченных признаком «вывод, через выходной регистр 7 во входное устройство 5з .матрицы 1з- Переменная поступает в регистр записи, а ее имя- в регистр опроса входного устройства. Из входного устройства переменная переписывается за один такт в те строки матрицы ввода, в которых предварительно (в процессе настройки) было занесено имя этой переменной.

Процедура вычислений состоит из последовательного выполнения микропрограмм операций, обеспечивающих вычисление выражений (I) и (2): умиожеиия, сложения и пересылок между соседними строками вычисленной суммы в зону второго слагаемого для выражения (1), а затем в зону множимого для выражения (2). По окончании обеих процедур три соседние матрицы по сигиалу, присутствующему на шине 15 и поступающему из внешнего устройства 8 уиравления, объединяются в одну большую матрицу и вновь вычисленные в зоне обработки (матрица обработки) переменные переписываются в зону вывода (матрица вывода), а вновь поступившие в зону ввода (матрица ввода) переменные - в зону обработки. Затем эти процедуры вновь повторяются. Обе процедуры выполияются в ассоциативновй памяти по микропрограммам, поступающим из внешнего устройства 8 управления, через соответствующие входные устройства .

Каждая из микронрограмм снабжена сиециальными дополнительными признаками, обеспечивающими ее вылолпепие только i, тех строках, которые были предварительно иа иее выстроены, и только после того, как и иих от других строк или извне поступят активные данные. Так, например, по окончании вычислеНИИ в какой-либо строке обработаиные данные становятся иеактивпыми, а активпы.м - результат вычислеиий, который затем пересылается в другую, связанную за счет информации настройкн, строку. Таким образом, в различиых строках ассоциативной памяти реализуется данное подмножество операций и пересылок, а также автоматически обеспечивается управление процессом вычислений и его волиовое распространение по цепочке связанных между собой отдельных строк.

При поступлении на вход 16 устройства нового массива данных процедуры пересылок и обработки временно прерываются и вновь возобновляются носле ввода этого массива в матрицу ввода.

Предмет изобретения

Ассоциативный параллельный процессор, содержащий входное устройство, внешнее устройство управления, местное устройство управления, выходной регистр и матрицу элементов ассоциативной памяти, соответствующие входы и выходы каждого из которых соединены с местным устройством управления общими для каждой строки шинами сравнения, разрешения заииси и разрещения считываиия, с входным устройством общими для каждого столбца шинами опроса и записи и с выходным регистром шинами -считывания, отличающийся тем, что, с целью новышения нроизводительности процессора, в него дополнительно введены ключи, две матрицы элемеитов ассоциативной памяти, соединенные шинами сравнения, разрешения заниси и разрешения счптывания с соответствующими местными устройствами унравлення, а шинами опроса и записи - с соответствующими входиыми устройствами, шины сравнения, разрешеиия записи и разреи еиия считывания одноименных строк соседнИх матриц соединены между собой через ключи, управляющие входы которых подключены к выходу внешнего устройства управления, выход выходного регистра соединен с первым входом одного из введенных входных устройств, второй вход которого подключен к в.ходу процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Однородная вычислительная среда | 1974 |

|

SU618738A1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

| Запоминающий модуль для матричных блоков памяти | 1978 |

|

SU746728A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

Авторы

Даты

1975-07-30—Публикация

1973-03-20—Подача