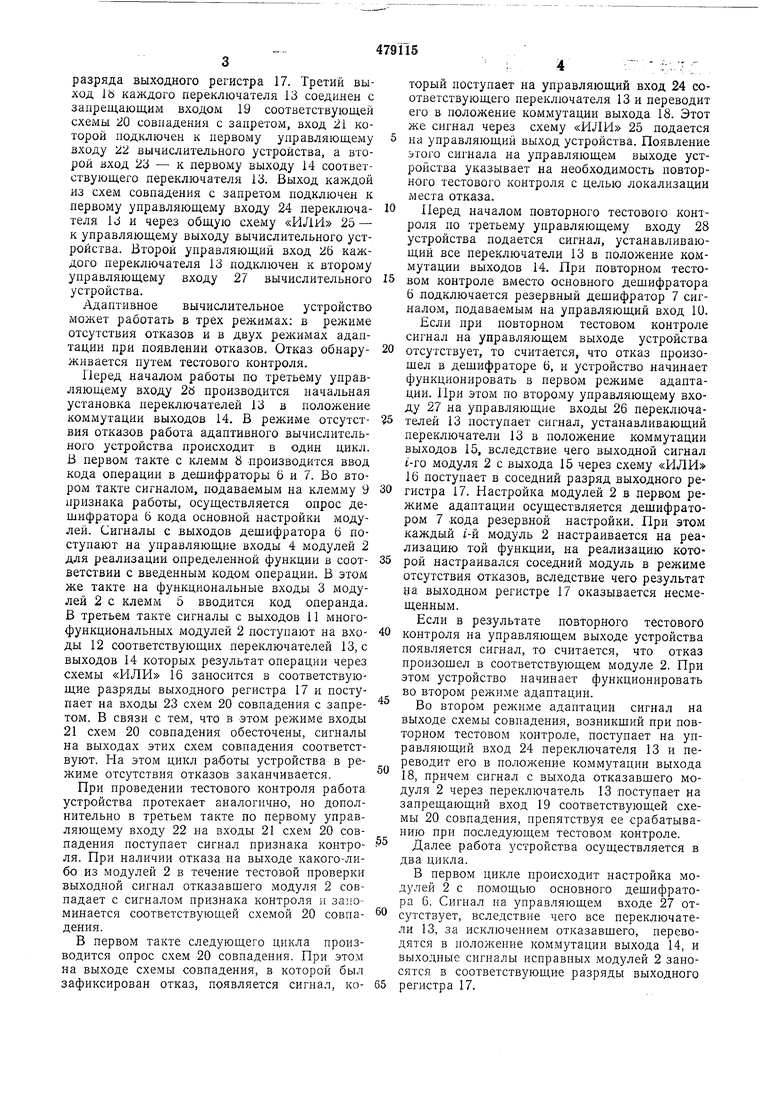

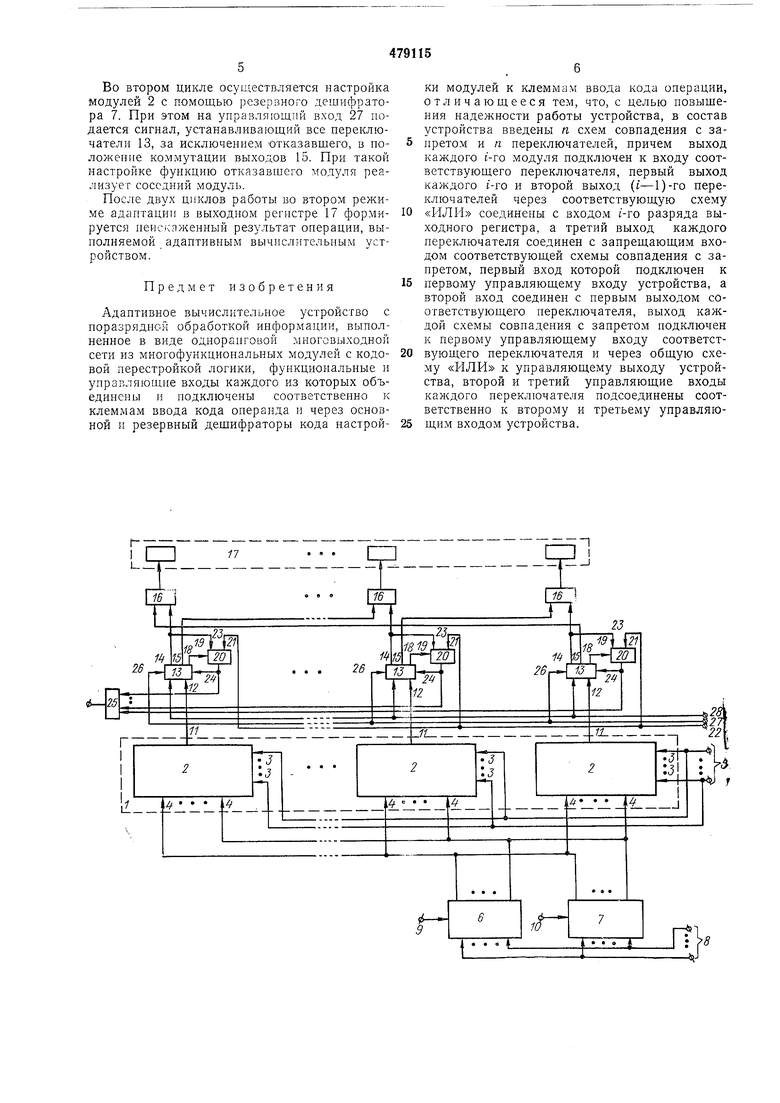

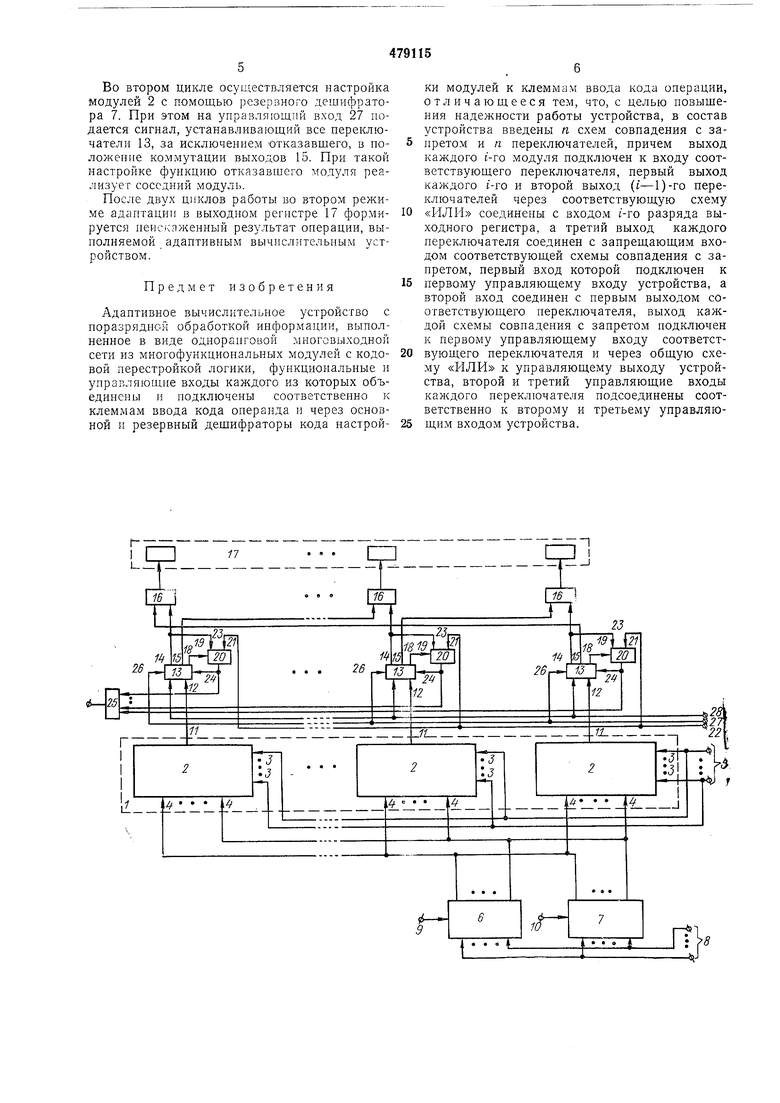

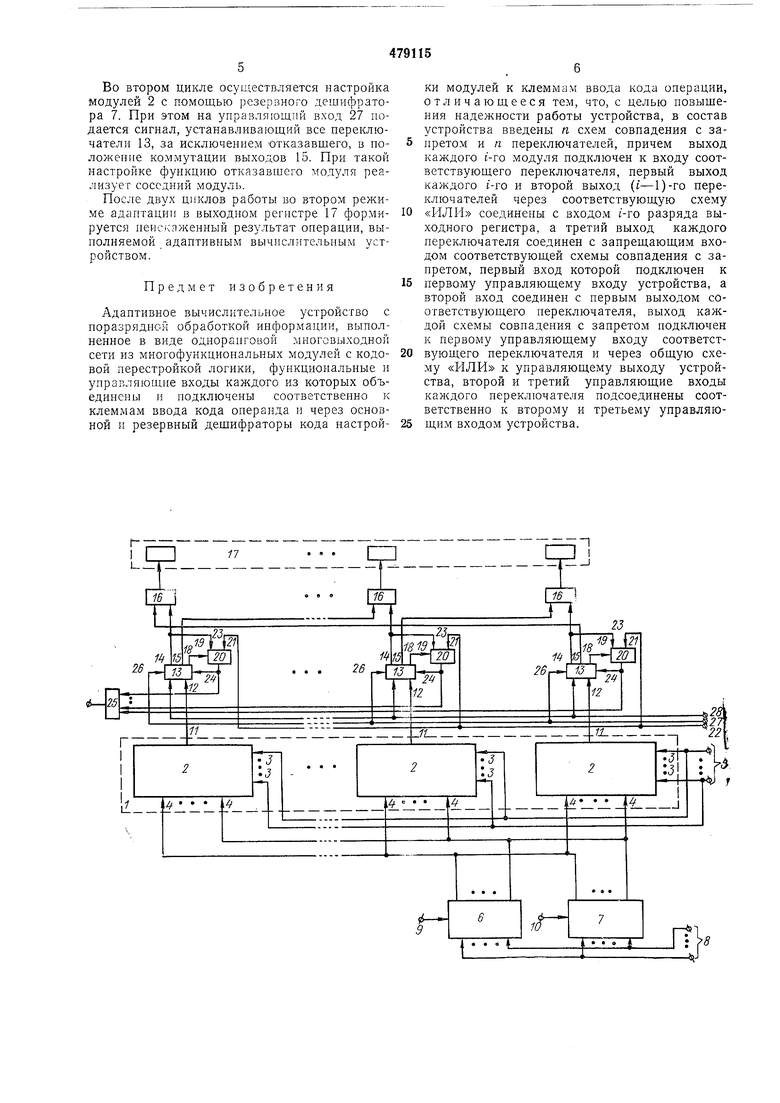

Изобретение относится к области вычисли тельной техники. Известны адаптивные вычислительные устройства, выполненные в виде функционально устойчивых сетей из многофункциональных модулей с кодовой перестройкой логики. Однако такие устройства не обеспечивают коррекции ошибок, связанных с отказом (например, типа обрыв или короткое замыкание) одного или некоторых комбинаций нескольких многофункциональных модулей функционально устойчивой сети. Цель изобретения - повышение надежности работы устройства. Это достигается благодаря тому, что в устройство введены п схем совпадения с запретом и п переключателей на три выхода по числу многофункциональных модулей в сети. Выход каждого f-ro модуля подключен к функциональному входу соответствуюш,его переключателя на три выхода, первый выход -ГО и второй выход (i-1)-го переключателей через соответствующую схему «ИЛИ соединены с входом 1-го разряда выходного регистра, а третий выход каждого переключателя - с запреш,аюш,им входом соответствующей схемы совпадения с запретом, один из входов которой подключен к первому управляющему входу устройства, а второй вход соединен с первым выходом соответствующего переклю чателя. Выход каждой схемы совпадения с запретом подключен к первому управляющему входу соответствующего переключателя и к управляющему выходу устройства, а. второй и третий управляющие входы каждого переключателя подсоединены соответственно к второму и третьему управляющим входам устройства. На чертеже показана структурная схема адаптивного вычислительного устройства с поразрядной обработкой информации. Вычислительное устройство выполнено в виде одноранговой многовыходной сети 1 из многофункциональных модулей 2 с кодовой перестройкой логики. Функциональные 3 и управляющие 4 входы каждого модуля 2 соединены параллельно и подключены к клеммам 5 ввода кода операнда и через соединенные параллельно дешифратор 6 кода основной настройки модулей и дешифратор 7 кода резервной настройки модулей - к клеммам 8 ввода кода операции. Управляющие входы дешифраторов б и 7 соединены с клеммами 9 и 10 признака работы. Выход 11 каждого i-ro многофункционального модуля 2 подключен к входу 12 соответствующего переключателя 13. Первый выход 14 каждого f-ro переключателя 13 и второй выход 15 соседнего с ним переключателя через схему «ИЛИ 16 соединены с входом t-ro

разряда выходного регистра 17. Третий выход 1Ь каждого переключателя 13 соединен с запрещающим входом 19 соответствующей схемы 20 совпадения с запретом, вход 21 которой подключен к первому управляющему входу 22 вычислительного устройства, а второй вход 23 - к первому выходу 14 соответствующего переключателя 13. Выход каждой из схем совпадения с запретом подключен к первому управляющему входу 24 переключателя 13 и через общую схему «ИЛИ 25 - к управляющему выходу вычислительного устройства. Второй управляющий вход 26 каждого переключателя 13 подключен к второму управляющему входу 27 вычислительного устройства.

Адаптивное вычислительное устройство может работать в трех режимах: в режиме отсутствия отказов и в двух режимах адаптации при появлении отказов. Отказ обнаруживается путем тестового контроля.

Перед началом работы по третьему управляющему входу 2й производится начальная установка переключателей 13 в положение коммутации выходов 14. В режиме отсутствия отказов работа адаптивного вычислительного устройства происходит в один цикл. В первом такте с клемм 8 производится ввод кода операции в дешифраторы 6 и 7. Во втором такте сигналом, подаваемым на клемму 9 признака работы, осуществляется опрос дешифратора 6 кода основной настройки модулей. Сигналы с выходов дешифратора b поступают на управляющие входы 4 модулей 2 для реализации определенной функции в соответствии с введенным кодом операции. В этом же такте на функциональные входы 3 модулей 2 с клемм 5 вводится код операнда. В третьем такте сигналы с выходов 11 многофункциональных модулей 2 поступают на входы 12 соответствующих переключателей 13, с выходов 14 которых результат операции через схемы «ИЛИ 16 заносится в соответствующие разряды выходного регистра 17 и поступает на входы 23 схем 20 совпадения с запретом. В связи с тем, что в этом режиме входы 21 схем 20 совпадения обесточены, сигналы на выходах этих схем совпадения соответствуют. На этом цикл работы устройства в режиме отсутствия отказов заканчивается.

При проведении тестового контроля работа устройства протекает аналогично, но дополнительно в третьем такте по первому управляющему входу 22 на входы 21 схем 20 совпадения поступает сигнал признака контроля. При наличии отказа па выходе какого-либо из модулей 2 в течение тестовой проверки выходной сигнал отказавшего модуля 2 совпадает с сигналом признака контроля и запоминается соответствующей схемой 20 совпадения.

В первом такте следующего цикла производится опрос схем 20 совпадения. При этом на выходе схемы совпадения, в которой был зафиксирован отказ, появляется сигнал, который поступает на управляющий вход 24 соответствующего переключателя 13 и переводит его в положение коммутации выхода 18. Этот же сигнал через схему «ИЛИ 25 подается 5 па управляющий выход устройства. Появление этого сигнала на управляющем выходе устройства указывает на необходимость повторного тестового контроля с целью локализации места отказа.

Перед началом повторного тестового контроля по третьему управляющему входу 28 устройства подается сигнал, устанавливающий все переключатели 13 в положение коммутации выходов 14. При повторном тесто5 вом контроле вместо основного дешифратора б .подключается резервный дешифратор 7 сигналом, подаваемым на управляющий вход 10. Если при повторном тестовом контроле сигнал на управляющем выходе устройства

0 отсутствует, то считается, что отказ произошел в дешифраторе 6, и устройство начинает функционировать Б первом режиме адаптации. При этом по второму управляющему входу 27 на управляющие входы 26 переключателей 13 поступает сигнал, устанавливающий переключатели 13 в положение коммутации выходов 15, вследствие чего выходной сигнал t-ro модуля 2 с выхода 15 через схему «ИЛИ 16 поступает в соседний разряд выходного регистра 17. Иастройка модулей 2 в первом режиме адаптации осуществляется дешифратором 7 -кода резервной настройки. При этом каждый i-й модуль 2 настраивается на реализацию той функции, на реализацию кото5 рой настраивался соседний модуль в режиме отсутствия отказов, вследствие чего результат аа выходном регистре 17 оказывается несмещенным. Если в результате повторного тестового

0 контроля на управляющем выходе устройства появляется сигнал, то считается, что отказ произошел в соответствующем модуле 2. При этом устройство начинает функционировать во втором режиме адаптации.

Во втором режиме адаптации сигнал на выходе схемы совпадения, возникший при повторном тестовом контроле, поступает на управляющий вход 24 переключателя 13 и переводит его в положение коммутации выхода 18, причем сигнал с выхода отказавшего модуля 2 через переключатель 13 поступает на запрещающий вход 19 соответствующей схемы 20 совпадения, препятствуя ее срабатыванию при последующем тестовом контроле.

Далее работа устройства осуществляется в два цикла.

В первом цикле происходит настройка модулей 2 с помощью основного дешифратора 6. Сигнал па управляющем входе 27 отсутствует, вследствие чего все переключатели 13, за исключением отказавшего, переводятся в положение коммутации выхода 14, и выходные сигналы исправных модулей 2 заносятся в соответствующие разряды выходного

5 регистра 17.

Во втором цикле осуществляется настройка модулей 2 с помощью резервного дешифратора 7. При этом на управляющий вход 27 подается сигнал, устанавливающий все переключатели 13, за исключением отказавщего, в положение коммутации выходов 15. При такой настройке функцию отказавщего модуля реализует соседний модуль.

После двух циклов работы во втором режиме адаптации в выходном регистре 17 формируется неис1;аженный результат операции, выполняемой адаптивным вычислительным устройством.

Предмет изобретения

Адаптивное вычислительное устройство с поразрядной обработкой информации, выполненное в виде одноранговой многовыходной сети из многофункциональных модулей с кодовой перестройкой логики, функциональные и управляющие входы каждого из которых объединены и подключены соответственно к клеммам ввода кода операнда и через основной и резервный дещифраторы кода настройки модулей к клеммам ввода кода операции, отличающееся тем, что, с целью повышения надежности работы устройства, в состав устройства введены п схем совпадения с запретом и п переключателей, причем выход каждого г-го модуля подключен к входу соответствующего переключателя, первый выход каждого t-ro и второй выход (i-1)-го переключателей через соответствующую схему

«ИЛИ соединены с входом t-ro разряда выходного регистра, а третий выход каждого переключателя соединен с запрещающим входом соответствующей схемы совпадения с запретом, первый вход которой подключен к

первому управляющему входу устройства, а второй вход соединен с первым выходом соответствующего переключателя, выход каж.цой схемы совпадения с запретом подключен к первому управляющему входу соответствующего переключателя и через общую схему «ИЛИ к управляющему выходу устройства, второй и третий управляющие входы каждого переключателя подсоединены соответственно к второму и третьему управляющим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная среда | 1973 |

|

SU443382A1 |

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| Устройство распределения заданий процессорам | 1986 |

|

SU1327106A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

Авторы

Даты

1975-07-30—Публикация

1973-06-28—Подача