to

Од

ел

-vl

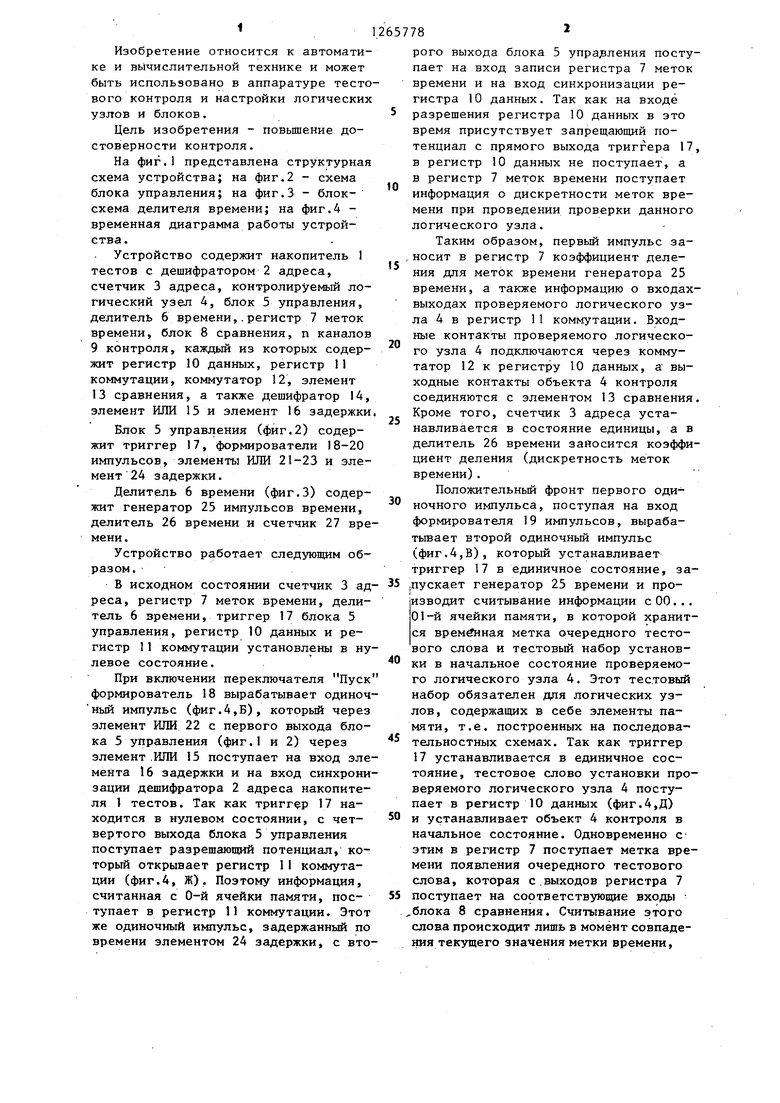

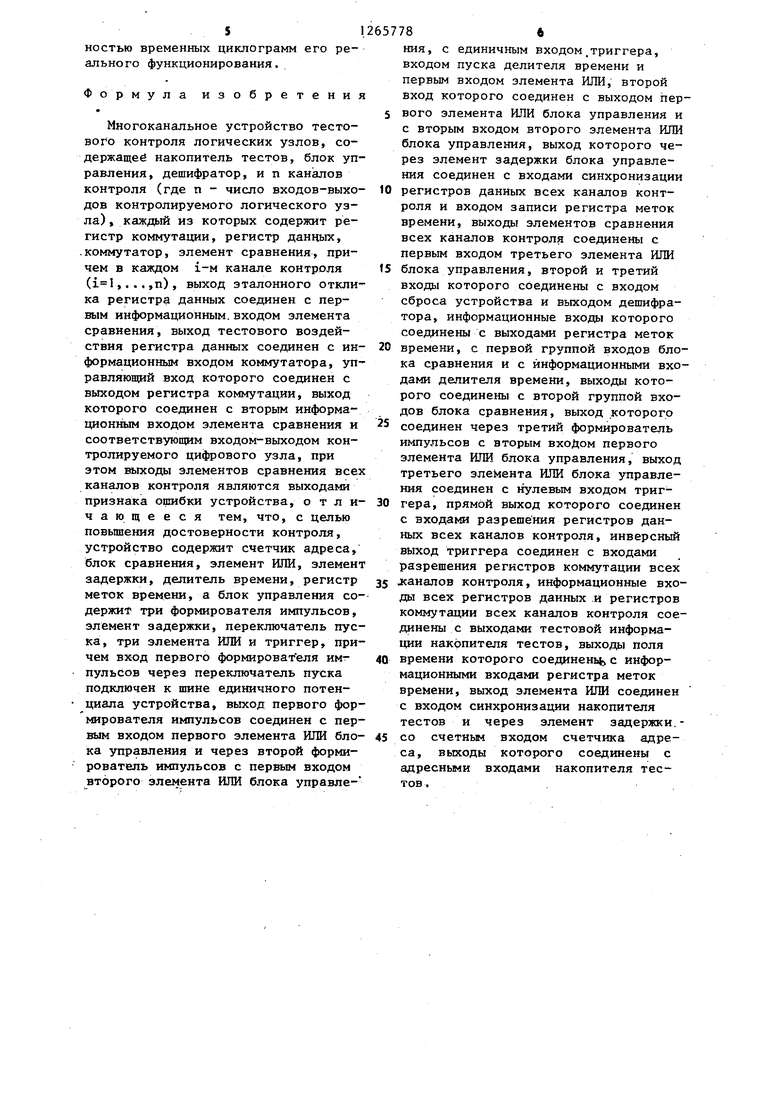

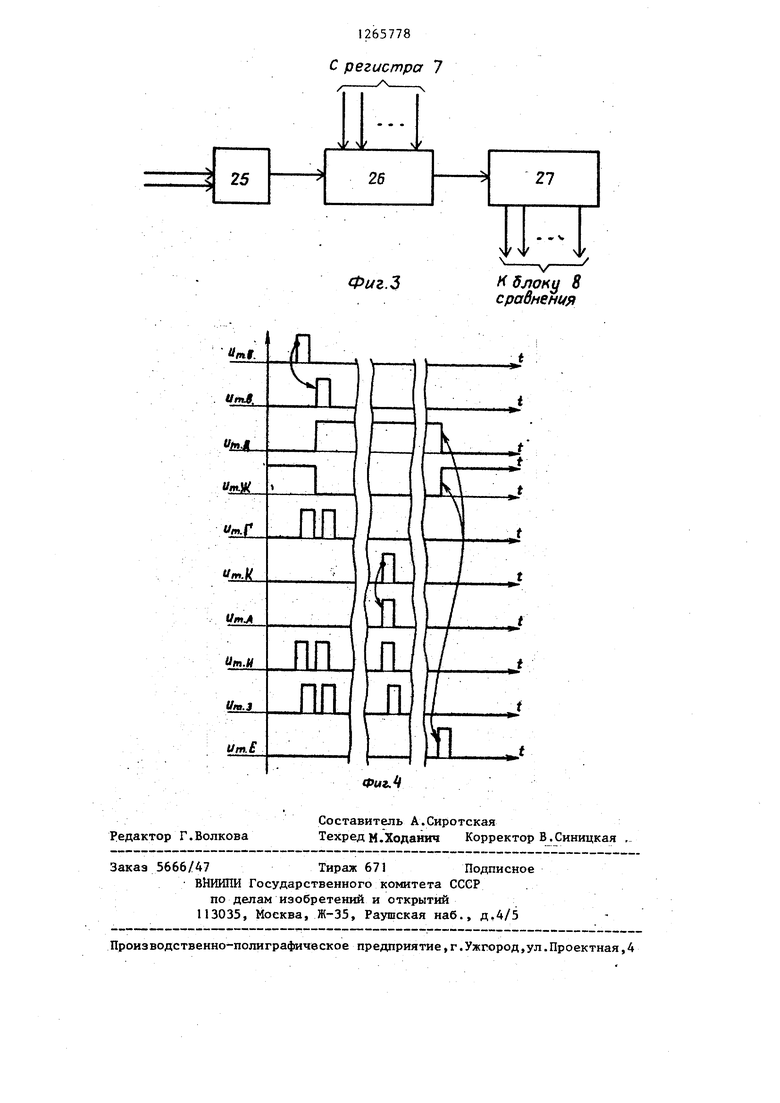

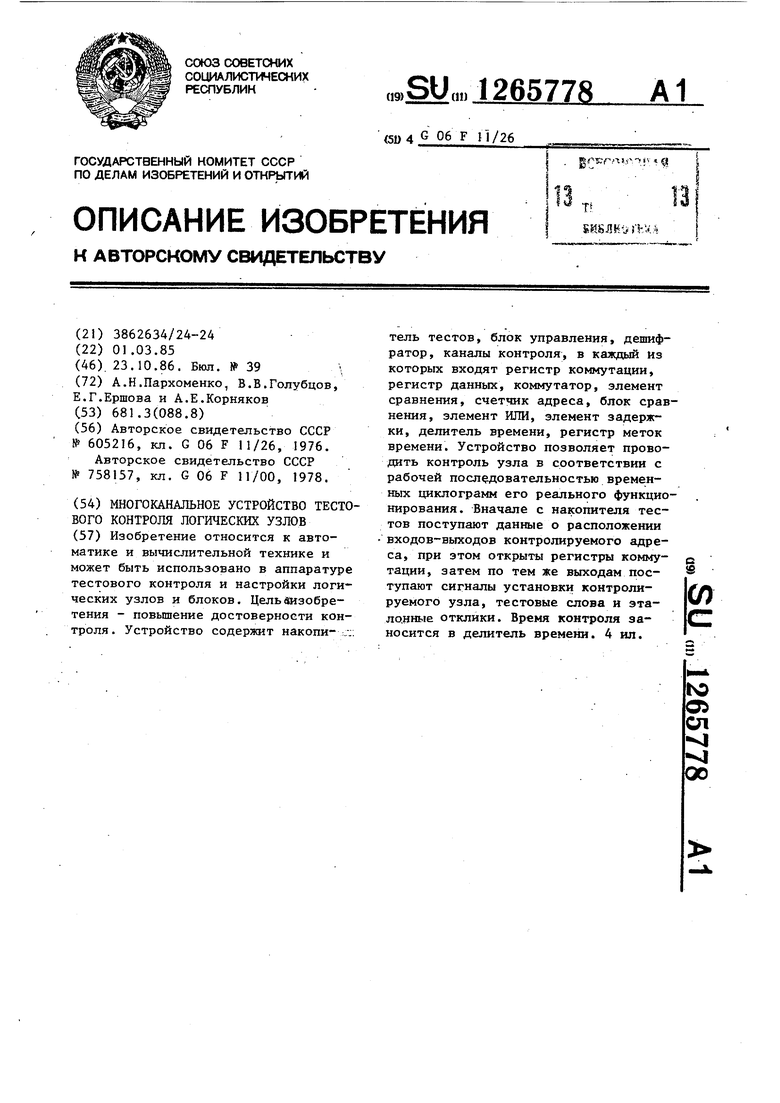

00 Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре тесто вого контроля и настройки логических узлов и блоков. Цель изобретения - повьшение достоверности контроля. На фиг.1 представлена структурная схема устройства; на фиг.2 - схема блока управления; на фиг.З - блоксхема делителя времени; на фиг.4 временная диаграмма работы устройства. Устройство содержит накопитель 1 тестов с дешифратором 2 адреса, счетчик 3 адреса, контролируемый логический узел 4, блок 5 управления, делитель 6 времени,.регистр 7 меток времени, блок 8 сравнения, п каналов 9 контроля, каждый из которых содержит регистр 10 данных, регистр 11 коммутации, коммутатор 12, элемент 13 сравнения, а также дешифратор 14, элемент ИЛИ 15 и элемент 16 задержки Блок 5 управления (фиг.2) содержит триггер 17, формирователи 18-20 импульсов, элементы ИЛИ 21-23 и элемент 24 задержки. Делитель 6 времени (фиг.З) содержит генератор 25 импульсов времени, делитель 26 времени и счетчик 27 вре мени . Устройство работает следующим образом. В исходном состоянии счетчик 3 ад реса, регистр 7 меток времени, делитель 6 времени, триггер 17 блока 5 управления, регистр 10 данных и регистр 11 коммутации установлены в ну левое состояние. При включении переключателя Пуск формирователь 18 вырабатывает одиноч ный импульс (фиг.4,В), который через элемент ИЛИ 22 с первого выхода блока 5 управления (фиг.1 и 2) через элемент .ИЛИ 15 поступает на вход эле мента 16 задержки и на вход синхрони зации дешифратора 2 адреса накопителя 1 тестов. Так как триггер 17 находится в нулевом состоянии, с четвертого выхода блока 5 управления поступает разрешающий потенциал, который открывает регистр 11 коммутации (фиг.А, Ж). Поэтому информация, считанная с 0-й ячейки памяти, поступает в регистр 11 коммутации. Этот же одиночный импульс, задержанный по времени элементом 24 задержки, с вто 78 рого выхода блока 5 управления поступает на вход записи регистра 7 меток времени и на вход синхронизации регистра 10 данных. Так как на входе разрешения регистра 10 данных в это время присутствует запрещающий потенциал с прямого выхода триггера 17, в регистр 10 данных не поступает, а в регистр 7 меток времени поступает информация о дискретности меток времени при проведении проверки данного логического узла. Таким образом, первый импульс заносит в регистр 7 коэффициент деления для меток времени генератора 25 времени, а также информацию о входахвыходах проверяемого логического узла 4 в регистр 11 коммутации. Входные контакты проверяемого логического узла 4 подключаются через коммутатор 12 к регистру 10 данных, а выходные контакты объекта 4 контроля соединяются с элементом 13 сравнения. Кроме того, счетчик 3 адреса устанавливается в состояние единицы, а в делитель 26 времени заносится коэффициент деления (дискретность меток времени). Положительный фронт первого одиночного импульса, поступая на вход формирователя 19 импульсов, вырабатьшает второй одиночный импульс (фиг.4,в), который устанавливает триггер 17 в единичное состояние, за.пускает генератор 25 времени и производит считывание информации с 00... 01-й ячейки памяти, в которой хранится времА1ная метка очередного тестового слова и тестовый набор установки в начальное состояние проверяемого логического узла 4. Этот тестовый набор обязателен для логических узлов, содержащих в себе элементы памяти, т.е. построенных на последовательностных схемах. Так как триггер 17 устанавливается в единичное состояние, тестовое слово установки проверяемого логического узла 4 поступает в регистр 10 данных (фиг.4,Д) и устанавливает объект 4 контроля в начальное состояние. Одновременно с этим в регистр 7 поступает метка времени появления очередного тестового слова, которая с.выходов регистра 7 поступает на сортветствующие входы блока 8 сравнения. Считывание этого слова происходит лишь в момент совпадения текущего значения метки времени.

формируемой в счетчике 27 времени,со значением метки времени, находящейся в регистре 7 меток времени.Задержанный элементом 6 задержки второй одиночный импульс устанавливает счетчик 3 адреса в состояние 00...10 т.е. подготавливает считывание содержимого 000...10-й ячейки памяти.

При совпадении текущего времени с меткой времени очередного тестового слова на выходе блока 8 сравнения появляется импульс (фиг.4, К), который, поступая на вход формирователя 20 блока 5 управления, вырабатывает импульс (фиг.4,А), который с первого и второго выходов блока 5 управления поступает на дешифратор 2 адреса (фиг.4,И), на счетчик 3 адреса (фиг.4,3) и на входы синхронизации регистра 10 данных. При этом происходит считывание тестового слова с ячейки памяти 000...10 в регистр 7 меток времени и регистр 10 данных, счетчик 3 адреса с определенной задержкой (фиг.4,3) принимает значение 000...11, на входные контакты контролируемого логического узла 4 подаются через коммутаторы 12 входные воздействия, мгновенные выходные реакции контролируемого лог ического узла 4 сравниваются на элементе 13 сравнения с их эталонными значениями которые записаны в регистре 10 данных.- Так как мгновенные реакции конт ролируемого логического узла появляются не на всех выходах, что зависит от внутренней структуры логического узла, то на других выходах реакции могут появиться во временном интерва ле, соответствующем второму, третьему и так далее тестовым словам. Поэтому тестовые слова, записанные но второй области памяти накопителя тестов, имеют в первой области памяти соответствующую временную метку, по которой производится считывание и подача тестовых воздействий и эталонные .выходных реакций в строгом соответствии с временной циклограммой работы конкретного логического узла 4. В первой области памяти поля тестов располагаются метки времени (i+l)-ro тестового слова, т.е. на этапе контроля логического узла 4 по i-му тестовому слову регистр 7 меток времени уже содержит (1+1)-ю метку времени.

В случае несовпадения выходной реакции контролируемого логического узла 4 с ее эталонным значением на регистре 10 данных, соответствующий элемент 13 сравнения вырабатывает потенциал, который поступает на первый вход блока 5 управления и переводит триггер 17 в нулевое состояние, которое накладывает запрет на формирование последующих временных меток делителя 6 времени.

При совпадении выходных реакций контролируемого логического узла 4 с их эталонными значениями делитель 6 времени не останавливается и накапливает значения временных интервалов в счетчике 27 до момента совпадения его значения с временной меткой, хранящейся в регистре 7.

Дальнейшая проверка осуществляется аналогичным образом.

Разрядность первой области накопителя 1 тестов определяется соотношением

N ,

где Q - общее количество тестов для контроля логического узла;

1- разряд, определяющий принадлежность информации к тестовому слову;

2- разряд метки коэффициента деления интервалов времени;

3- разряд, обозначающий код завершения контроля.

Разрядность второй области накопителя 1 тестов определяется количеством входов-выходов контролируемых логических узлов.

При дешифрации кода завершения контроля дешифратором 14 вырабатывается сигнал, который поступает в блок 5 управления и останавливает работу устройства.

Выходы элементо в 13 сравнения могут быть выведены на индикацию, отсутствие индикации означает, что контролируемьй логический узел 4 исправен.

В случае иесовпадения выходных реакций контролируемого логического узла 4 с их эталоншоми значениями производится останов устройства, а по состоянию элементов 13 сравнения можно судить о номере несовпадающего выходного контакта.

Устройство позволяет проводить контроль логического узла в строгом соответствии с рабочей последовательреностью временных циклограмм его ального функционирования. изобретения р м у л а Многоканальное устройство тестового контроля логических узлов, содержащее накопитель тестов, блок управления, дешифратор, и п каналов контроля (где п - число входов-выходов контролируемого логического узла) , каждый из которых содержит регистр коммутации, регистр данных, .коммутатор, злемент сравнения, причем в каждом i-M канале контроля (,...,п), выход эталонного отклика регистра данных соединен с первым информационным.входом элемента сравнения, выход тестового воздействия регистра данных соединен с ин формационным входом коммутатора, уп равляющий вход которого соединен с выходом регистра коммутации, выход которого соединен с вторым информационным входом элемента сравнения и соответствующим входом-выходом контролируемого цифрового узла, при этом выходы элементов сравнения все каналов контроля являются выходами признака ощибки устройства, отли чающееся тем, что, с целью повьшения достоверности контроля, устройство содержит счетчик адреса, блок сравнения, элемент ИЛИ, элемен задержки, делитель времени, регистр меток времени, а блок управления со держит три формирователя импульсов, элемент задержки, переключатель пус ка, три элемента ИЛИ и триггер, при чем вход первого формирователя им-:пульсов через переключатель пуска подключен к шине единичного потенциала устройства, выход первого фор мирователя импульсов соединен с пер вым входом первого элемента ИЛИ бло ка управления и через второй формирователь импульсов с первым входом второго элемента ИЛИ блока управле8«ния, с единичным входом .триггера, входом пуска делителя времени и первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ блока управления и с вторым входом второго элемента ИЛИ блока управления, выход которого через элемент задержки блока управления соединен с входами синхронизации регистров данных всех каналов контроля и входом записи регистра меток времени, выходы элементов сравнения всех каналов контроля соединены с первым входом третьего элемента ИЛИ блока управления, второй и третий входы которого соединены с входом сброса устройства и выходом дешифратора, информационные входы которого соединены с выходами регистра меток времени, с первой группой входов блока сравнения и с информационными входами делителя времени, выходы которого соединены с второй группой входов блока сравнения, выход которого соединен через третий формирователь импульсов с вторым входом первого элемента ИЛИ блока управления, выход третьего элемента ИЛИ блока управления соединен с нулевым входом триггера, прямой выход которого соединен с входами разрешения регистров данных всех каналов контроля, инверсный выход триггера соединен с входами разрешения регистров коммутации всех ланалов контроля, информационные входы всех регистров данных .и регистров коммутации всех каналов контроля соединены с выходами тестовой информации накопителя тестов, выходы поля времени которого соединеньь с информационными входами регистра меток времени, выход элемента ИЛИ соединен с входом синхронизации накопителя тестов и через элемент задержки.со счетным входом счетчика адреса, выходы которого соединены с адресными входами накопителя тестов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре тестового контроля и настройки логических узлов и блоков. Цель«изобретения - повышение достоверности контроля. Устройство содержит накопи- с:; тель тестов, блок управления, дешифратор, каналы контроля, в каждый из которых входят регистр коммутации, регистр данных, коммутатор, элемент сравнения, счетчик адреса, блок сравнения, элемент ИЛИ, элемент задержки, делитель времени, регистр меток времени. Устройство позволяет проводить контроль узла в соответствии с рабочей последовательностью временных циклограмм его реального функционирования. Вначале с накопителя тестов поступают данные о расположении входов-выходов контролируемого адреса, при этом открыты регистры коммутации, затем по тем же выходам пос(Л тупают сигналы установки контролируемого узла, тестовые слова и эталонные отклики. Время контроля заносится в делитель времени. 4 ил.

Содпадение

Фиг. 2

С регистра 1

| Устройство для контроля и диагностики цифровых блоков | 1976 |

|

SU605216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758157, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1985-03-01—Подача