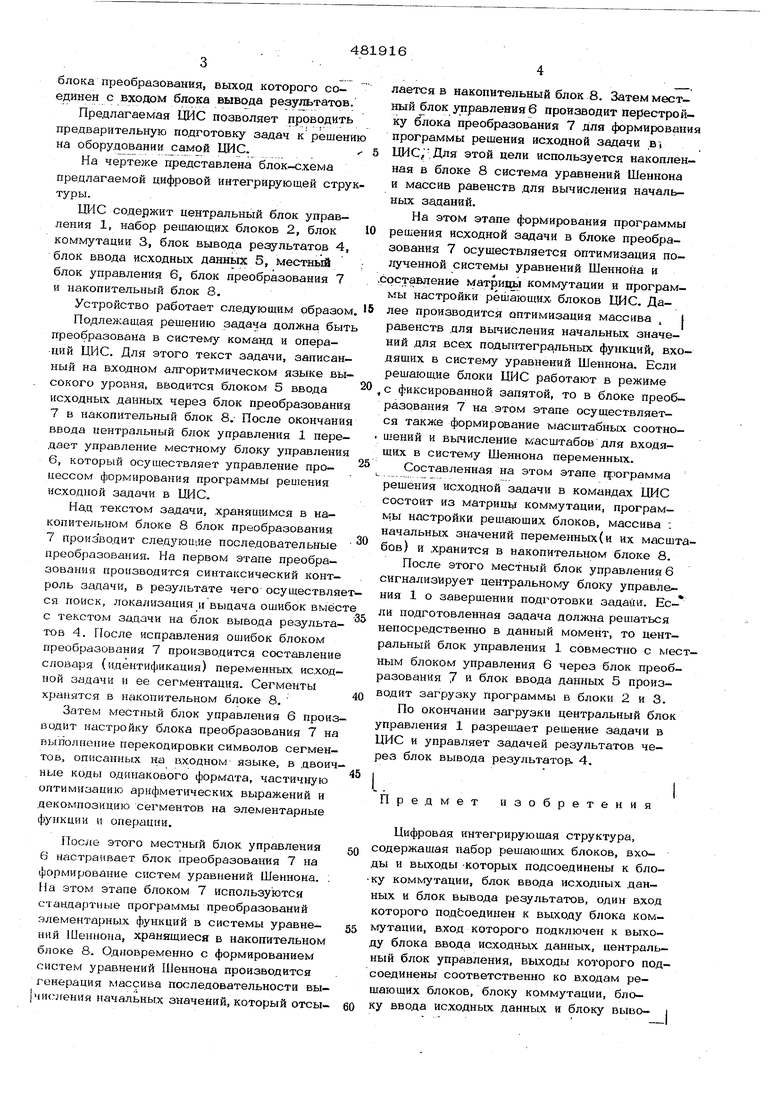

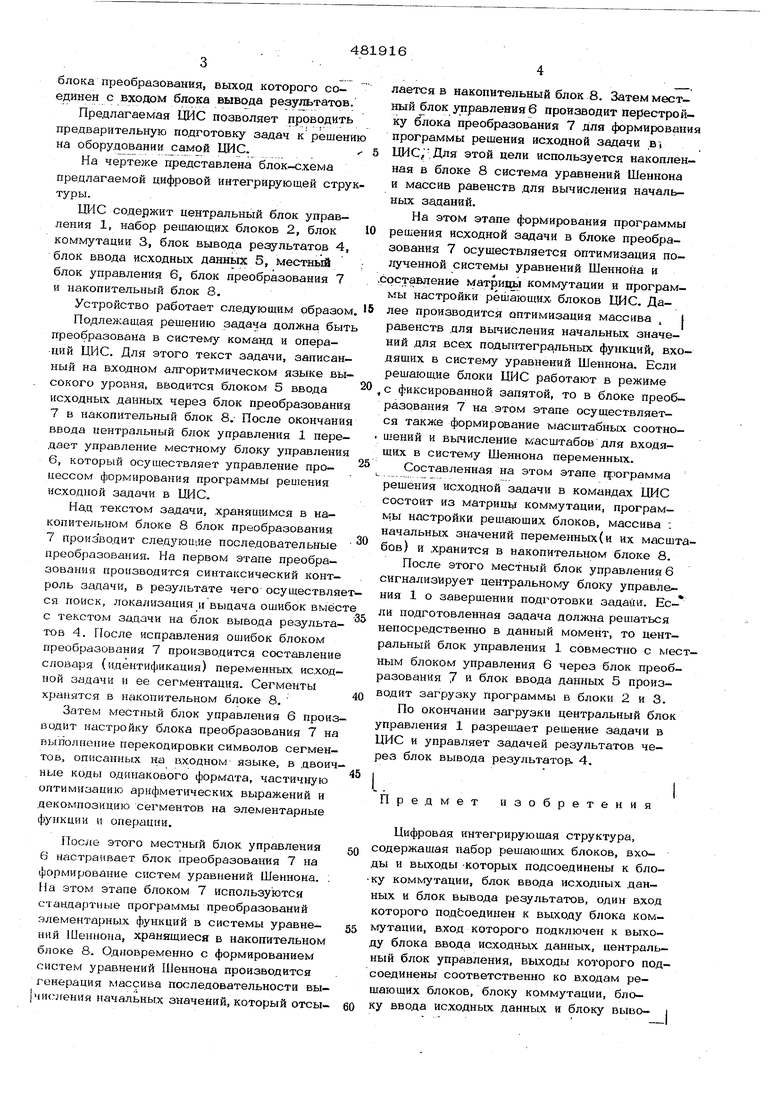

блока преобразования, выход которого соединен с входом блока вывода результатов. Предлагаемая ЦИС позволяет проводить предварительную подготовку здцач к решени на оборудовании самой ЦИС. На чертеже представлена блок-схема предлагаемой цифровой интегрирующей струк туры. ЦИС содержит центральный блок управления 1, набор решающих блоков 2, блок коммутации 3, блок вывода результатов 4, блок ввода исходных данных 5, местньхй блок управления 6, блок преобразования 7 и накопительный блок 8, Устройство работает следующим образом Подлежащая решению зааача должна быт преобразована в систему команд и операций ЦИС. Для этого текст задачи, записанный на входном алгоритмическом языке вы сокого уроаня, вводится блоком 5 ввода исходных данных через блок преобразования 7 в накопительный блок 8.- После окончани ввода центральный блок управления 1 передает управление местному блоку управления 6, который осуществляет управление процессом формирования программы решения исходной задачи в ЦИС, Ндц текстом задачи, хранящимся в накопительном блоке 8 блок преобразования 7 производит след}Ю111,ие последовательные преобразования. На первом этапе преобразования производится синтаксический контроль здцачи, в результате чего осуществля ся поиск, локализация и выдача ошибок вмес с текстом здцачи на блок вывода результатов 4. Г}осле исправления ошибок блоком преобразования 7 производится составление словаря (идентификация) переменных исходной задачи и ее сегментация. Сегменты хранятся Б накопительном блоке 8. Затем местный блок управления 6 произ водит настройку блока преобразования 7 на выполнение перекодировки символов сегментов, описанных на входном языке, в двоич ные коды одинакового формата, частичную оптимизацию арифметических выражений и декомпозицию сегментов на элементарные функции я операции. Rocjo этого местный блок управления 6 настраивает блок преобразования 7 на формирование систем уравнений Шеннона. ; На этом этапе блоком 7 используются стандартные программы преобразований элементарных функций в системы уравнений Шеннона, хранящиеся в накопительном блоке 8. Одновременно с формированием систем уравнений Шеннона производится генерация массива последовательности вы{чи(-ления начальных значений, который отсылается в накопительный блок 8. Затем местный блок ут1равления6 производит перестройку блока преобразования 7 для формирования программы решения исходной задачи Si ЦИС,.Для этой цели используется накопленная в блоке 8 система уравнений Шеннона и массив равенств для вычисления начальных заданий. На этом этапе формирования программы решения исходной задачи в блоке преобразования 7 осуществляется оптимизация полученной системы уравнений Шеннона и оставление матрицы коммутации и программы настройки решающих блоков ЦИС. Да- лее производится оптимизация массива , равенств для вычисления начальных значений для всех подынтегральных функций, входящих в систему уравнений Шеннона. Если решающие блоки ЦИС работают в режиме с фиксированной запятой, то в блоке преобразования 7 на этом этапе осуществляется также формирование масЕ1табных соотношенйй и вычисление масштабов для входящих в систему Шеннона переменных. Составленная на этом этапе фограмма рещения исходной задачи в командах ЦИС состоит из матрицы коммутации, программы настройки решающих блоков, массива : начальных значений перемепных(и их масштабов) и Хранится в накопительном блоке 8. После этого местный блок управления 6 сигнализирует центральному блоку управления 1 о завершении подготовки задайи. Ее- ли подготовленная задача должна решаться непосредственно в данный момент, то центральный блок управления 1 совместно с местным блоком управления 6 через блок преобразования 7 и блок ввода данных 5 производит загрузку программы в блоки 2 и 3. По окончании загрузки центральный блок управления 1 разрешает решение задачи в ЦИС и управляет задачей результатов через блок вывода результатов. 4. Предмет изобретения Цифровая интегрирующая структура, содержащая набор решающих блоков, входы и выходы -которых подсоединены к блоку коммутации, блок ввода исходных данных и блок вывода результатов, один вход которого подЬоединен к выходу блока ком- }утаций, вход которого подключен к выходу блока ввода исходных данных, центральный блок управления, выходы которого подсоединены соответственно ко входам решающих блоков, блоку коммутации, блоку ввода исходных данных и блоку выво- i

да результатов, отличающаяся тем, что с целью повышения быстродейсТ ВИЯ устройства и упрощения подготовки задач к решению, в структуру, введены накопительный блок, местный блок управления, блок преобразования, входы и выходы которого соединены с блоком ввода

исходных данных и накопительным блоком, | вход которого соединен с одним выходом местного блока управления, вход которого соединен с центральным блоком управления, а другой выход - с входом блока преобразования, выход которого соединен с ьходом блока вывода результатов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программирования цифровых интегрирующих структур | 1974 |

|

SU526892A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Цифровая интегрирующая структура | 1973 |

|

SU488205A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1429139A1 |

| СПОСОБ ГЕНЕРАЦИИ БАЗ ЗНАНИЙ ДЛЯ СИСТЕМ ВЕРИФИКАЦИИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ РАСПРЕДЕЛЕННЫХ ВЫЧИСЛИТЕЛЬНЫХ КОМПЛЕКСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2006 |

|

RU2364930C2 |

| Аналого-цифровое вычислительное устройство | 1988 |

|

SU1501103A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Измерительно-вычислительное устройство для определения параметров быстропеременных и пульсирующих потоков жидкостей | 1971 |

|

SU452001A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

Г

П

Авторы

Даты

1975-08-25—Публикация

1973-08-29—Подача