(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| УО:;СОЮЗНАЯ | 1973 |

|

SU363202A1 |

| Устройство для преобразования сигналов информационно-измерительной системы | 1982 |

|

SU1062751A1 |

| Преобразователь напряжения в двоичный код | 1972 |

|

SU482005A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624458A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Динамометрический тестер | 1988 |

|

SU1600704A1 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

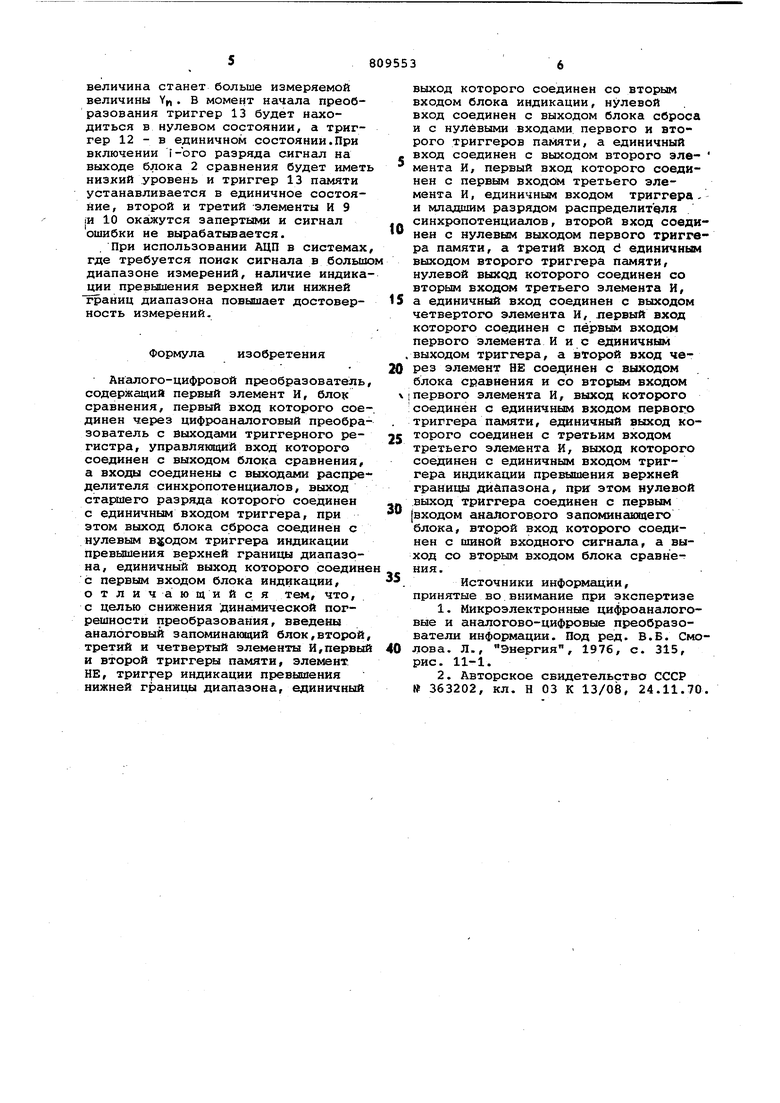

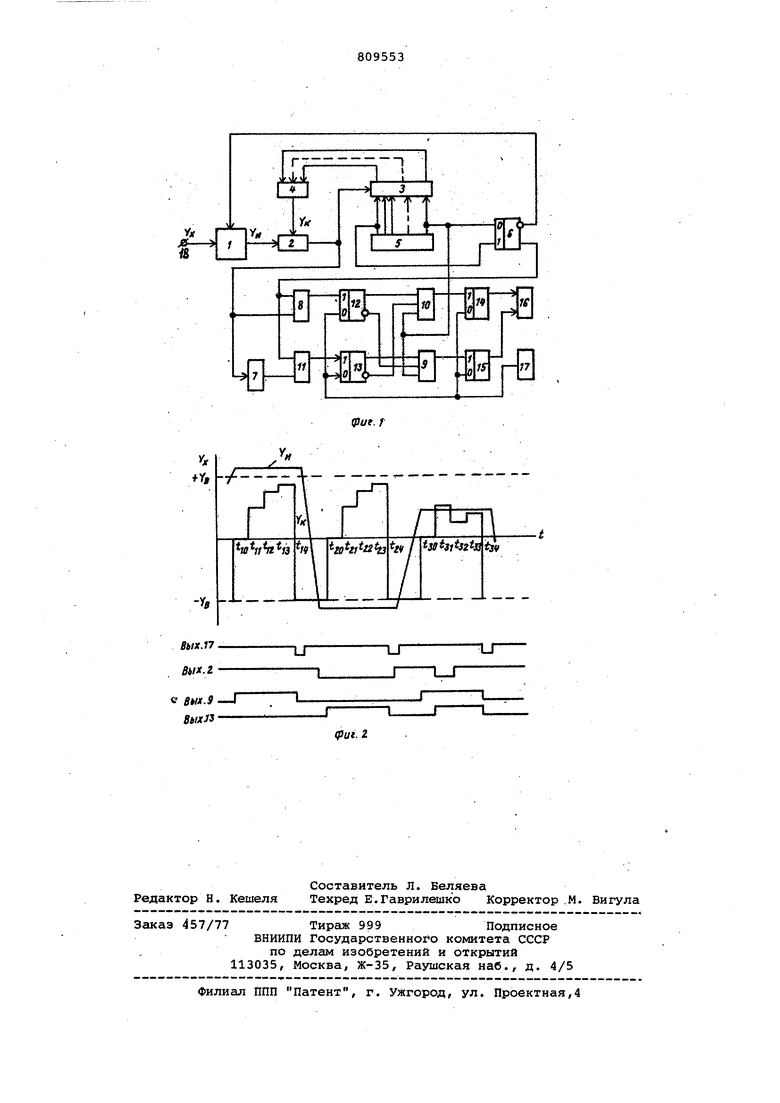

Изобретение относится к импульсной технике, в частности к устройствам для преобразования аналоговых сигналов в цифровой код. Известен аналого-цифровой -преобразователь, содержащий аналоговое запоминакнцее устройство, устройство сравнения, триггерный регистр, преобразователь напряжение-код, распределитель импульсов и триггер управления 1 . Недостатком этого устройства явля ется то, что оно не обеспечивает контроль за превышением входным сигналом границ диапазона измерения аналого-цифрового преобразователя. Известен аналого-цифровой преобра soBaTeJib, содержащий распределитель синхропотенциалов, соединенный с триггерным регистром, выход которого через циф{)оаналоговый преобразова.тель соединен со входом блока сравне ния, триггер индикации с индикаторны устройств1ом, триггер памяти, элемент совпадения, элемент ИЛИ и блок сброса,, причем выход распределителя,соединенный с тригге зом старшего разряда регистра, подключен к единичному входу триггера памяти, выход блока сравнения через элемент ИЛИ соедине с нулевым входом триггера памяти, а выход распределителя, соединенный с триггером младшего разряда, и выход триггера памяти через элемент И соединены с единичньм входом триггера индикации, нулевой вход триггера памяти через элемент ИЛИ и нулевой, вход триггера индикации соединены с выходом блока сброса 2J. Недостатками устройства является то, что оно указывает превышение входным сигнале границ диапазона АЦП, однако не анализирует, какую границу, верхнюю или нижнюю, превысил входной сигнал, имеет большую динамическую погрешность ине реагирует на кратковременное превышение границы диапазона входным сигналом во время преобразования. Цель изобретения - снижение динамической погрешности преобразования. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий первый элемент И, блок сравнения, первый вход которого соединен через цифроаналоговый преобразователь с выходами триггерного регистра, управляющий вход которого соединен с выходом блока сравнения. $ входы соединены с выходами распре делителя синхропотенциалов,выход старшего разряда которого соединен с единичным входом триггера,при этом выход блока сброса соединен с нулевым входом триггера индикации превышения верхней границы диапазон .единичный выход которого соединен с первым входом блока индикации, введены аналоговый запоминающий бло второй, третий и четвертый элементы первый и второй триггеры памяти, элемент НЕ, триггер индикации превы шения нижней границы диапазона, еди ничный выход которого соединен со вторым входом блока индикации, нуле вой вход соединен с выходом блокасброса и с нулевыми входами первого второго триггеров памяти, а единичный вход соединен с выходом второго элемента И, первый вход которого соединен с первым вхЪдом третьего элемента И, единичным входом триггера и младшим разрядом распределителя синхропотенциалов, второй вход соединен с нулевым выходом первого триггера памяти, а третий вход с единичным выходом второго триггера памяти, нулевой выход которого соединен со вторым входом .третьего эле мента И, а единичный вход соединен с выходом четвертого элемента И, пе вый вход которого соединен с первым входом первого элемента И и с единичным выходом триггера, а второй вход через элемент НЕ соединен с выходом блока сравнения и со вторым входом первого элемента И, выход которого соединен с единичным входом первого триггера памяти, единич ный выход которого соединен с .треть входом третьего элемента И, выход которого соединен с единичным входом триггера индикации превышения верхней границы диапазона, при этом нулевой выход триггера соединен с пер вым входом аналогового запоминающег блока, .второй вход которого соедине с шиной входного сигнала, а выход со вторым входом блока сравнения. На фиг. 1 представлена структурна схема аналого-цифрового преобразовагеця; на фиг. 2 - временная диаграмма работы аналого-цифрового преобразователя. «Аналого-цифровой преобразователь содержит аналоговый запоминающий блок 1, блок 2 сравнения, триггерный регистр 3, цифроаналоговый преобразователь (ЦАП) 4, распределитель 5 синхропотенциалов, триггер б,элемент НЕ 7, первый, второй, третий и четвертый элементы И 8-11,первый и второй триггеры 12 и 13 памяти, триггер 14 индикации превышения верхней границы диапазона, триггер 15 индикации превышения нижней границы диапазона, блок 16 индикации. блок 7 сброса, шина 18 входного сигнала. Устройство работает следующим образом. Сигнал с блока сброса устанавливает первый и второй триггеры 12 и 13 памяти и триггеры 14 и 15 индикации превышения верхней и нижней границы уровня в нулевое состояние. В начале преобразования первым синхропотенциалом с выхода распределителя синхропотенциалов триггер 6 устанавливается в единичное состояние и сигнал, с нулевого выхода триггера б поступает на управляющий вход аналогового запоминаки его блока 1. С приходом сигнала низ.кого уровня на управляющий вход aнaлoJ oвый запоминающий блок 1 запоминает входную величину YO и хранит ее до конца преобразования. . Если измеряемый сигнал У„ к моменту начала преобразователя t находится за верхней границей диапазона, то в течение всего времени преобразования компенсационная величина Y будет меньше Y, при этом на выходе . блока 2 сравнения будет сигнал высокого уровня, который через первый элемент И 8 устанавливает триггер 12 памяти в единичное состояние, а триггер 13 памяти остается в нулевом состоянии. При поступлении последнего синхропотенциала через третий элемент И 10 триггер 14 индикации превышения верхней границы диапазона устанавливается в единичное состояние, сигнал с выхода триггера 14 поступает на вход блока 16 индикации. Если измеряемый сигнал Y, к моменту начала преобразования находится за нижней границей диапазона, то в течение всего времени преобразования компенсационная величина Y будет больше при этом на выходе блока 2 сравнения будет сигнал низкого уровня, который через четвертый элемент и 11 устанавливает второй триггер 13 памяти в единичное состояние, а первый триггер 12 памяти остается в нулевом состоянии. При поступлении последнего синхропотенциала через второй элемент И 9, триггер 13 индикации превышения нижней границы диапазона устанавливается в единичное состояние, сигнал с его выхода поступает на вход блока 16 индикации. Если измеряемый сигнал Y к моменту начсша преобразования tjo находится в пределах диапазона измерения, то в момент начала преобразования компенсационная величина Y, будет меньше измеряемого сигнала Y , сиг-. нал на выходе блока 21 сравнения будет иметь высокий уровень до тех пор, пока при включении некоторого 1-ого разряда ЦАП компенсирующая величина станет больше измеряемой величины УИ. В момент начала преобразования триггер 13 будет находиться в нулевом состоянии, а триггер 12 - в единичном состоянии.При включении i-oro разряда сигнал на выходе блока 2 сравнения будет имет низкий уровень и триггер 13 памяти устанавливается в единичное состояние, второй и третий элементы И 9 1И 10 окс1жутся запертыми и сигнал ошибки не вырабатывается. При использовании АЦП в системах где требуется поиск сигнала в больш диапазоне измерений, наличие индика ции превышения верхней или нижней границ диапазона повышает достоверность измерений. Формула изобретения Аналого-цифровой преобразователь содержащий первый элемент И, блок сравнения, первый вход которого сое динен через цифроаналоговый преобра зователь с Выходами триггерного регистра, управляющий вход которого соединен с выходом блока сравнения, а входы соединены с выходами распре делителя синхропотенциалов, выход старшего разряда которого соединен с единичным входом триггера, при этом выход блока сброса соединен с нулевым вводом триггера индикации превышения верхней границы диапазона, единичный выход которого соедин с первым входом блока индикации, отличающийся тем, что, с целью снижения динамической погрешности преобразования, введены аналоговый запоминакэдий блок,второй третий и четвертый элементы И,первы и второй триггеры памяти, элемент НЕ, триггер индикации превышения нижней границы диапазона, единичный выход которого соединен со вторым входом блока индикации, нулевой вход соединен с выходом блока сброса и с нулевыми входами, первого и второго триггеров памяти, а единичный вход соединен с выходом второго элемента И, первый вход которого соединен с первым входсм третьего элемента И, единичным входом триггера, и младацим разрядом распределителя синхропотенциалов, второй вход соединен с нулевым выходом первого триггера памяти, а третий вход d единичным выходом второго триггера памяти, нулевой выхдд которого соединен со вторым входом третьего элемента И, а единичный вход соединен с выходом четвертого элемента И, лервый вход которого соединен с первым входом первого элемента И и с единичным выходом триггера, а второй вход через элемент НЕ соединен с выходом блока сравнения и со вторым входом первого элемента И, выход которого соединен с единичным входом первого триггера памяти, единичный выход которого соединен с третьим входом третьего элемента И, выход которого соединен с единичным входом триггера индикации превшцения верхней границы диапазона, при этом нулевой выход триггера соединен с первым (входом аналогового запоминавшего блока, второй вход которого соединен с шиной входного сигнала, а выход со вторым входом блока сравне- ния. Источники информации, принятые во.внимание при экспертизе 1.Микроэлектронные цифроаналоговые и аналогово-цифровые преобразователи информации. Под ред. В.Б. Смолова. Л., Энергия, 1976, с. 315, рис. 11-1. 2.Авторское свидетельство СССР № 363202, кл. Н 03 К 13/08, 24.11.70.

УХ

r.

LJ

L

J Iг

(put. 2

J

Авторы

Даты

1981-02-28—Публикация

1979-03-02—Подача