1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах параллельного типа.

Известен накапливающий сумматор, состоящий из i групп и содержащий в каждой t-й группе (где i - целое, положительное число, t 2) счетные триггеры, установочные входы которых соединены с выходом схемы формирования переноса по модулю в данной группе, а счетные входы, кроме счетного входа триггера младщего разряда, - соответственно с выходами схем «ИЛИ. Первые входы схем «ИЛИ связаны соответственно с первым и вторым входами сумматора данной группы, а вторые входы - с выходами схем формирования последовательного переноса из предыдущего разряда в данной группе, входы которых подключены соответственно к единичным выходам счетных триггеров и к входам схемы формирования переноса но модулю в данной группе.

Цель изобретения - повышение быстродействия сумматора при сложении двоичных чисел.

Это достигается тем, что в каждую группу сумматора введена схема «И. Первый вход схерлы «И связан с выходом схемы формирования последовате.гыюго переноса в старшем разряде ((-1)-й группы и с первым входом дополнительной схемы «ИЛИ, второй вход -

с выходом схемы формирования последовательного переноса в старщем разряде данной группы и с вторым входом дополнительной схемы «ИЛИ, а выход - с дополнительным

входом запрета счетного триггера младщего разряда и через элемент задержки с дополнительным входом схемы «ИЛИ. Первый вход последней соединен с вторым входом сумматора в данной группе. Выход дополнительной

схемы «ИЛИ подключен к входу счетного триггера младщего разряда. Третий вход схемы «И подсоединен к третьему входу сумматора в данной группе, а четвертный вход - к выходу схемы формирования переноса по модулю в (i-1)-й группе.

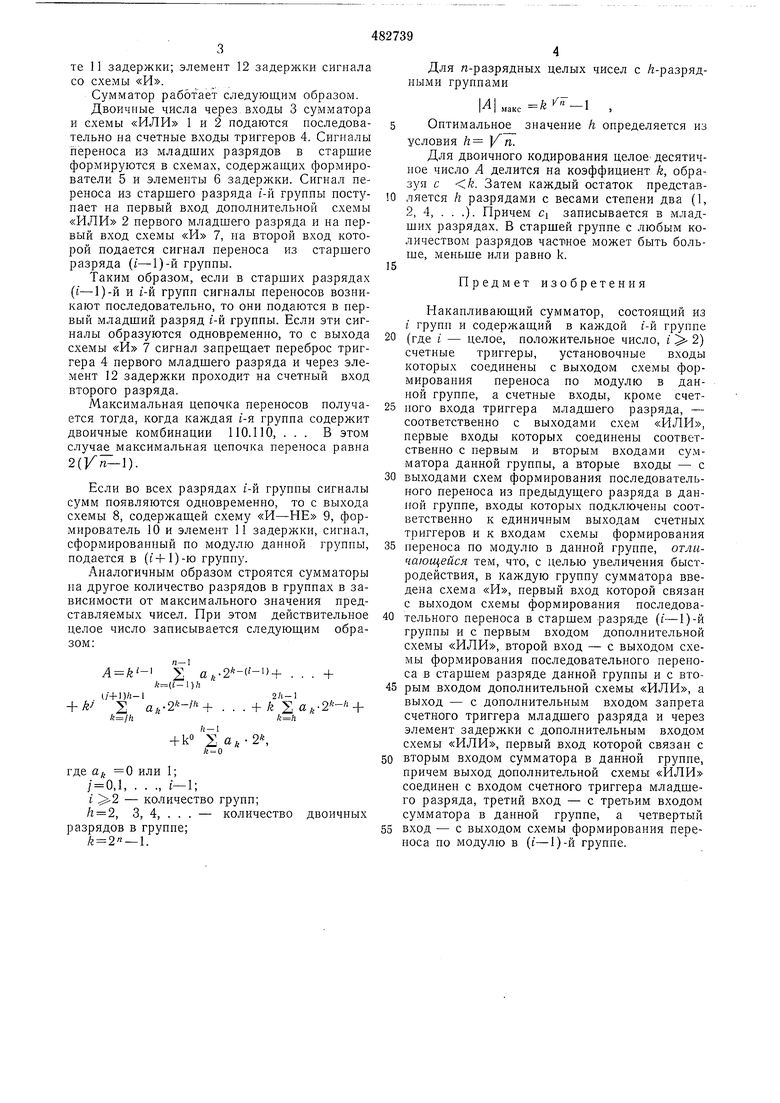

На чертеже показана схема i-й группы на три разряда /г-разрядного накапливающего сумматора (где ( 2).

Сумматор содержит схемы «ИЛИ 1 и дополнительную схему «ИЛИ 2, через которые информация с входов 3 устройства поступает на счетные входы триггеров 4; схемы формирования последовательного переноса па формирователях 5 и элементах 6 задержки; схему «И 7, объединяющую входы схем формирования носледовате.чьных нереносов старших разрядов с-й и ((-1)-й групп; схему 8 формирования переноса по модулю в данной группе на

схеме «И-ПЕ 9, формирователе 10 и элементе 11 задержки; элемент 12 задержки сигнала со схемы «И.

Сумматор работает следующим образом.

Двоичные числа через входы 3 сумматора и схемы «ИЛИ 1 и 2 подаются последовательно на счетные входы триггеров 4. Сигналы переноса из младших разрядов в старшие формируются в схемах, содержащих формирователи 5 и элементы 6 задерл ки. Сигнал переноса из старшего разряда /-и группы поступает на первый вход дополнительной схемы «ИЛИ 2 первого младшего разряда и на первый вход схемы «И 7, на второй вход которой подается сигнал переноса из старшего разряда (г-1)-й группы.

Таким образом, если в старших разрядах (t-1)-й и i-й групп сигналы переносов возникают последовательно, то они подаются в первый младший разряд i-й группы. Если эти сигналы образуются одновременно, то с выхода схемы «И 7 сигнал запрещает переброс триггера 4 первого младшего разряда и через элемент 12 задержки проходит на счетный вход второго разряда.

Максимальная цепочка переносов получается тогда, когда каждая i-я группа содержит двоичные комбинации ПО.ПО, ... В этом случае максимальная цепочка переноса равьга

2().

Если во всех разрядах i-й группы сигналы сумм появляются одновременно, то с выхода схемы 8, содержащей схему «И-НЕ 9, формирователь 10 и элемент 11 задержки, сигнал, сформированный по модулю данной группы, подается в (( + 1)-ю группу.

Аналогичным образом строятся сумматоры на другое количество разрядов в группах в зависимости от максимального значения представляемых чисел. При этом действительное целое число записывается следующим образом:

A k- а,(-)+ . . . -f

k(i- l)h (/-t-l)ft-l2Л-1

+ S . . . + S a,-2 - -} /ftk h

+ ko 2 ,

k-O

где Oft 0 или 1;

/ 0,1, . . ., f-1;

i 2 - количество групп;

/г 2, 3, 4, ... - количество двоичных разрядов в группе;

-1.

Для п-разрядных целых чисел с /i-разрядными группами

|- макс J

Оптимальное значение /г определяется из условия /г )/п.

Для двоичного кодирования целое десятичное число Л делится на коэффициент k, образуя с /г. Затем каждый остаток представляется h разрядами с весами степени два (1, 2, 4, . . .). Причем Ci записывается в младщих разрядах. В старшей группе с любым количеством разрядов частное может быть больше, меньше или равно k.

Предмет изобретения

Накапливающий сумматор, состоящий из / групп и содержащий в каждой i-й группе

(где / - целое, положительное число, i 2) счетные триггеры, установочные входы которых соединены с выходом схемы формирования переноса по модулю в данной группе, а счетные входы, кроме счетного входа триггера младшего разряда, - соответственно с выходами схем «ИЛИ, первые входы которых соединены соответственно с первым и вторым входами сумматора данной группы, а вторые входы - с

выходами схем формирования последовательного переноса из предыдущего разряда в данной группе, входы которых подключены соответственно к единичным выходам счетных триггеров и к входам схемы формирования

переноса по модулю в данной группе, отличающейся тем, что, с целью увеличения быстродействия, в каждую группу сумматора введена схема «И, первый вход которой связан с выходом схемы формирования последовательного переноса в старшем разряде (г-1)-й группы и с первым входом дополнительной схемы «ИЛИ, второй вход - с выходом схемы формирования последовательного переноса в старшем разряде данной группы и с вторым входом дополнительной схемы «ИЛИ, а выход - с дополнительным входом запрета счетного триггера младшего разряда и через элемент задержки с дополнительным входом схемы «ИЛИ, первый вход которой связан с

вторым входом сумматора в данной группе, причем выход дополнительной схемы «ИЛИ соединен с входом счетного триггера младшего разряда, третий вход - с третьим входом сумматора в данной группе, а четвертый

вход - с выходом схемы формирования переоса по модулю в (t-1)-й группе.

Г

л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Формирователь корректирующего кода | 1989 |

|

SU1695515A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Устройство для формирования и хранения адресов команд | 1984 |

|

SU1182578A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1970 |

|

SU273519A1 |

Авторы

Даты

1975-08-30—Публикация

1973-06-11—Подача