1 о соединен с вторым входом первого элемента И, а третий выход - с входами синхронизации первого счетчика и первого регистра адресов команд, выходы с четвертого по седьмой блока управления подключены соответственно к входам синхронизации второго счетчика, третьего счетчика, первого триггера и второго регистра адресов команд, восьмой и девятый выходы блока управления соединены соотBetcTBeHHO с управляющими входами второго и третьего счетчиков,.а десятый выход подключен к входу синхронизации: второго триггера, выход которого является контрольным выходом устройства, вторым и третьим управляющими входами которого являются первый и второй входы блока управления, входы с третьего по седьмой которого являются входами синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля переписи информации перезагружаемой управляющей памяти процессора | 1981 |

|

SU1008746A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Блок адресации для процессора быстрого преобразования Фурье | 1984 |

|

SU1223247A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ И ХРАНЕНИЯ АДРЕСОВ КОМАНД, содержащее регистры адресов команд, сумматоры по модулю два, мультиплексоры, первый блок сравнения и блок управления, причем одни из входов первого мультиплексора и выходы второго мультиплексора являются соответственно одними из входов и выходами устройства, выходы первого мультиплексора соединены с входами первого регистра адресов команд, одни из выходов которого подключены к входам первой группы второго мультиплексора и входам второго регистра адресов команд, выходы которого соединены с одними из входов первого и второго сумматоров по модулю два, выходы первого сумматора по модулю два подключены к одним из входов первого .блока сравнения и другим входам первого мультиплексора, другие входы сумматоров по модулю два и управляклций вход второго мультиплексора являются соответственно другими входами и первым управляющим входом устройства, отличающееся тем, что, с целью -повьшения надежности и упрощения устройства, в него введены счетчики, второй блок сравнения, триггеры, элементы И, элементы ИЛИ и элемент НЕ, причем входы первого и второго счетчиков соединены с одними из входов первого мультиплексора, счетный вход третьего счетчика подключен к дpyгo тy выходу первого регистра адресов команд, входу элемента НЕ и первым входам первого и второго элементов И, выходы которых соединены с входами первого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, счетный вход первого счетчика соединер с первым выходом переноса перф вого сумматора по модулю два, второй вькод переноса которого подклюС/) чен к второму входу второго элемента И, выходы первого счетчика соединены с входами третьего счетчика, выходы которого и выходы второго счетчика подключены соответственно к входам второго блока сравнения, выход которого соединен с первым вхооо ю ел дом второго элемента ИЛИ, второй вход которого подключен к выходу первого триггера, а выход - к входу второго триггера, вход первого триг00 гера соединен с выходом первого блока сравнения, другие входы которого подключены к выходам второго сумматора по модулю два, входы второй, третьей и четвертой групп второго мультиплексора соединены соответственно с выходом второго счетчика, с выходом элемента НЕ и с выходами первого счетчика, третий вход второго элемента И и управляющие входы первого счетчика и первого мультиплексора подключены к первому выходу блока управления, второй выход которо

1

Изобретение относится к вычислительной технике, в частности к запоминающим, устройствам и может использоваться в цифровых микропрограммных вычислительных машинах с байтной структурой данных и с хранимой в оперативной памяти программой.

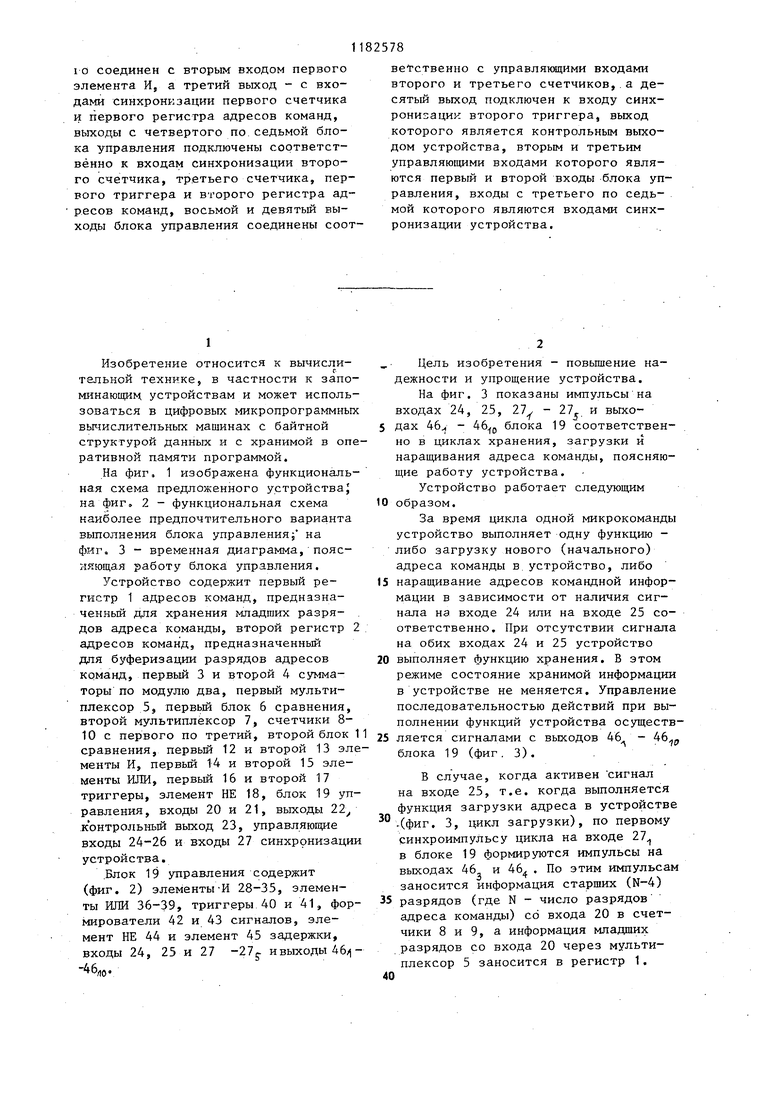

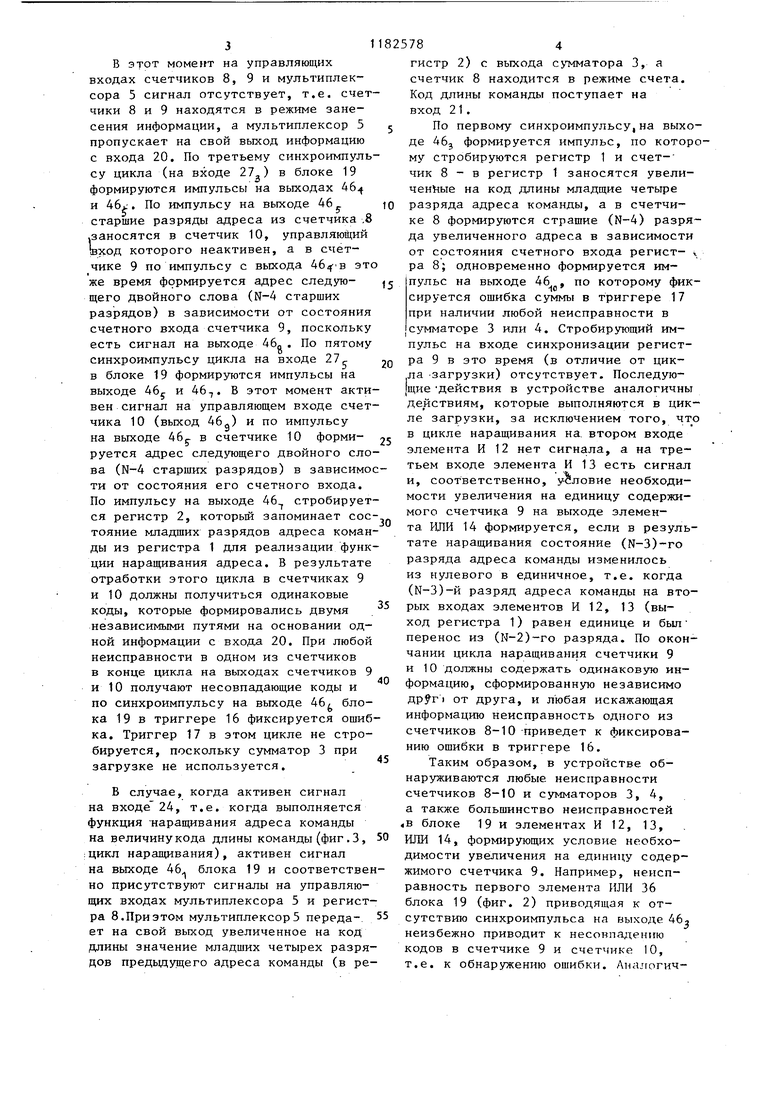

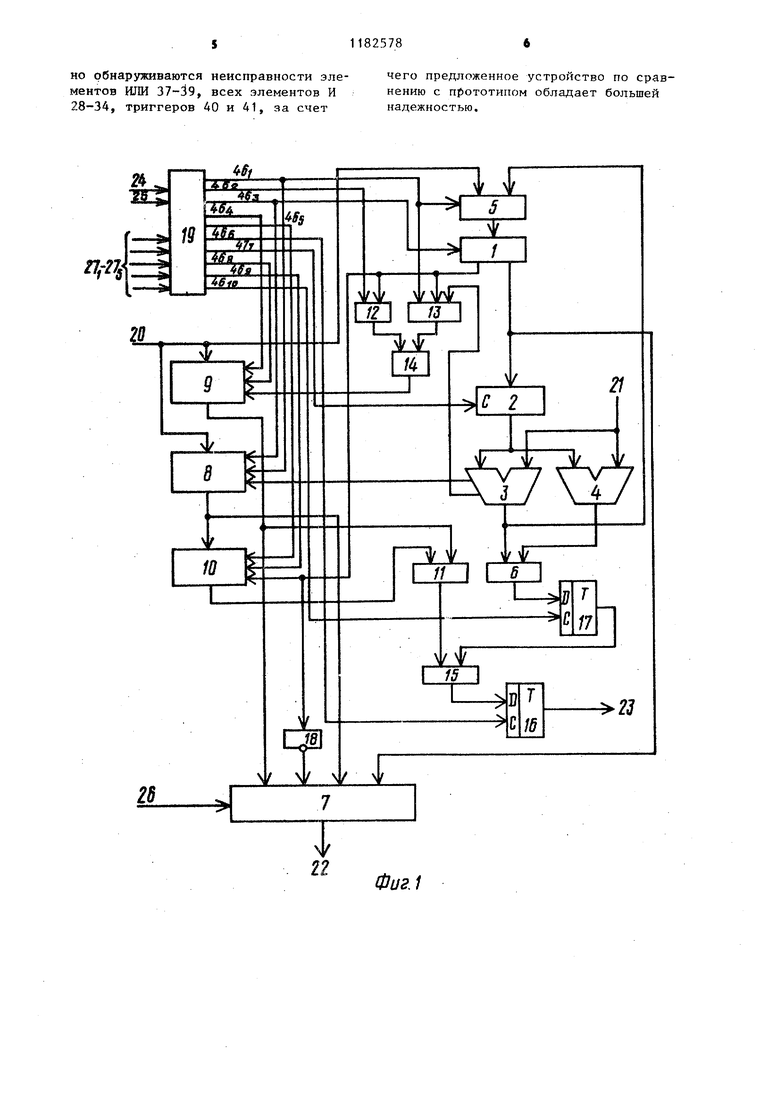

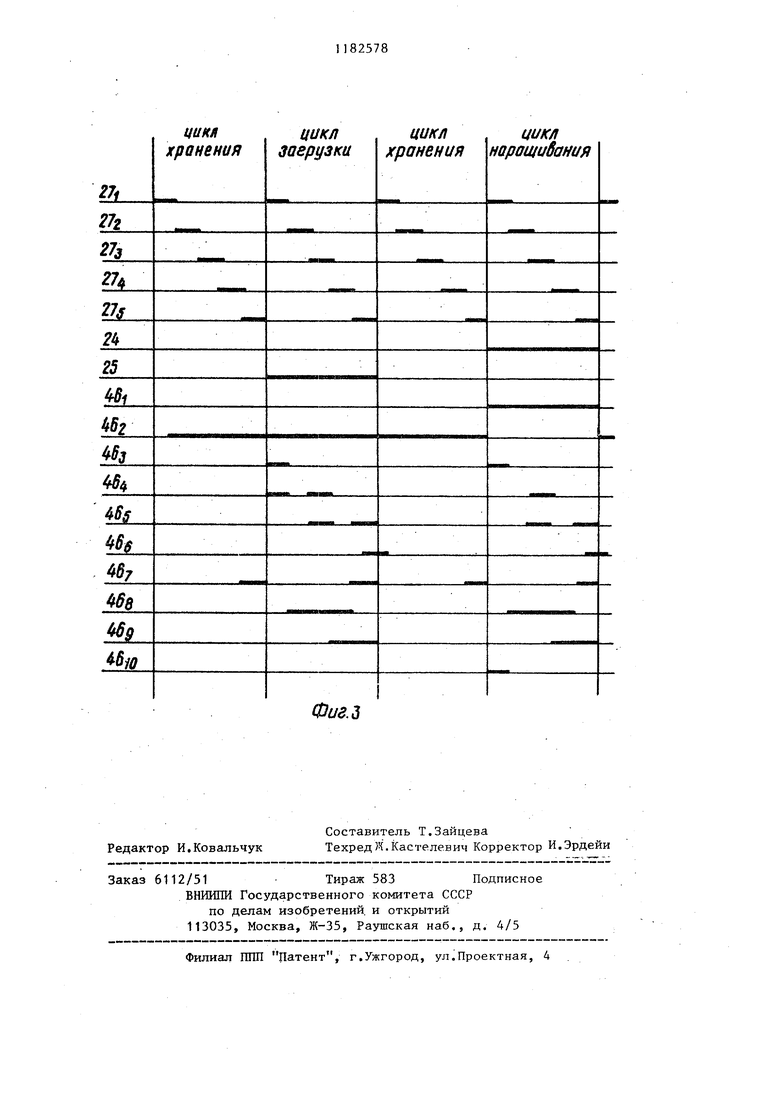

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема наиболее предпочтительного варианта выполнения блока управления; на фиг. 3 - временная диаграмма,поясняющая работу блока управления.

Устройство содержит первый регистр 1 адресов команд, предназначенный для хранения младших разрядов адреса команды, второй регистр 2 адресов команд, предназначенный дпя буферизации разрядов адресов команд, первый 3 и второй 4 сумматоры по модулю два, первый мультиплексор 5, первьш блок 6 сравнения, второй мультиплексор 7, счетчики 810 с первого по третий, второй блок 1 сравнения, первый 12 и второй 13 элементы И, первый 14 и второй 15 элементы ИЛИ, первый 16 и второй 17 триггеры, элемент НЕ 18, блок 19 управления, входы 20 и 21, выходы 22 контрольньш выход 23, управляющие входы 24-26 и входы 27 синхронизации устройства.

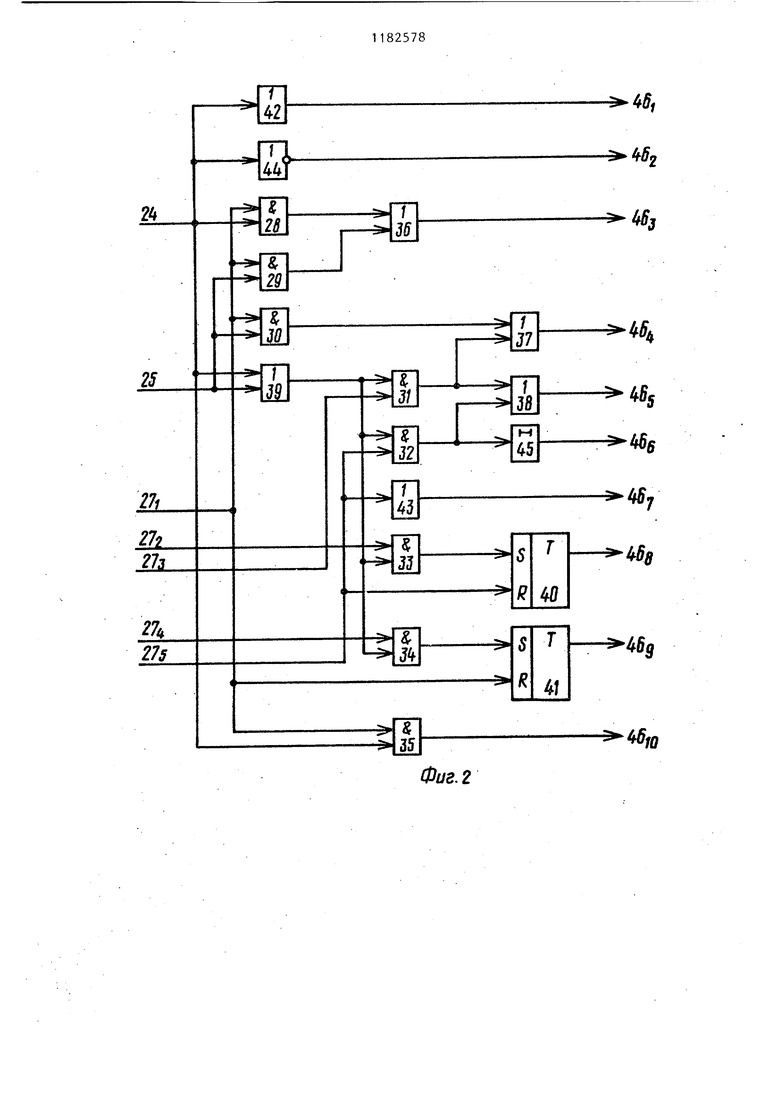

Блок 19 управления содержит (фиг. 2) элементы-И 28-35, элементы ИЛИ 36-39, триггеры 40 и 41, формирователи 42 и 43 сигналов, элемент НЕ 44 и элемент 45 задержки, входы 24, 25 и 27 -275. ивыходы46;1- 6,0.

Цель изобретения - повьшение надежности и упрощение устройства.

На фиг. 3 показаны импульсы на входах 24, 25, 27. - 27. и вьгходах 46 - блока 19 соответственно в циклах хранения, загрузки и наращивания адреса команды, поясняющие работу устройства.

Устройство работает следующим

образом.

За время цикла одной микрокоманды устройство выполняет одну функцию либо загрузку нового (начального) адреса команды в устройство, либо

наращивание адресов командной информации в зависимости от наличия сигнала на входе 24 или на входе 25 соответственно. При отсутствии сигнала на обих входах 24 и 25 устройство

выполняет функцию хранения. В этом режиме состояние хранимой информации в устройстве не меняется. Управление последовательностью действий при выполнении функций устройства осуществляется сигналами с выходов 46 - 46

10 блока 19 (фиг. 3).

В случае, когда активен сигнал на входе 25, т.е. когда выполняется функция загрузки адреса в устройстве

.(фиг. 3, цикл загрузки), по первому синхроимпульсу цикла на входе 27. в блоке 19 формируются импульсы на выходах 46 и 46 . По этим импульсам заносится информация старших (N-4)

разрядов (где N - число разрядов адреса команды) со входа 20 в счетчики 8 и 9, а информация младших разрядов со входа 20 через мультиплексор 5 заносится в регистр 1. в этот MOMeifT на управляющих входах счетчиков 8, 9 и мультиплексора 5 сигнал отсутствует, т.е. счетчики 8 и 9 находятся в режиме занесения информации, а мультиплексор 5 пропускает на свой выход информацию с входа 20. По третьему синхроимпульсу цикла (на входе 27) в блоке 19 формируются импульсы на выходах 46 и 46. По импульсу на выходе 46 . старшие разряды адреса из счетчика ,8 .заносятся в счетчик 10, управляющий вход которого неактивен, а в счетчике 9 по импульсу с выхода 464 в это же время формируется адрес следующего двойного слова (N-4 старших разрядов) в зависимости от состояния счетного входа счетчика 9, поскольку есть сигнал на выходе 46„. По пятому синхроимпульсу цикла на входе 27 в блоке 19 формируются импульсы на выходе 46j и 46-,. В этот момент активен сигнал на управляющем входе счетчика 10 (выход 46а) и по импульсу на выходе 465. в счетчике 10 формируется адрес следующего двойного слова (N-4 старших разрядов) в зависимос ти от состояния его счетного входа. По импульсу на выходе 46 стробируется регистр 2, который запоминает состояние младших разрядов адреса команды из регистра 1 для реализации функции наращивания адреса. В результате отработки этого цикла в счетчиках 9 и 10 должны получиться одинаковые коды, которые формировались двумя независимыми путями на основании одной информации с входа 20. При любой неисправности в одном из счетчиков в конце цикла на выходах счетчиков 9 и 10 получают несовпадающие коды и по синхроимпульсу на выходе 46 блока 19 в триггере 16 фиксируется ошиб ка. Триггер 17 в этом цикле не стробируется, поскольку сумматор 3 при загрузке не используется. В случае, когда активен сигнал на входе24, т.е. когда выполняется функция наращивания адреса команды на величину кода длины команды (фиг .3, ;цикл наращивания), активен сигнал на выходе 46 блока 19 и соответствен но присутствуют сигналы на управляющих входах мультиплексора 5 и регистра 8,При этом мультиплексор 5 передает на свой выход увеличенное на код длины значение младших четырех разрядов предьщудего адреса команды (в ре1784 гистр 2) с выхода ciMMaTopa 3, а счетчик 8 находится в режиме счета. Код длины команды поступает на вход 21. По первому синхроимпульсу,на выходе 46j формируется импульс, по которому стробируются регистр 1 и счетчик 8 - в регистр 1 заносятся увеличенйые на код длины младщие четыре разряда адреса команды, а в счетчике 8 формируются страшие (N-4) разряда увеличенного адреса в зависимости от состояния счетного входа регист- ра 8; одновременно формируется им- пульс на выходе 46 , по которому фиксируется ошибка суммы в триггере 17 при наличии любой неисправности в сумматоре 3 или 4. Стробирутощий импульс на входе синхронизации регистра 9 в это время (в отличие от цикла -загрузки) отсутствует. Последую|щие действия в устройстве аналогичны действиям, которые выполняются в цикле загрузки, за исключением того, что Цикле наращивания на втором входе элемента И 12 нет сигнала, а на третьем входе элемента И 13 есть сигнал и, соответственно, условие необходимости увеличения на единицу содержимого счетчика 9 на выходе элемента ИЛИ 14 формируется, если в результате наращивания состояние (N-3)-ro разряда адреса команды изменилось из нулевого в единичное, т.е. когда (М-З)-й разряд адреса команды на вторых входах элементов И 12, 13 (выход регистра 1) равен единице и был перенос из (N-2)-ro разряда. По окончании цикла наращивания счетчики 9 и 10 должны содержать одинаковую информацию, сформированную независимо I от друга, и любая искажающая информацию неисправность одного из счетчиков 8-10 приведет к фиксированию ошибки в триггере 16. Таким образом, в устройстве обнаруживаются любые неисправности счетчиков 8-10 и сумматоров 3, 4, а также большинство неисправностей |В блоке 19 и элементах И 12, 13, ИЛИ 14, формирующих условие необходимости увеличения на единицу содержимого счетчика 9. Например, неисправность первого элемента ИЛИ 36 блока 19 (фиг. 2) приводящая к отсутствию синхроимпульса на выходе 46, неизбежно приводит к несовпадению кодов в счетчике 9 и счетчике 10, т.е. к обнаружению ошибки. Ана.тогично обнаруживаются неисправности элементов ИЛИ 37-:i9, всех элементов И 28-34, триггеров 40 и 41, за счет

чего предложенное устройство по сравнению с прототипом обладает большей надежностью.

Фиг. 2

Фиг. 2

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Реле | 1925 |

|

SU2435A1 |

| Насос | 1917 |

|

SU13A1 |

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-20—Подача