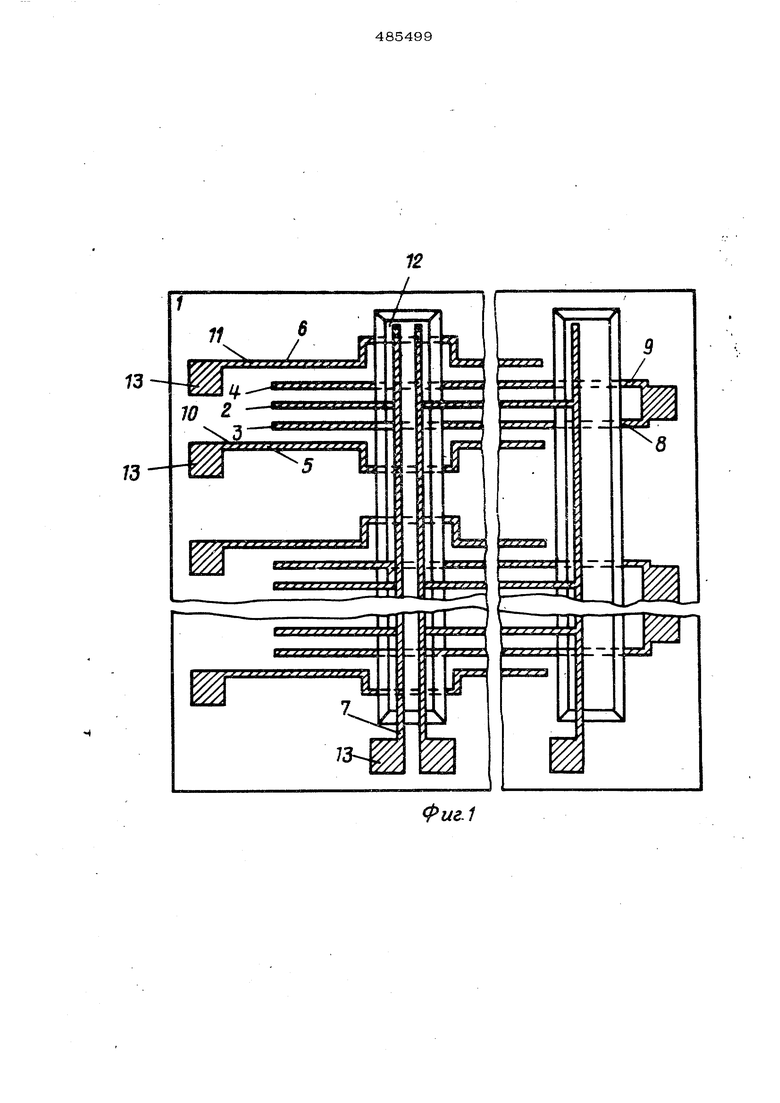

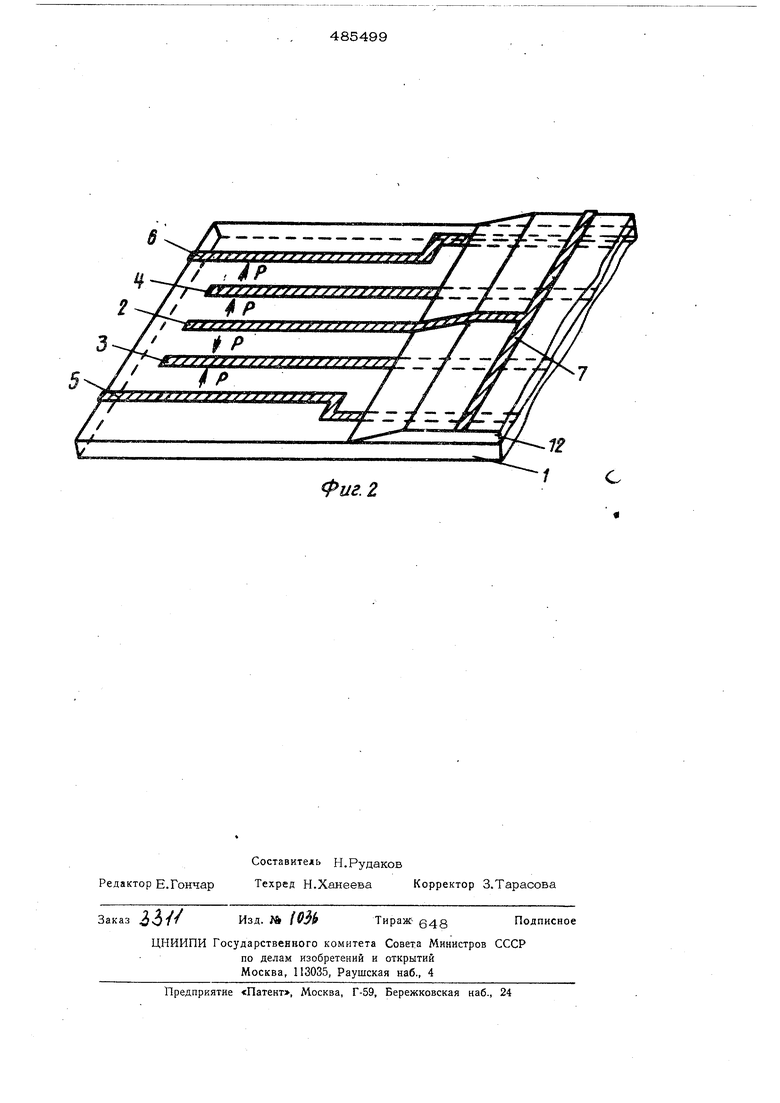

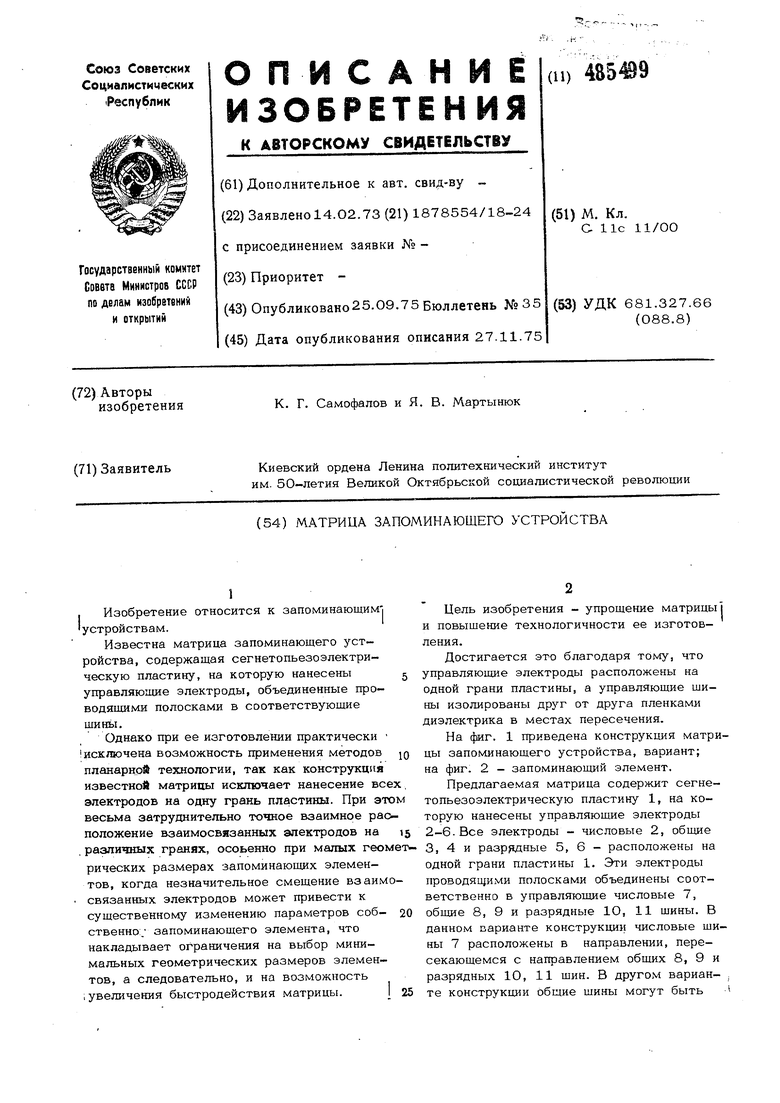

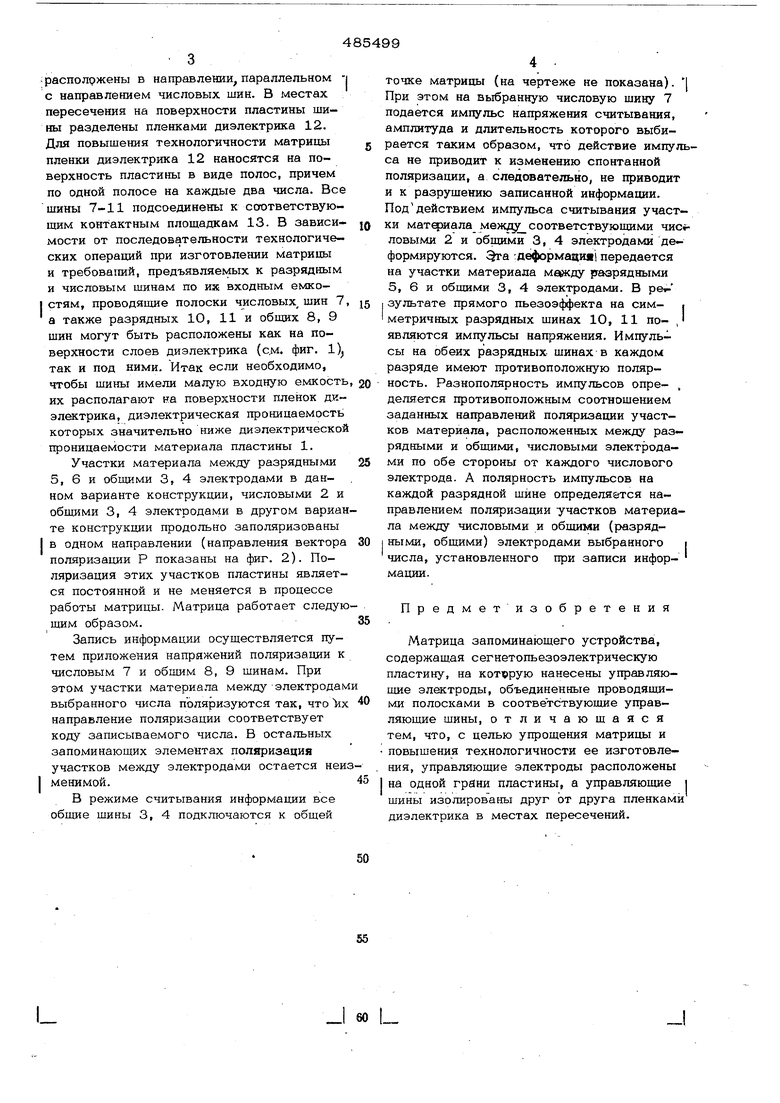

I Изобретение относится к запоминающим устройствам. Известна матрица запоминающего устройства, содержащая сегнетопьезоэлектри- ческую пластину, на которую нанесены управляющие электроды, объединенные проводящими полосками в соответствующие Однако при ее изготовлении практически исключена возможность применения методов пленарной технологии, так как конструкция известной матрицы исключает нанесение вс электродов на одну грань пластины. При эт весьма затруднительно точное взаимное ра положение взаимосвязанных электродов на . различных гранях, осоьенно при малых гео рических размерах запоминающих элементов, когда незначительное смещение взаим связанных электродов может привести к существенному изменению параметров собственно:. запоминающего элемента, что накладывает ограничения на выбор минимальных геометрических размеров элементов, а следовательно, и на возможность , увеличения быстродействия матрицы. Цель изобретения - упрощение матрицы и повыщение технологичности ее изготовления. Достигается это благодаря тому, что управляющие электроды расположены на одной грани пластины, а управляющие шины изолированы друг от друга пленками диэлектрика в местах пересечения. На фиг. 1 приведена конструкция матрицы запоминающего устройства, вариант; на фиг. 2 - запоминающий элемент. Предлагаемая матрица содержит сегнетопьезоэлектрическую пластину 1, на которую нанесены управляющие электроды 2-6. Все электроды - числовые 2, общие 3, 4 и разрядные 5, 6 - расположены на одной грани пластины 1. Эти электроды проводящими полосками объединены соответственно в управляющие числовые 7, общие 8, 9 и разрядные 1О, 11 щины. В данном варианте конструкции числовые щины 7 расположены в направлении, пересекающемся с направлением общих 8, 9 и разрядных 10, 11 щин. В другом вариан- , те конструкции общие щины могут быть фасполржены в направлении, параллельном с направлением числовых шин. В местах пересечения на поверхности пластины шины разделены пленками диэлектрика 12. Для повышения технологичности матрицы пленки диэлектрика 12 наносятся на поверхность пластины в виде полос, причем по одной полосе на каждые два числа. Все шины 7-11 подсоединены к соответствующим контактным площадкам 13. В зависимости от последовательности технологических операций при изготовлении матрицы и требова шй, предъявляемых к разрядным и числовым шинам по ия входным емкоI стям, проводящие полоски числовых шин 7 а также разрядных 10, 11 и общих 8, 9 щин могут быть расположены как на поверхности слоев диэлектрика (с.м. фиг. 1) так и под ними. Итак если необходимо, чтобы шины имели малую входную емкость их располагают на поверхности пленок диэлектрика, диэлектрическая проницаемость которых значительно ниже диэлектрической проницаемости материала пластины 1. Участки материала между разрядными 5, 6 и общими 3, 4 электродами в данном варианте конструкции, числовыми 2 и общими 3, 4 электродами в другом вариан те конструкции продольно заполяризованы I в одном направлении (направления вектора поляризации Р показаны на фиг. 2). Поляризация этих участков пластины является постоянной и не меняется в процессе работы матрицы. Матрица работает следую щим образом. Запись информации осуществляется путем приложения напряжений поляризации к числовым 7 и общим 8, 9 шинам. При этом участки материала между-электродам выбранного числа поляризуются так, что их направление поляризации соответствует коду записываемого числа. В остальных запоминающих элементах поляризация участков между электродами остается неи менимой. В режиме считывания информации все общие шины 3, 4 подключаются к общей точке матрицы (на чертеже не показана). При этом на выбранную числовую шину 7 подается импульс напряжения считывания, амплитуда и длительность которого выбирается таким образом, что действие импульса не приводит к изменению спонтанной поляризации, а следовательно, не приводит и к разрушению записанной информации. Под действием импульса считывания участки матфиала меж;:у соответствующими чис ловыми 2 и общими 3, 4 электродами деформируются. Зга деформация передается на участки материала мдасду разрядными 5, 6 и общими 3, 4 электродами. В ре зультате прямого пьезоэффекта на сим- i метричных разрядных шинах 10, 11 по- , являются импульсы напряжения. Импульсы на обеих разрядных щинах в каждом разряде имеют противоположную полярность. Разнополярность импульсов определяется противоположным соотношением заданных направлений поляризации участков материала, расположенных между разрядными и общими, числовыми электродами по обе стороны от каждого числового электрода. А полярность импульсов на каждой разрядной шине определяется направлением поляризации участков материала между числовыми и общими (разрядными, общими) электродами выбранного i числа, установленного при записи информадии. Предметизобретения Матрица запоминающего устройства, содержащая сегнетопьезоэлектрическую пластину, на котррую нанесены управляющие электроды, объединенные проводящими полосками в соответЬтвующие управляющие шины, отличающаяся тем, что, с целью упрощения матрицы и повышения технологичности ее изготовления, управляющие электроды расположены на одной грани пластины, а управляющие i шины изолированы друг от друга пленками диэлектрика в местах пересечений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1973 |

|

SU488257A1 |

| Запоминающая матрица | 1979 |

|

SU855731A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| МАТРИЦА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1971 |

|

SU427378A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1972 |

|

SU469139A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

1 60

иг.2

Авторы

Даты

1975-09-25—Публикация

1973-02-14—Подача