3

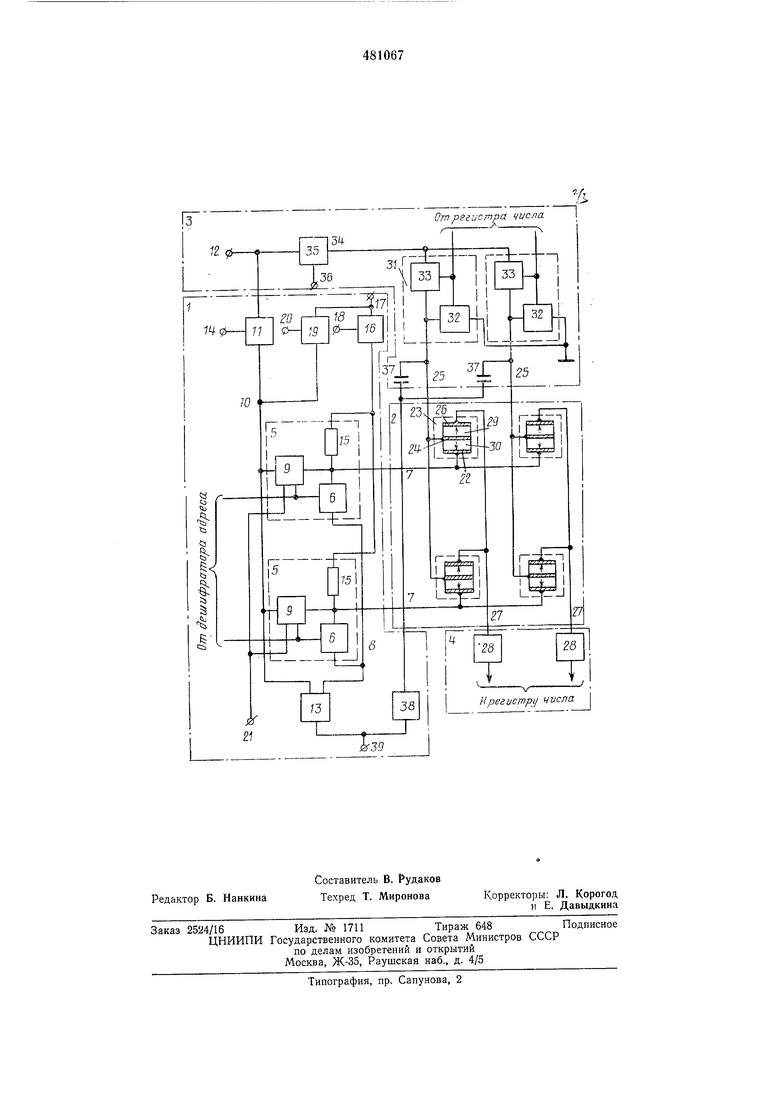

Блок 1 управления по адресу содержит составные адресные ключи 5, управляющие входы которых подключены к выходам дешифратора адреса (дешифратор па чертеже не показан). Каждый из адресных ключей состоит из ключа 6, через который числовые шипы 7 блока 2 иодсоедипеиы к общей шине 8, а из ключа 9, через который числовые шины 7 подключены к управляющей шиие 10. Шипа 10 через ключ 11 соединена с источником напрял ення поляризации -Up (клемма 12). Шина 8 соединена с одним выходом формирователя 13 токов считывания, со вторым выходом которого соединена щина 10. Клемма 14 является унравляюндим входом ключа 11. Кроме того, числовые шины 7 через резисторы 15 подключены к выходу ключа 16, вход 17 которого соединен с источником напряжения, составляющего часть напряжения поляризации, в данрном случаеп-. Клемма 18 - управляющий

вход .ключа 16. С этим источником через ключ

19соединена и шина 10. В ключе 19 клемма

20является управляющим входом. Ключи 9 имеют дополнительные управляющие входы. Они подключены к шине 21 запрета включения.

В матрице 2 входные электроды 22 широкополосных пьезотрансформаторов 23, являющихся запоминающими элементами, соеди ены с числовыми шинами, экраннруюпц-ie электроды 24 пьезотрансформаторов объединены по разрядам в экранирующие шины 25. Выходные электроды 26 пьезотрансформаторов объедннены в разрядные щи}1ы 27, которые соединены с входами усилителей считывания 28 в блоке 4. Пьезокерамическне пластины 29 генераторной секции пьезотрапсформаторов имеют жесткую поляризацию. Пластины 30 секции возбуждения могут нметь различную поляризацию, причем направленне ее определено записанной информацией. Экранирующие шины 25 подключены к выходам составных разрядных ключей 31, каждый нз которых состоит из двух ключей: ключа 32, через который экранирующие шины соединены с общей точкой устройства, и ключа 33, через который экранирующие шины соединены с щиной 34 напряжений. Управляющие входы разрядных ключей соединены с выходами регистра числа (регистр на чертеже не показан). Шина 34 через ключ 35 соедииепа с источником напряжения поляризации. Клемма 36 является ун завляющим входом ключа 35. Экранирующие шины 25 через конденсаторы 37 подключены к выходу формирователя 38 противофазных токов считывания.

Устройство работает с.1едуюпи1М об()азом.

Запись информации в устройство по ;,ап)1ому адресу производится с предварительной подготовкой злсмсптов. при этом ранее зап .;сапная информация стирается, что nponajioдится следующим образом.. Все регистра числа устанавливаются в «О и иотеи циалы на выходных шипах регистра открывают ключи 32 и закрывают ключи 33. Отрицательным напряжением только на одном выходе дешифратора соответствующего адреса выбранный ключ 9 открыт. Все остальные невыбранные ключи 9 и 6 закрыты, причем закрыт ключ 6 и выбранного адреса потенциалом на общей щине 8. По сигналу стирания на управляющем входе 14 ключа И напряжение -Up через открытый ключ 9 нрикладывается к выбранной числовой шине 7. И в результате к электродам 22 и 24 пьезотрансформаторов только выбранпого адреса прикладывается нацряжение -Up. Под действием этого напряжения пластины 30 поляризуются в направлениях, соответствующих заниси «О, т. е. стирается ранее записанная информация и данный адрес подготавливается к записи нового числа. Зацнсываемое число принимается в регистр.

При этом под действием потенциалов на выходных щннах регистра экранирующие шины 25, соответствующие тем разрядам регистра числа, которые находятся в «1, нодключаются через ключи 33 к шине 34, а экранирующие

шины 25, соответствующие тем разрядам регистра, которые находятся в состоянии «О, нодключаются через ключи 32 к общей точке. Потенциалом на шиие 21 зацрета включения закрыты все адресиые ключи 9. При этом об1и,ая щина 8 через формирователь 13 подключена к общей точке и отрицательным напряжением на соответствующем выходе дещифратора открыт только один ключ 6 выбранного адреса и соответствующая числовая щина 7 подключена к общей точке. Остальные числовые пшны отключены от общей точки и от щины 10. По сигналу записи на управляющие в.ходы 18, 20 п 36 ключей 16, 19 и 35 поступают сигналы и эти ключи открываются. При этом к

электродам элемеитов выбраппого числа, в которые записываются «1, прикладывается напряжение , а электроды элементов, в которые занисываются «О, закорочены. К электродам элементов невыбранных адресов прии.

;ладывается разница напряжений, равная

Up - -g-. Под действием

напряжения +t/p

или

выбранные элементы устанавливаются в состояние, соответствующее «1, а состояние выбранных элементов остается нрежним, т. е. ОКИ находятся в состоянии, которое было задано при стирании информации. Таким образом, после операции стирания и

заниси информации п.тастины 30 выбранных элементов поляризуются в направлениях в соответствии с кодом записываемого числа. Иапряжеиие, которое нри этом прикладывается л электродам нев1 бранных элементов,

являегся недостаточным для изменения поляризации иласгии 30 и разреше1Н я или записи ложной информации в пезыбранных адресах не н)оисходит. В режиме считывания шгформании потенц 1аламн с выходов регистра числа открыты

ключи 32 и все шины 25 подключены к общей точке. С соответствующего выхода дешифратора поступает отрицательный потенциал на основной управляющий вход выбранного адресного ключа 5. При этом открывается только ключ 9, ключ 6 закрыт потеициалом на шине 8. По сигналу чтения на входе 39 формирователей с выхода формирователя 13 в шину 10 цоступает импульс тока заряда, который через открытый ключ 9 прикладывается к входам выбранных запоминающих элементов, заряжая их до напряжения считывания (L/сч)Одно:Временно с этим с выхода формирователя 38 поступает имлульс тока, равный по величине, по противоположной полярности току формирователя 13. После этого со второго выхода фор иирователя 13 поступает импульс тока разряда (по полярности противоположный току заряда), который через открывающийся ключ 6 выбранного адреса прикладывается к входам выбранных элементов, разряжая их от напряжения f/сч считывания до исходного состояния. Одновременно с током разряда с выхода формирователя 38 поступает импульс тока, равный по величине, но противоположный по полярности току формирователя 13. При этом к входам элементов выбранного числа прикладываются импульсы напряжения возбуждения, в результате чего на разрядных шинах 27 появляются импульсы напряжения, полярность которых определяется направлением поляризации пластин 30, т. е. записанной информацией. Эти импульсы по разрядным шинам поступают на входы усилителей считывания 28.

В описанном устройстве для тока заряда и тока разряда образованы допол)1ительная цепь, состоящая из конденсаторов 37 и формирователя 38, которая исключает протекание

этих токов через ключи 32. Этим обеспечивается постоянное значение потенциала шин 25 и исключается составляющая сигнала помехи, обусловленная падением напряжения на динамических сопротивлениях ключей 32, так

как при считывании через них не протекают токи заряда и разряда входных емкостей запоминающих элементов.

Пред м ет изобретения

15

Запоминающее устройство, содержащее матрицу широкополосных льезотрансформаторов, разрядные шины которой подключены к усилителям считывания, экранирующие шины - к выходам разрядных ключей, числовые шииы - к выходам адресных ключей, соединенных с общей шиной и с управляющей шииой, подсоединенной к ключу, связанному с источииком напряжения поляризации, формирователь токов считывания, отличающееся тем, что, с целью повышения помехозашищенности и увеличения информационной емкости устройства, оно содержит дополнительный формирователь противофазных токов сч)1тывания, выход которого через соответствующие элементы связи подключен к экранирующим шинам, обшая шииа подключена к одному из выходов формирователя токов считываиия, другой выход которого соединен с управляющей шиной.

И регистру числа

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

Авторы

Даты

1975-08-15—Публикация

1973-07-19—Подача