1

Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах (ЗУ) цифровых вычислительных машин.

В известных ЗУ для обращения к ячейке памяти необходимы два такта: такт считывания (при записи информации в этом такте ячейка памяти обнуляется) и такт записи (При считывании информации из ЗУ в этом такте восстанавливается содержимое ячейки памяти). В некоторых случаях, например при использовании ЗУ в качестве буферного, восстановления считанной информации не требуется и поэтому для повышения эффективного быстродействия используется режим считьивания без регенерации.

Однако в таких ЗУ при записи информации в ячейку памяти, из которой информация ранее была считана без регенерации, производится еще раз обнуление уже свободной ячейки.

Целью изобретения является повышение эффективного быстродейсивия ЗУ за счет исключения такта считывания при записи информации в свободную ячейку памяти. Это достигается путем добавления в накопитель ЗУ разряда, хранящего информацию о занятости ячейки памяти, и использования специального алгоритма обращения к ЗУ. В режиме считывания без регенерации в этот разряд записывается О, а нри любом другом обращении к ЗУ этот разряд хранит 1. Цикл записи начинается с такта записи и, если в дополнительном разряде хранится О, состоит из одного такта записи. Если же в дополнительном разряде хранится 1, то вслед за тактом записи выполняется такт коррекции, в котором производится считьшапие в тех разрядах, где производится запись 0.

Предлагаемое устройство отличается от известных тем, что оно содержит в накопителе дополнительный разряд, соединенный с входом усилителя воспроизведения дополнительного разряда и выходом однополярного формирователя тока запрета, причем выход усилителя воспроизведения подключен к входу

блока управления, выход которого соединен с входом однополярного формирователя тока запрета.

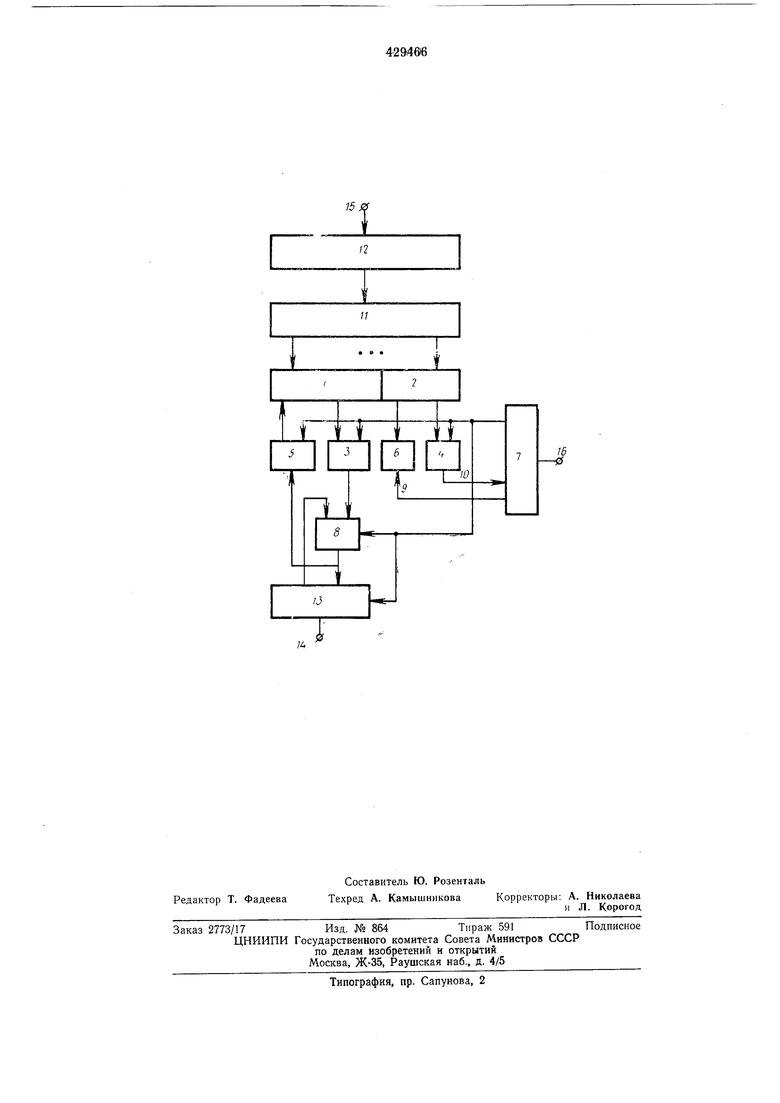

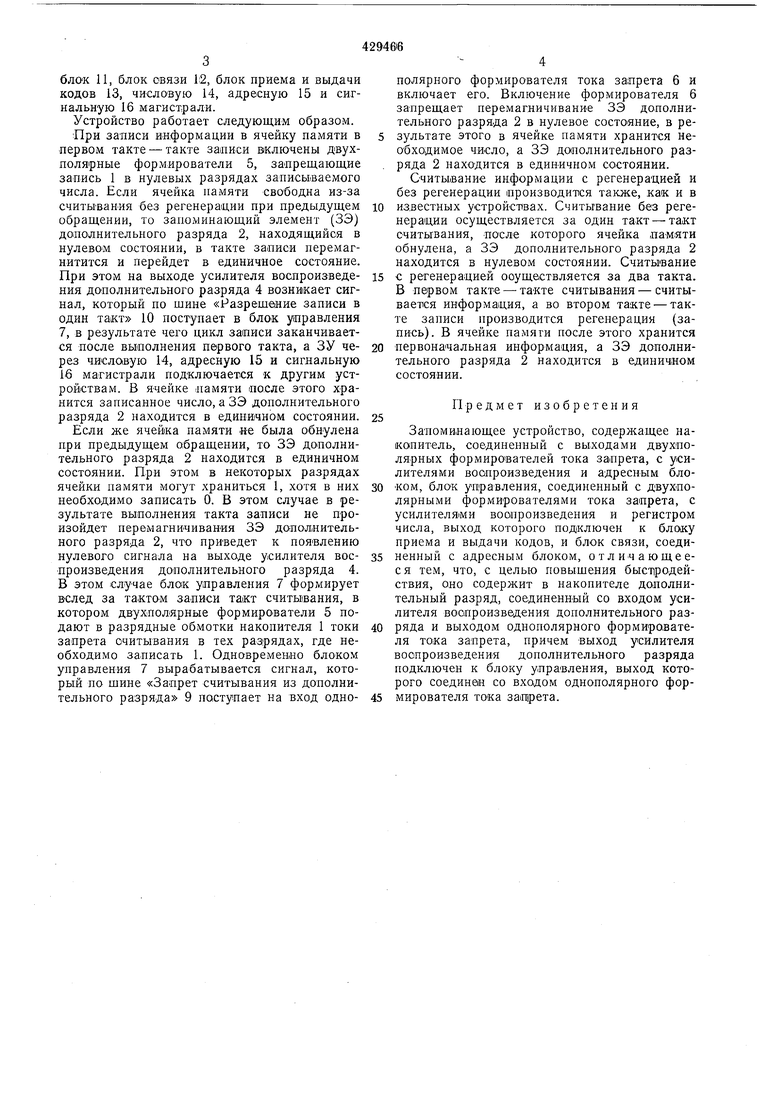

На чертеже изображена структурная схема предлагаемого устройства.

Устройство включает накопитель 1 с дополнительным разрядом 2, усилители воспроизведения 3, усилитель воспроизведения дополнительного разряда 4, двухполярные формирователи тока запрета 5, однополярный формирователь тока запрета ,6, блок управления 7, регистр числа 8, щнну «Запрет считывания из дополнительного разряда 9 и шину «Разрещение записи в один такт 10, адресный

блок и, блок связи 12, блок приема и выдачи кодов 13, числовую 14, адресную 15 и сигнальную 16 магистрали.

Устройство работает следующим образом.

При записи информации в ячейку памяти в первом такте - такте записи включены двухполярные формирователи 5, запрещающие запись 1 в нулевых разрядах записываемого числа. ЕСЛИ ячейка памяти свободна из-за считывания без регенерации при предыдущем обращении, то запоминающий элемент (ЗЭ) дополнительного разряда 2, находящийся в нулевом состоянии, в такте записи перемагнитится и перейдет в единичное состояние. При этом на выходе усилителя воспроизведения дополнительного разряда 4 возникает сигнал, который по шине «Разрешение записи в один такт 10 поступает в бло« управления 7, в результате чего цикл записи заканчивается после выполнения первого такта, а ЗУ через числовую 14, адресную 15 и сигнальную 16 магистрали подключается к другим устройствам. В ячейке памяти после этого хранится записанное число, а ЗЭ дополнительного разряда 2 находится в единичном состоянии.

Если же ячейка памяти «е была обнулена при предыдущем обращении, то ЗЭ дополнительного разряда 2 находится в единичном состоянии. При этом в некоторых разрядах ячейки памяти могут храниться 1, хотя в них необходимо записать 0. В этом случае в результате выполнения такта записи не произойдет перемагничивания ЗЭ дополнительного разряда 2, что приведет к появлению нулевого сигнала на выходе усилителя воспроизведения дополнительного разряда 4. В этом случае блок управления 7 формирует вслед за тактом записи такт считывания, в котором двухпол1ярные формирователи 5 подают в разрядные обмотки накопителя 1 токи запрета считывания в тех разрядах, где необходимо записать 1. Одновременно блоком управления 7 вырабатывается сигнал, который по шине «Запрет считывания из дополнительного разряда 9 поступает на вход однополярного формирователя тока запрета 6 и включает его. Включение формирователя 6 запрещает перемагничивание ЗЭ дополнительного разряда 2 в нулевое состояние, в результате этого в ячейке памяти хранится необходимое число, а ЗЭ дополнительного разряда 2 находится в единичном состоянии.

Считывание информации с регенерацией и без регенерации производит1ся также, как и в

известных устройствах. Считывание без регенерации осуществляется за один такт - такт считывания, после которого ячейка па-м;яти обнулена, а ЗЭ дополнительного разряда 2 находится в нулевом состоянии. Считывание

с регенерацией осуществляется за два такта. В первом такте--такте считывания - считывается информация, а во втором такте - такте записи производится регенерация (запись). В ячейке памяти после этого хранится

первоначальная информация, а ЗЭ дополнительного разряда 2 находится в единичном состоянии.

Предмет изобретения

Запоминающее устройство, содержащее накопитель, соединенный с выходами двухполярных формирователей тока запрета, с усилителями воспроизведения и адресным блоком, блок управления, соединенный с двухполярными формирователями тока запрета, с усилителями воопроизведения и регистром числа, выход которого подключен к блоку приема и выдачи кодов, и блок связи, соединенный с адресным блоком, отличающееся тем, что, с целью повышения быстродействия, оно содержит в накопителе дополнительный разряд, соединенный со входом усилителя воспроизведения дополнительного разряда и выходом однополярного формирователя тока запрета, причем выход усилителя воспроизведения дополнительного разряда подключен к блоку управления, выход которого соединен со входом однополярного формирователя тока за1П1рета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| Логическое запоминающее устройство | 1972 |

|

SU464017A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Формирователь импульсов разрядныхТОКОВ зАпиСи | 1979 |

|

SU849298A1 |

| Запоминающее устройство | 1974 |

|

SU487417A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

Даты

1974-05-25—Публикация

1973-01-05—Подача