Предлагаемое изобретение относится к области вычислительной техники, в частности к запоминающим элементам и может применяться в цифровых дифференциальных анализаторах (ЦДА), в ряде устройств ЦВМ с десятичной системой счисления, а также в преобразователях прямого двоично-десятичного кода 8-4-2-1 в десятиуровневый код.

Известны многоуровневые запоминающие элементы (МЗЭ), выполненные на интегральных числовых линейках с двумя отверстиями на разряд, сечения перемычек которых между отверстиями каждого разряда равны друг другу и в два раза меньше сечения перемычек между отверстиями соседних разрядов.

Однако эти элементы не позволяют преобразовывать двоично-десятичный код 8-4-2- 1 в десятиуровневый код, что значительно сужает их функциональные возможности и область применения.

Цель изобретения - расширить область применения известного запоминающего элемента.

Поставленная цель достигается тем, что шина первого разряда прошита встречно через оба отверстия первого разряда, шипа второго разряда прошита через второе отверстие одноименного разряда, шины третьего и четвертого разрядов прошиты согласно через соответствующую пару отверстий одноименных разрядов, выходная обмотка прошита встречно

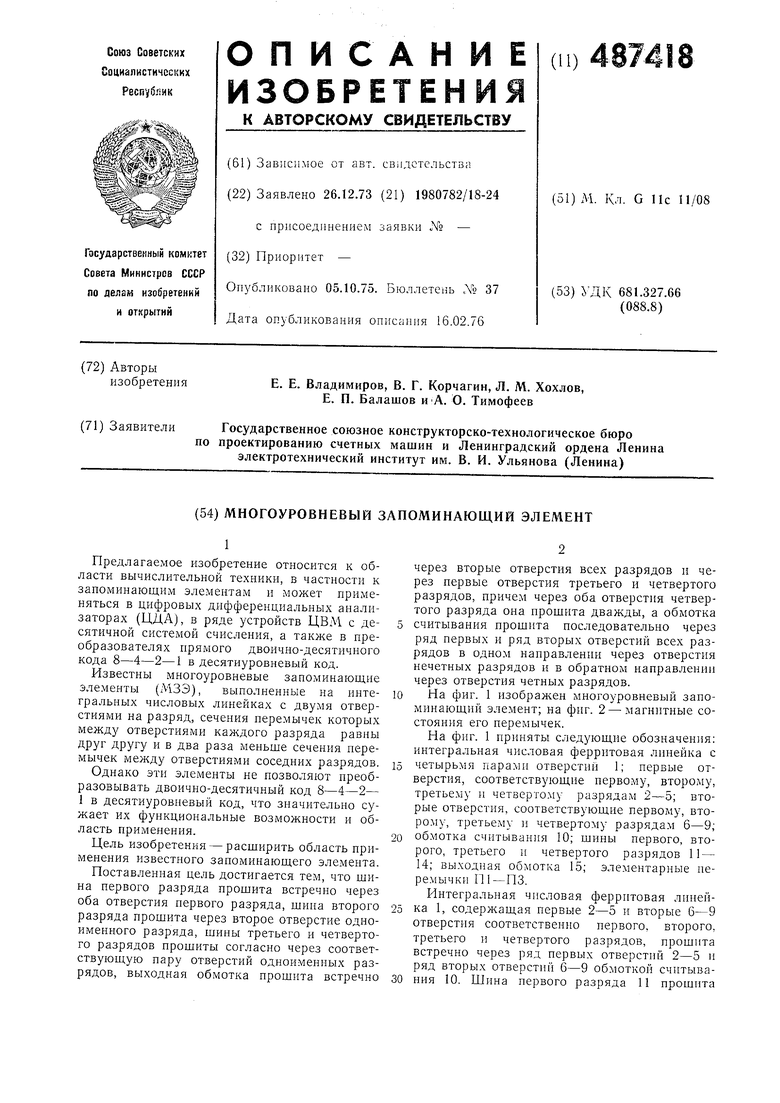

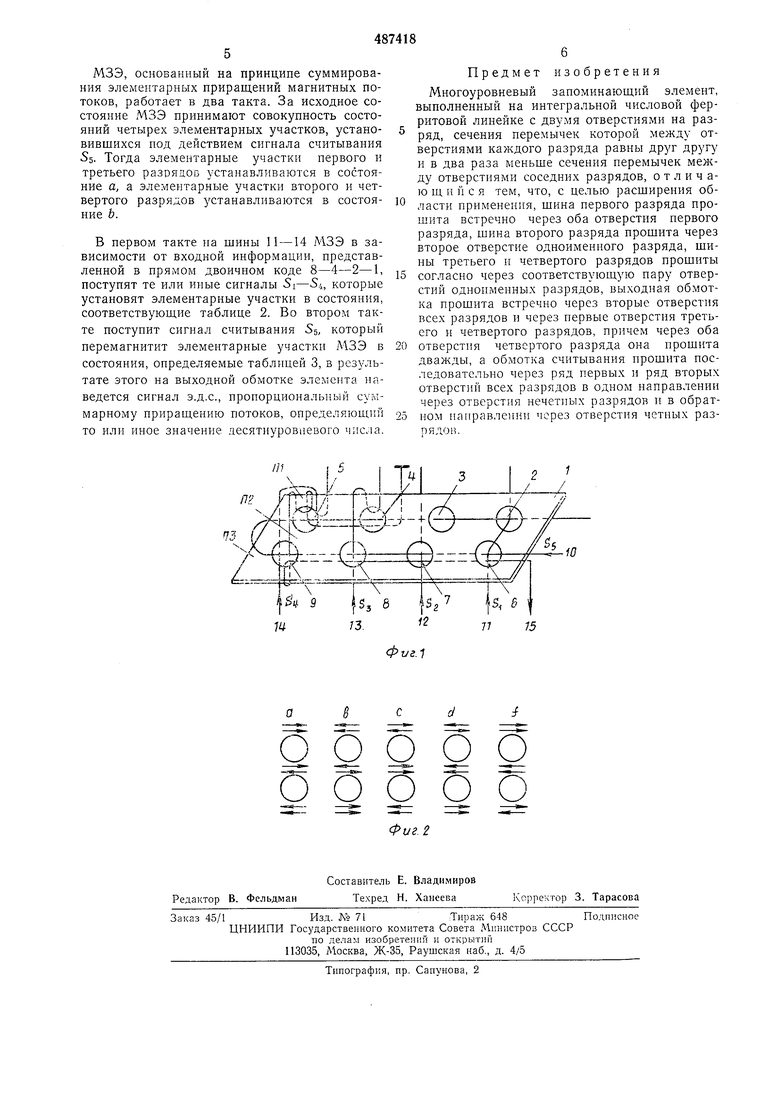

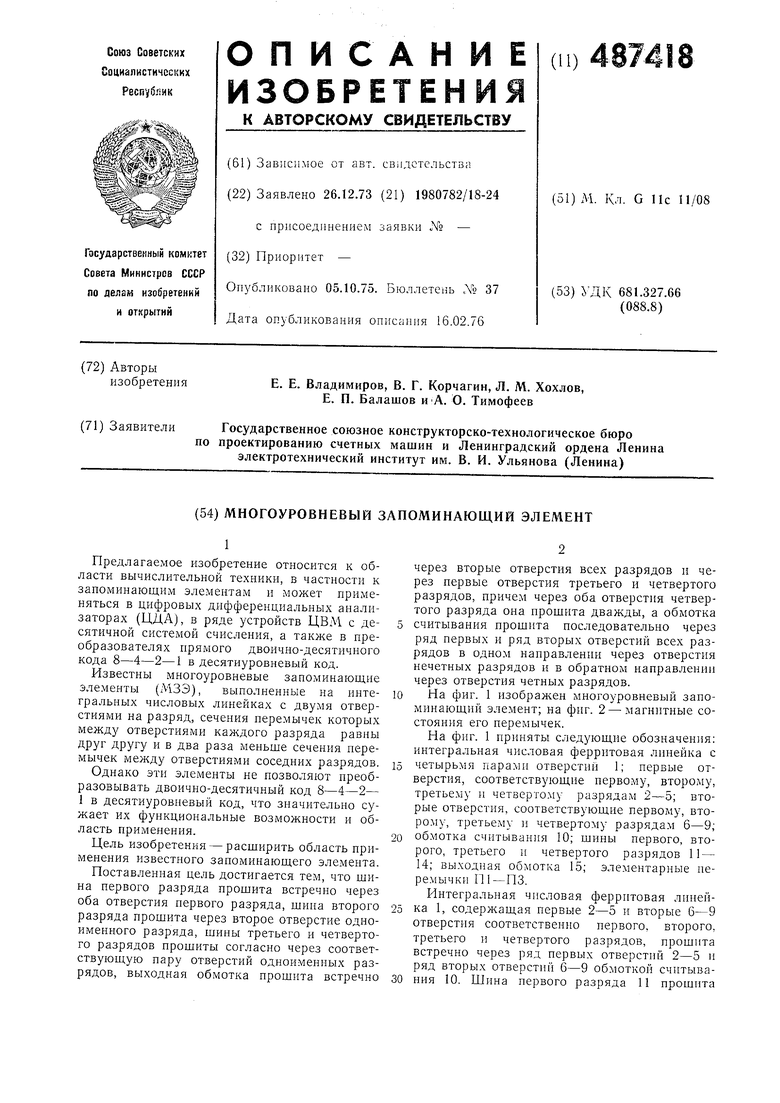

через вторые отверстия всех разрядов и через первые отверстия третьего и четвертого разрядов, причем через оба отверстия четвертого разряда она прошита дважды, а обмотка считывания прошита последовательно через ряд первых и ряд вторых отверстий всех разрядов в одном направлении через отверстия нечетных разрядов и в обратном направлении через отверстия четных разрядов. На фиг. 1 изображен многоуровневый запоминающий элемент; на фиг. 2 - магнитные состояния его перемычек.

На фиг. 1 приняты следующие обозначен 1я: интегральная числовая ферритовая линейка с четырьмя парами отверстий 1; первые отверстия, соответствуюшие первому, второму, третьему и четверто.му разрядам 2-5; вторые отверстия, соответствующие первому, второму, третьему и четвертому разрядам 6-9; обмотка считывания 10; шины первого, второго, третьего и четвертого разрядов 11 - 14; выходная обмотка 15; элементарные перемычки П 1-ИЗ.

Интегральная числовая ферритовая линейка 1, содерл ащая первые 2-5 и вторые 6-9

отверстия соответственно первого, второго,

третьего и четвертого разрядов, прошита

встречно через ряд первых отверстий 2-5 и

ряд вторых отверстий 6-9 обмоткой считывания 10. Шина первого разряда 11 прошита

встречно через первое 2 и второе 6 отверстия первого разряда, шина второго разряда 12 прошита через второе 7 отверстие второго разряда, а шина третьего и четвертого разрядов прошиты согласно через одноименные отверстия 3, 8 и 5, 9 третьего н четвертого разрядов. Выходная обмотка 15 прошита встречно через отверстия 6-9, 5 и 3, причем через отверстия 5 и 9 дважды.

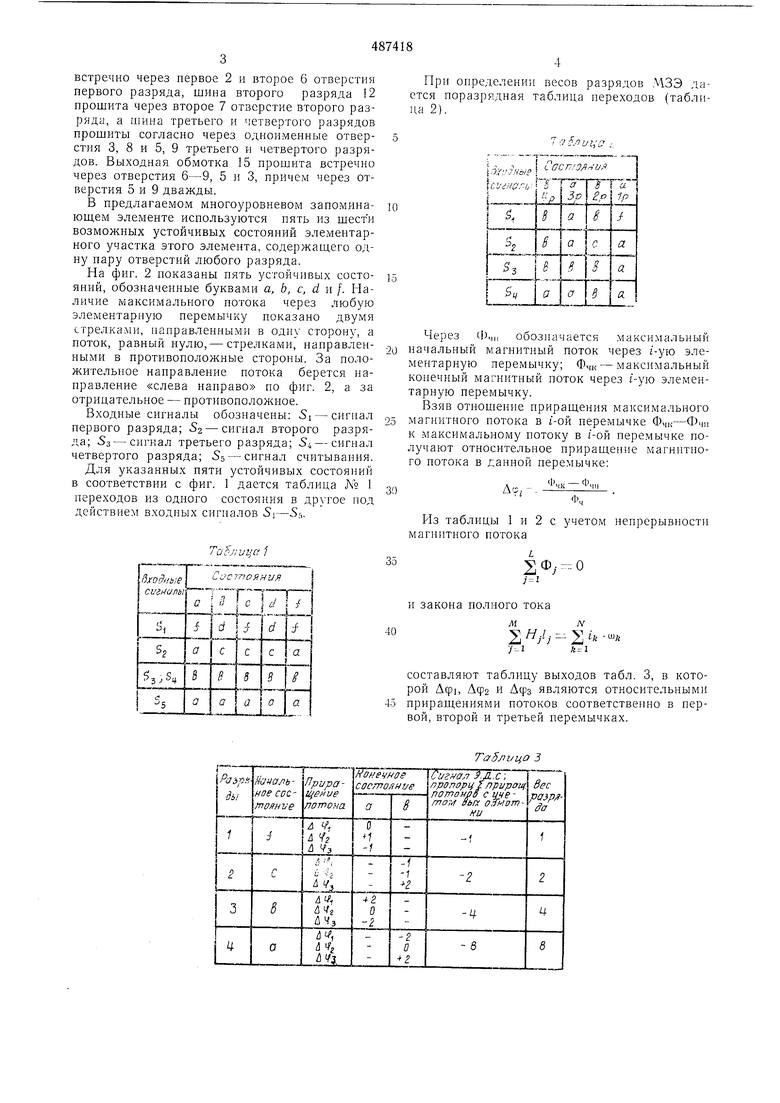

В предлагаемом многоуровневом запоминаюш,ем элементе используются пять из шести возможных устойчивых состояний элементарного участка этого элемента, содержашего одну пару отверстий любого разряда.

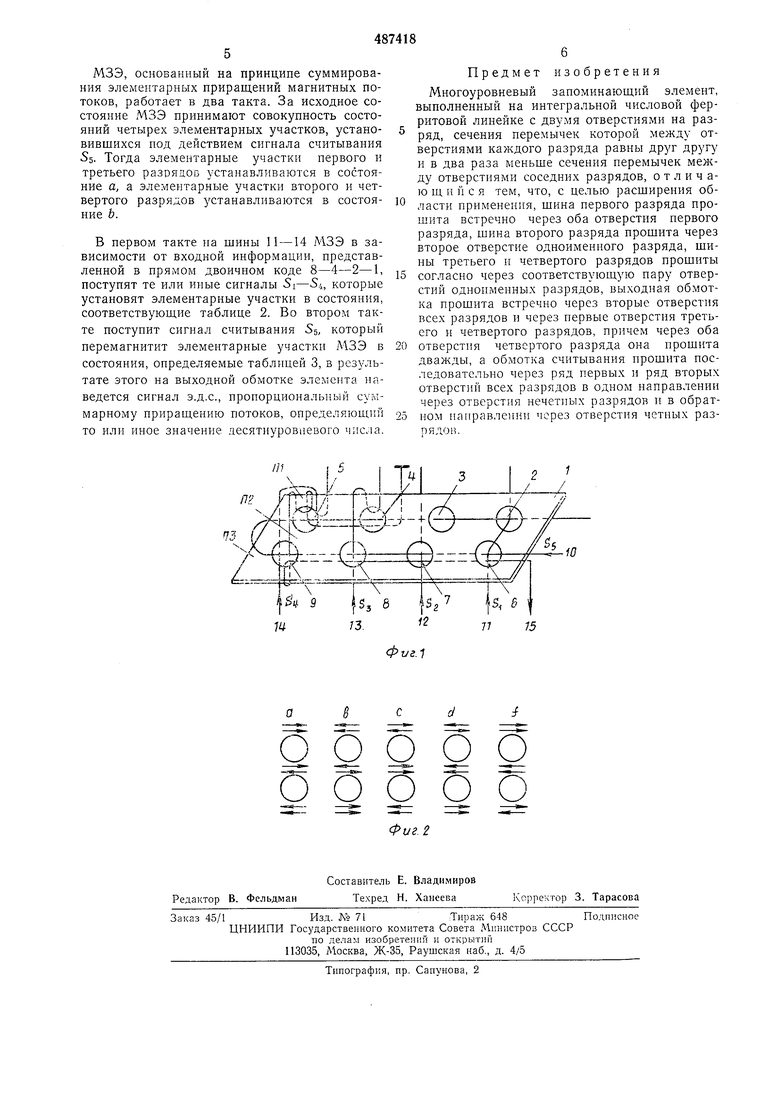

На фиг. 2 показаны пять устойчивых состояний, обозначенные буквами а, Ь, с, d и /. Наличие максимального потока через любую элементарную перемычку показано двумя стрелками, направленными в одну сторону, а поток, равный нулю, - стрелками, направленными в противоположные стороны. За полол ительное направление потока берется направление «слева направо по фиг. 2, а за отрицательное - противоположное.

Входные сигналы обозначены: 5i - сигнал первого разряда; 2 - сигнал второго разряда; Зз - сигнал третьего разряда; S - сигнал четвертого разряда; Ss -сигнал считывания.

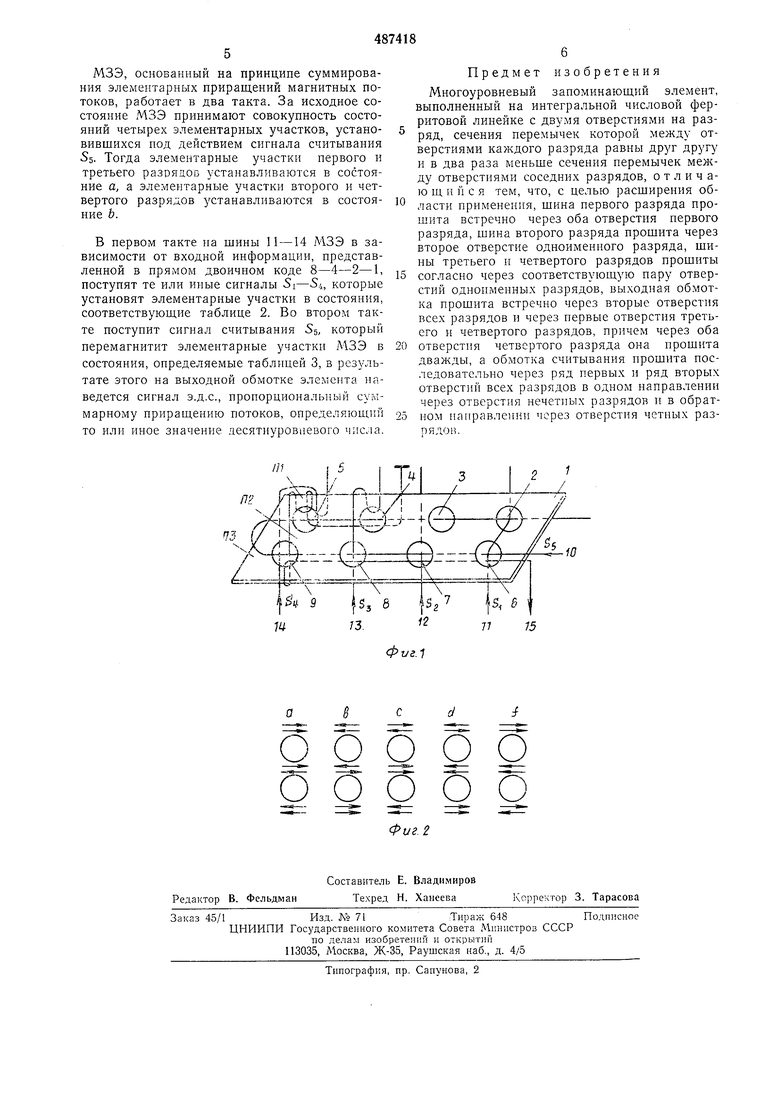

Для указанных пяти устойчивых состояний в соответствии с фиг. 1 дается таблица Ni 1 переходов из одного состояния в другое под действием входных сигналов Si-S-,.

Tcifj:vva 1

входные

.4 j , Г

с и г:- а ЛЬ:

. Ч С d

При определении весов разрядов дается поразрядная таблица переходов (таблица 2).

Через и)ч11 обозначается максимальный начальный магнитный поток через г-ую элементарную перемычку; Фчк - максимальный конечный магнитный поток через г-ую элементарную перемычку.

Взяв отношение ирирашения максимального магнитного потока в t-ой перемычке Фчк-Фчп к максимальному потоку в -ой перемычке получают относительное прираш,ение магнитного потока в ;;анной перемычке;

д ,,Ф.к-Ф.,„ , Фч

Из таблицы 1 и 2 с учетом ненрерывности магнитного потока

Ефу-о

и закона полного тока

Л1Л

2 .-.

У-1

составляют таблицу выходов табл. 3, в которой ДФ1, АФ2 и Дфз являются относительными 45 приращениями потоков соответственно в первой, второй и третьей перемычках.

МЗЭ, основанный на принципе суммирования элементарных приращений магнитных потоков, работает в два такта. За исходное состояние МЗЭ принимают совокупность состояний четырех элементарных участков, установившихся под действием сигнала считывания Ss. Тогда элементарные участкн первого и третьего разрядов устанавливаются в состояние а, а элементарные участки второго и четвертого разрядов устанавливаются в состояние Ь.

В первом такте на шины И -14 МЗЭ в зависимости от входной информации, представленной в прямом двоичном коде 8-4-2-1, поступят те или иные сигналы Si-S/, которые установят элементарные участки в состояния, соответствующие таблице 2. Во втором такте поступит сигнал считывания S, который перемагнитит элементарные участки МЗЭ в состояния, онределяемые таблицей 3, в результате этого на выходной обмотке элемента наведется сигнал э.д.с., пропорциональный суммарному приращению потоков, определяющий то или иное значение десятиуровневого числа.

т

Предмет изобретения

Многоуровневый запоминающий элемент, выполненный на интегральной числовой ферритовой линейке с двумя отверстиями на разряд, сечения перемычек которой между отверстиями каждого разряда равны друг другу и в два раза меньше сечения перемычек мелсду отверстиями соседних разрядов, о т л и ч аю щ и и с я тем, что, с целью расширения области применения, шина первого разряда прошита встречно через оба отверстия первого разряда, шина второго разряда прошита через второе отверстие одноименного разряда, шины третьего и четвертого разрядов прошиты согласно через соответствующую пару отверстий одноименных разрядов, выходная обмотка прошита встречно через вторые отверстия всех разрядов и через первые отверстия третьего и четвертого разрядов, причем через оба отверстия четвертого разряда она прошита дважды, а обмотка считывания ирошита последовательно через ряд первых и ряд вторых отверстий всех разрядов в одном направлении через отверстия нечетных разрядов и в обратном наггравлеиии через отверстия четных разпядон.

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневый эапоминающий элемент | 1973 |

|

SU492932A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| МАГНИТНЫЙ НАКОПИТЕЛЬ | 1973 |

|

SU385315A1 |

| Магнитный запоминающий элемент | 1975 |

|

SU538422A1 |

| Магнитный запоминающий элемент | 1974 |

|

SU520621A1 |

| Числовой блок для запоминающего устройства | 1975 |

|

SU542242A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| Запоминающее устройство | 1973 |

|

SU481938A1 |

| Магнитное запоминающее устройство | 1974 |

|

SU532132A1 |

| Магнитный запоминающий элемент | 1975 |

|

SU516098A1 |

Авторы

Даты

1975-10-05—Публикация

1973-12-26—Подача