(54) МНОГОУРОВНГгВЫИ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневый запоминающий элемент | 1973 |

|

SU487418A1 |

| Магнитный запоминающий элемент | 1975 |

|

SU538422A1 |

| Запоминающее устройство | 1973 |

|

SU481938A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНО-п-ИЧНОГО КОДА | 1973 |

|

SU387360A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ | 1973 |

|

SU430442A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| Магнитный запоминающий элемент | 1975 |

|

SU610173A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Числовой блок для запоминающего устройства | 1975 |

|

SU542242A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении различных устройств для переработки дискретной информации с мно- Гоуровневьм представлением.

Известны многоуровневые запоминающие элементы, содержащие интегральную ферритовую линейку с двумя отве Х;ти. ями на разряд, сечения перемычек которой между отверстиями каждого разряда равнц друг друту и в два раза меньше сечения перемычек между отверстиями соседних разрядов, шину первого разряда, прошитую встречно через оба отверстия первого раз ряда, шину второго разряда, прошитую через второе отверстие одноименного раз рйда, ШИНУ третьего разряда, прошитую через оба отверстия одноименного разряду, обмотку считывания, проиш ю последов тельно через ряд первых и ряд вторых отверстий всех разрядов в одном нйправпёнии через отверстия нечетных раэ 1ЯДОБ и в iflpyfOM направлении через отверстия четных разрядов и выходную обмотку.

Однако эти элементы не позволяют преобразовать код 2-4-2-1 в десятиурОЕУ невый код, что значительно ограничивает область их применения.

Цель изобретения - расширение облас1|1 применения элемента.

Достигается это тем, что элемент содержит шину четвертого разряда, прошитую через вторые отверстия всех разрядов.

На фиг. 1 изображен многоуровневый .запоминающий элемент, на фиг. 2 - магнитные состояния отдельных участков элем-;Нта.

Запоминающий элемент содержит инт&-гральную числовую ферритовую линейку 1 с четырьмя парами отверстий, из который первые отверстия 2-5 соответствуют 1-4i разрядам, вторые отверстия 6-9 соответн) ствуют 1-4 разрядам; обмотку считывания 1О; шины 11-14 1-4-го разрядоп выходную обмотку 15; элементарные перфмычки П 1- ПЗ.

Интегральная чисповья ферритовая линейка 1, содержащая первые и втарые 6-9 отверстия соответственно 1-4 разрядов, прошита встречно через ряд первых отверстий и ряд вторых отверстий обмоткой сягитьгеания 10. Шина 11 перво го разряда прошита через первое 2 и второе 6 отверстий первого разряда встречн но, шины BTOpOiXj 12 и четвертого 14 разрядов пропущены Соответственно через второе отверстие 7 второго разряда. я второе отверстие 9 четвертого разряда, а шкмна третьего разряда 13 прошита согласно через отверстия 4 и 8 третьего разряда. Выходная обмотка 15 прошита встречно через вторые отверстия 6-9 соответствен- ко 1-.4-ГО разрядов и через первое отверотие 4 третьего разряда.

В продложенном многоуровневом запоминающем элементе (МЗЭ) используются пять из шести возможных устойчнвьк состояний элементарного участка этогоэде- мента, содержащего одну пару отверстий любого разряда.

Эти пять устойчивых состояний, обозначены } буквами а, b , С , Ct и f .

Наличие максимального потока через любую элементарную лерекагчку обозначено двумя стрелками, направленными в одну сторону, е. попхж, равный нулю, -стреяками, направлен .еыми в противоположные стороны. За лоложительное направление потока принято направление слева направо, а за отри цательно& противоположное.

Входные сигналы обозначены следук шим образом:S - сигнал первого

разряда, $2 - сигнал второго рпзряда,

S сигнал третьего разряда, S

V погнал четвертого разряда и S - сигнал считывания,

Для указанных пяти устойчивых состояний в соответствии с фиг. 1 составлена таблица переходов из одного состояния в другюе под действием входных сигналов $л - S| , (табл. 1).

При определении весов разрядов МЗЭ используется поразрядная таблица переходов (таб,1ица 2).

Взяв отношение приращения максимального магнитного потока в L -.ой перв4

мычке ( - Фцр ) щ максимальному потоку в t -ой перемы ке, получим

..--,

5Фц

где д Уб - относительное приращение

магнитного потока в О ой перемычке,;, ф - максимальный начальный

поток через i/ , элементарную перемычку;

максимальный конечный

1агни ный потек через 1 -ую эл9мента{ -. яую перемычку.

Из табл. 1 и 2 с учетом основных з конов коммутации магнитного потока получена таблица (табл. 3), в которой д. V.J , А f J., U 3 являются относительными приращениями потоков соответственно в 1-3-ей перемычках.

Предложенный элемент, основанный на принципе суммирования элементарных при- рашений магнитных потоков, работает в два такта. За исходное состояние многоуровнего запоминающего элемента принята совокупность состояний; четырехэлементар- яых участков, установившихся под дейст ; вием сигнала считывания 5. Тогда элементарные участки первого и третьего разря-: дов установятся в состоянии d, а элементарные участки второго и четвертого раэрядов установятся в состояние Ь-

В первом такте на шины 11-14 МЗЭ, в зависимости от входной информации, пред:ставленпой. к коде Айкена, поступят те или иные входные сигналы Ь 7 5ц,

которые установят элементарные участки в состояния.,, соответствующие табл. 2.

Во влхэрО14 такте поступит сигнал считы. вания Sr , который перемагнитит элементарные участки МЗЭ в состояния, определяемые табл. 3; результате этого на выходной обмотке элемента наведется сигнал Э.Д.С., пропорциональный суммарному приращению потоков, определяющий то или иное значение десятиуровневого числа.

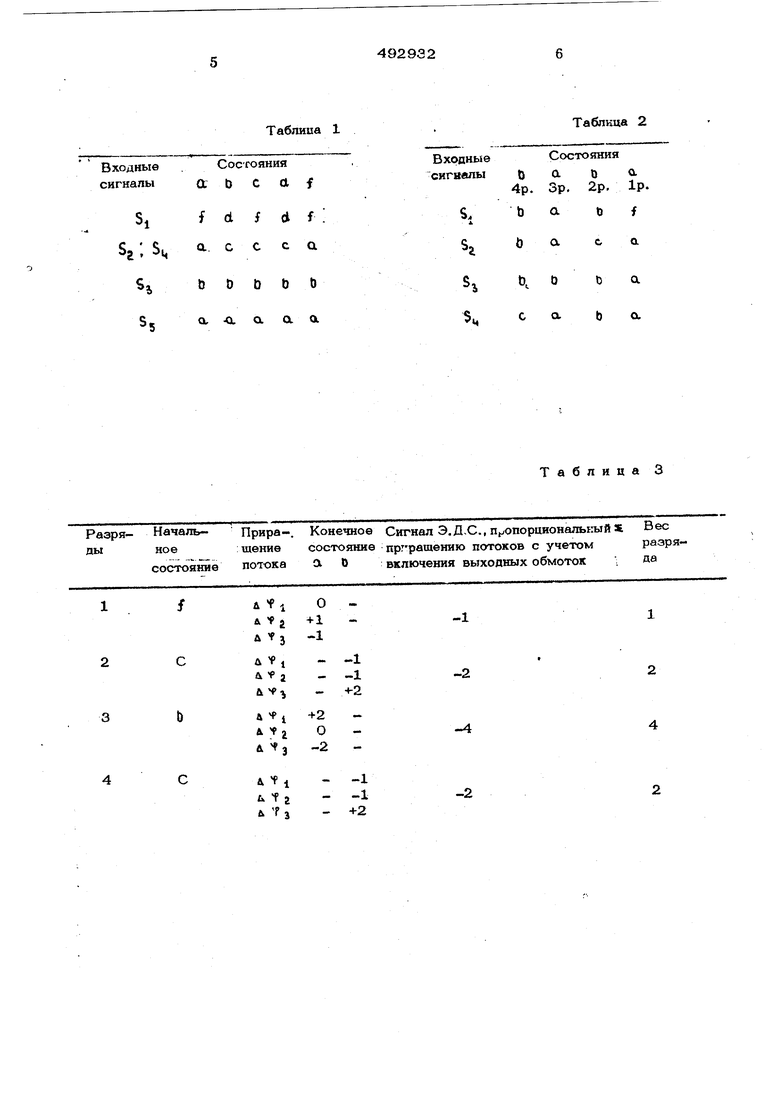

Таблица 1

Таблица 2

Таблица 3

Авторы

Даты

1975-11-25—Публикация

1973-12-26—Подача