управляющие входы кольцевого маркерного регистра 3.

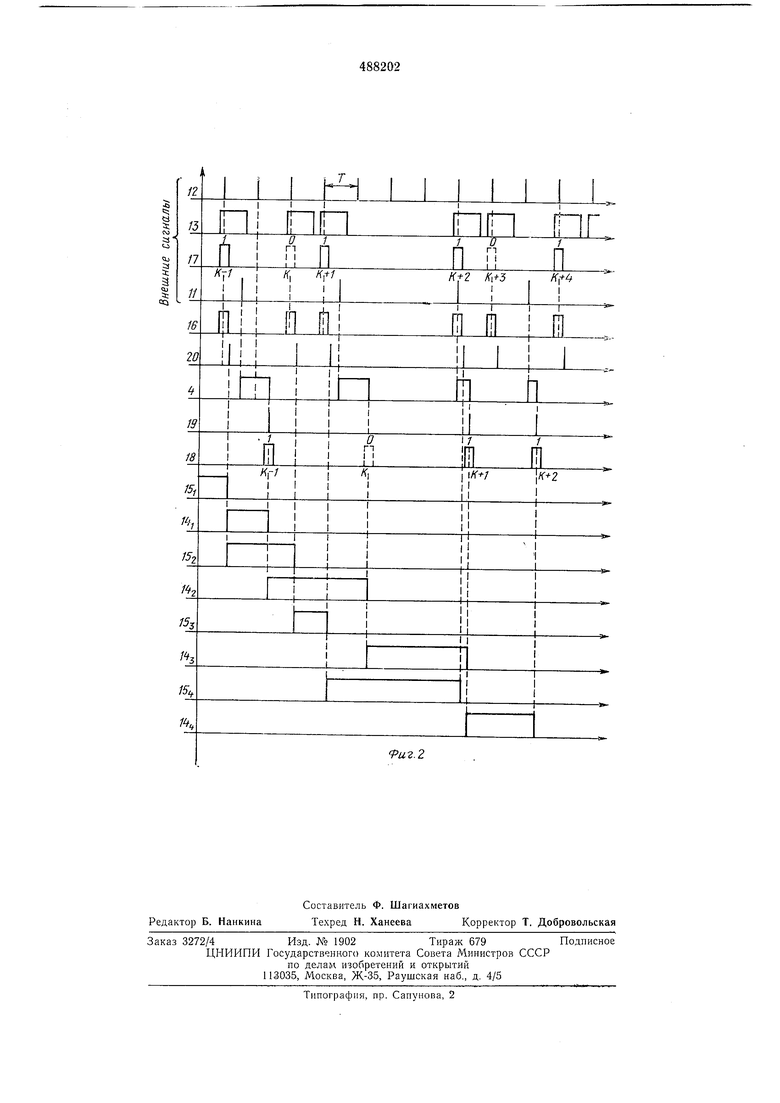

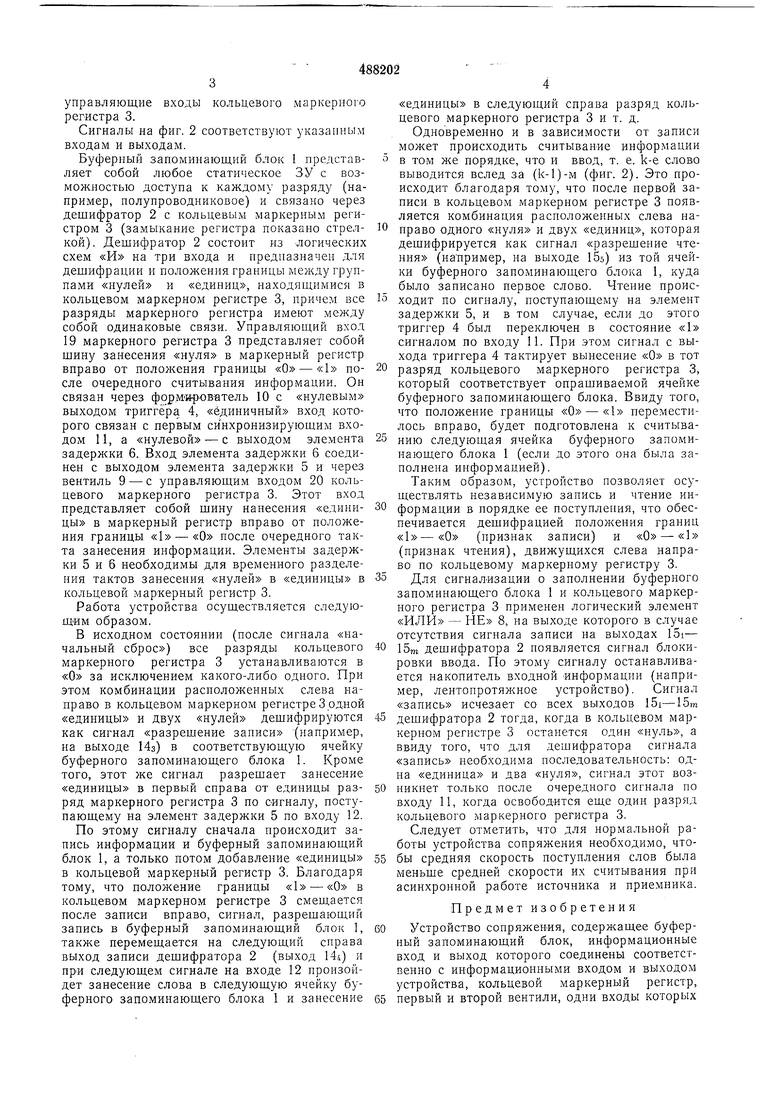

Сигналы на фиг. 2 соответствуют указанным входам и выходам.

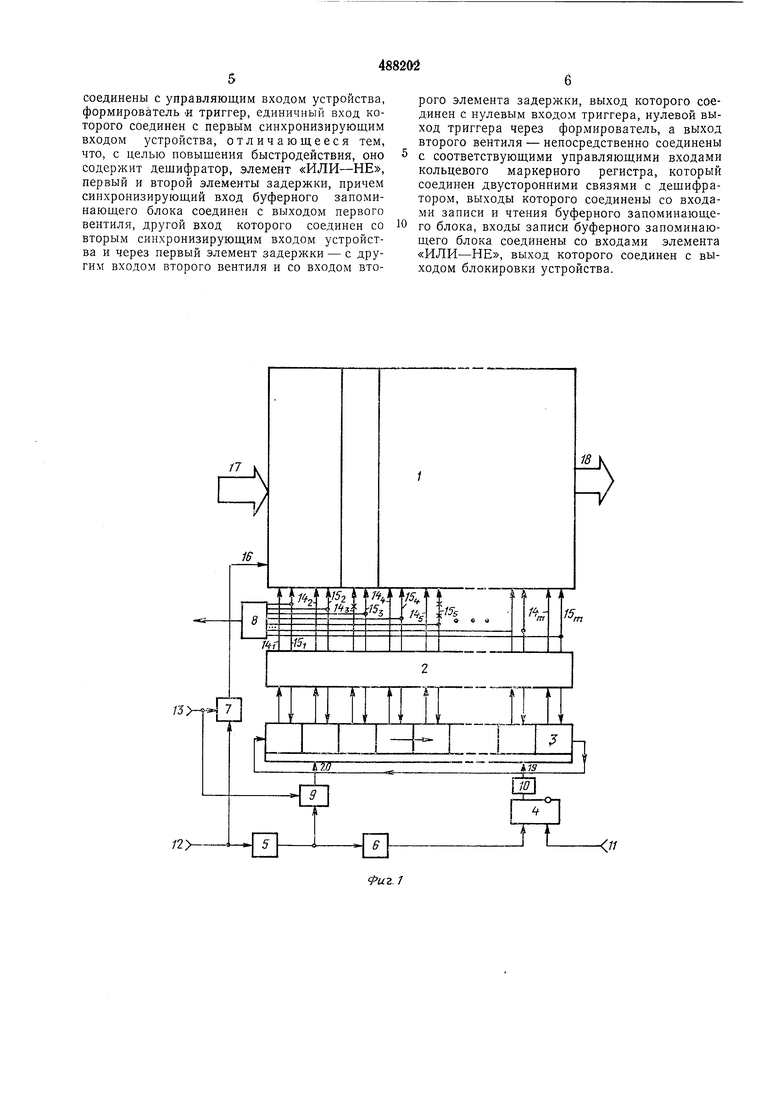

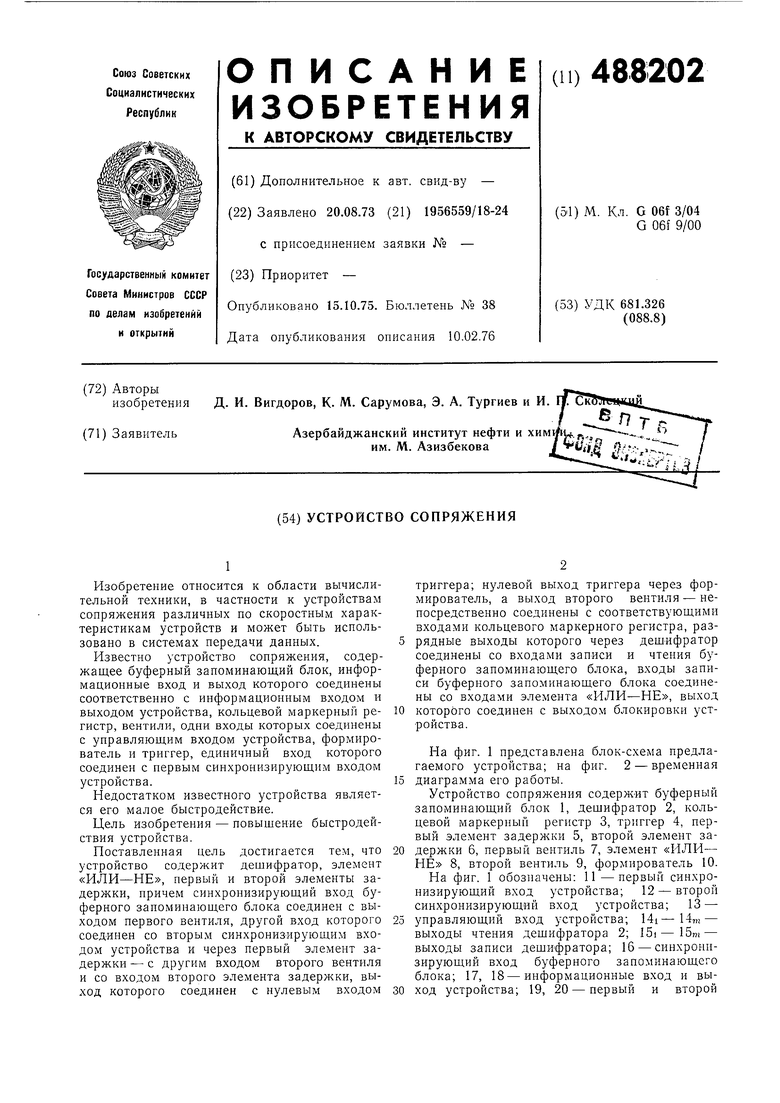

Буферный заноминающий блок 1 представляет собой любое статическое ЗУ с возможностью доступа к каждому разряду (например, полупроводниковое) и связано через дешифратор 2 с кольцевым маркерным регистром 3 (замыкание регистра показано стрелкой). Дешифратор 2 состоит из логических схем «И на три входа и нредназначеп для дешифрации и положения границы между группами «нулей и «единиц, находящимися в кольцевом маркерном регистре 3, причем все разряды маркерного регистра имеют между собой одинаковые связи. Управляюш.ий вход 19 маркерного регистра 3 представляет собой шину занесения «нуля в маркерный регистр вправо от полол ения границы «О - «1 после очередного считывания информации. Он связан через форм ров-нтель 10 с «нулевым выходом триггера 4, «единичный вход которого связан с первым синхронизируюшим входом 11, а «нулевой - с выходом элемента задержки 6. Вход элемента задержки 6 соединен с выходом элемента задержки 5 и через вентиль 9 - с управляющим входом 20 кольцевого маркерного регистра 3. Этот вход представляет собой шину нанесения «единицы в маркерный регистр вправо от положения границы после очередного такта занесения информации. Элементы задержки 5 и 6 необходимы для временного разделения тактов занесения «нулей в «единицы в кольцевой маркерный регистр 3.

Работа устройства осушествляется следующим образом.

В исходном состоянии (после сигнала «начальный сброс) все разряды кольцевого маркерного регистра 3 устанавливаются в «О за исключением какого-либо одного. При этом комбинации расположенных слева наираво в кольцевом маркерном регистре 3 одной «единицы и двух «нулей дешифрируются как сигнал «разрешение записи (например, на выходе Из) в соответствующую ячейку буферного запоминающего блока 1. Кроме того, этот же сигнал разрешает занесение «единицы в первый справа от единицы разряд маркерного регистра 3 по сигналу, поступающему на элемент задержки 5 по входу 12.

По этому сигналу сначала происходит запись информации и буферный запоминающий блок 1, а только потом добавление «единицы в кольцевой маркерный регистр 3. Благодаря тому, что положение границы «1 - «О в кольцевом маркерном регистре 3 смещается после записи вправо, сигнал, разрешающий запись в буферный запоминающий блок 1, также перемещается на следующий справа выход записи дешифратора 2 (выход 144) и при следующем сигнале на входе 12 произойдет занесение слова в следующую ячейку буферного запоминающего блока 1 и занесение

«единицы в следующий справа разряд кольцевого маркерного регистра 3 и т. д.

Одновременно и в зависимости от записи происходить считывание информации в том же порядке, что и ввод, т. е. k-e слово выводится вслед за (k-l)-M (фиг. 2). Это происходит благодаря тому, что после первой записи в кольцевом маркерном регистре 3 появляется комбинация расположенных слева нанраво одного «нуля и двух «единиц, которая дешифрируется как сигнал «разрешение чтения (например, на выходе iSs) из той ячейки буферного запоминающего блока 1, куда было записано первое слово. Чтение происходит по сигналу, поступающему на элемент задержки 5, и в том случае, если до этого триггер 4 был нереключен в состояние «1 сигналом по входу 11. При этом сигнал с выхода триггера 4 тактирует вынесение «О в тот

разряд кольцевого маркерного регистра 3, который соответствует опрашиваемой ячейке буферного запоминающего блока. Ввиду того, что положение границы «О - «1 переместилось вправо, будет подготовлена к считыванию следующая ячейка буферного запоминающего блока 1 (если до этого она была заполнена информацией).

Таким образом, устройство позволяет осуществлять независимую запись и чтение информации в норядке ее поступления, что обеспечивается дещифрацией положения границ (признак записи) и «О - «1 (признак чтения), движущихся слева направо но кольцевому маркерному регистру 3.

Для сигнализации о заполнении буферного запоминающего блока 1 и кольцевого маркерного регистра 3 применен логический элемент «ИЛИ - НЕ 8, на выходе которого в случае отсутствия сигнала записи на выходах 15i-

15m дешифратора 2 появляется сигнал блокировки ввода. По этому сигналу останавливается накопитель входной информации (например, лентопротяжное устройство). Сигнал «запись исчезает со всех выходов I5i-15т

дешифратора 2 тогда, когда в кольцевом маркерном регистре 3 останется один «нуль, а ввиду того, что для дешифратора сигнала «запись необходима последовательность: одна «единица и два «нуля, сигнал этот возникнет только после очередного сигнала по входу 11, когда освободится еще один разряд кольцевого маркерного регистра 3.

Следует отметить, что для нормальной работы устройства сопряжения необходимо, чтобы средняя скорость поступления слов была меньше средней скорости их считывания при асинхронной работе источника и приемника.

Предмет изобретения

Устройство сопряжения, содержащее буферный запоминающий блок, информационные вход и выход которого соединены соответственно с информационными входом и выходом устройства, кольцевой маркерный регистр,

первый и второй вентили, одни входы которых

соединены с управляющим входом устройства, формирователь « триггер, единичный вход которого соединен с первым синхронизирующим входом устройства, отличающееся тем, что, с целью повыщения быстродействия, оно содержит дещифратор, элемент «ИЛИ-НЕ, первый и второй элементы задержки, причем синхронизирующий вход буферного запоминающего блока соединен с выходом первого вентиля, другой вход которого соединен со вторым синхронизирующим входом устройства и через первый элемент задержки - с другим входом второго вентиля и со входом второго элемента задержки, выход которого соединен с нулевым входом триггера, нулевой выход триггера через формирователь, а выход второго вентиля - непосредственно соединены с соответствующими управляющими входами кольцевого маркерного регистра, который соединен двусторонними связями с дешифратором, выходы которого соединены со входами записи и чтения буферного запоминающего блока, входы записи буферного запоминающего блока соединены со входами элемента «ИЛИ-НЕ, выход которого соединен с выходом блокировки устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1977 |

|

SU746488A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для сопряжения | 1977 |

|

SU739516A1 |

| Устройство для сопряжения | 1983 |

|

SU1124276A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Ассоциативное запоминающее устройство | 1988 |

|

SU1562956A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Многоканальный измеритель временных характеристик последовательности дискретных сигналов | 1987 |

|

SU1442971A1 |

| Буферное запоминающее устройство | 1980 |

|

SU974411A1 |

Авторы

Даты

1975-10-15—Публикация

1973-08-20—Подача