(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1226473A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Запоминающее устройство с диагональной адресацией | 1986 |

|

SU1399819A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2020 |

|

RU2723288C1 |

1

Изобретение относится к области . вычислительной техники и может быть использовано для согласования скоростей обмена данными.

Известны устройства для сопряжения Щ , содержащие память на сдвиговых регистрах, коммутаторы, распределители, регистры, сумматор, схемы сравнения и узел управления и выполняющие функции согласования скоростей передачи данных.

Однако такие устройства сложны, кроме того, невозможно использовать в качестве запоминающих злементов стандартные интегральные модули-памяти,

Наиболее близким к изобретению по технической сущности является .устройство для сопряжения 2 , содержащее память, кольцевой маркерный регистр, соединенный выходами с соответствующими входами дешифратора, первая и вторая группа выходов которого подключены соответственно к первой и второй группам управляющих входов памяти, информационные вхсды и выходы которой являются соответствующими информационными входами и выходами устройства,и элемент И, соединенный входами с соответствующими

выходами первой группы дешифратора, а выходом - с первым управляющим выходом устройства.

Недостаток этого устройства сос5 тоит в низком быстродействии из-за того, что считывание очередного слова из памяти не может производится сразу по синхроимпульсу вывода , а только через некоторое время пос10 ле поступления очередного импульса синхронизации, который тактирует запись. При этом скорость чтения ин.формации не может быть выше частоты записи.

15 Кроме того, ограничение на тип запоминающих элементов, на которых может строится память, выражающееся в невозможности использовать стандартные дешёвые интегральные элемен20 ты памяти с произвольной выборкой, сужает область применения устройства.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем,

25 что в предложенное устройство введены два счетчика, ко мутаторы по числу адресных входов памяти и элемент ИЛИ, Выход каждого коммутатора подключен к соответствующему адресному входу

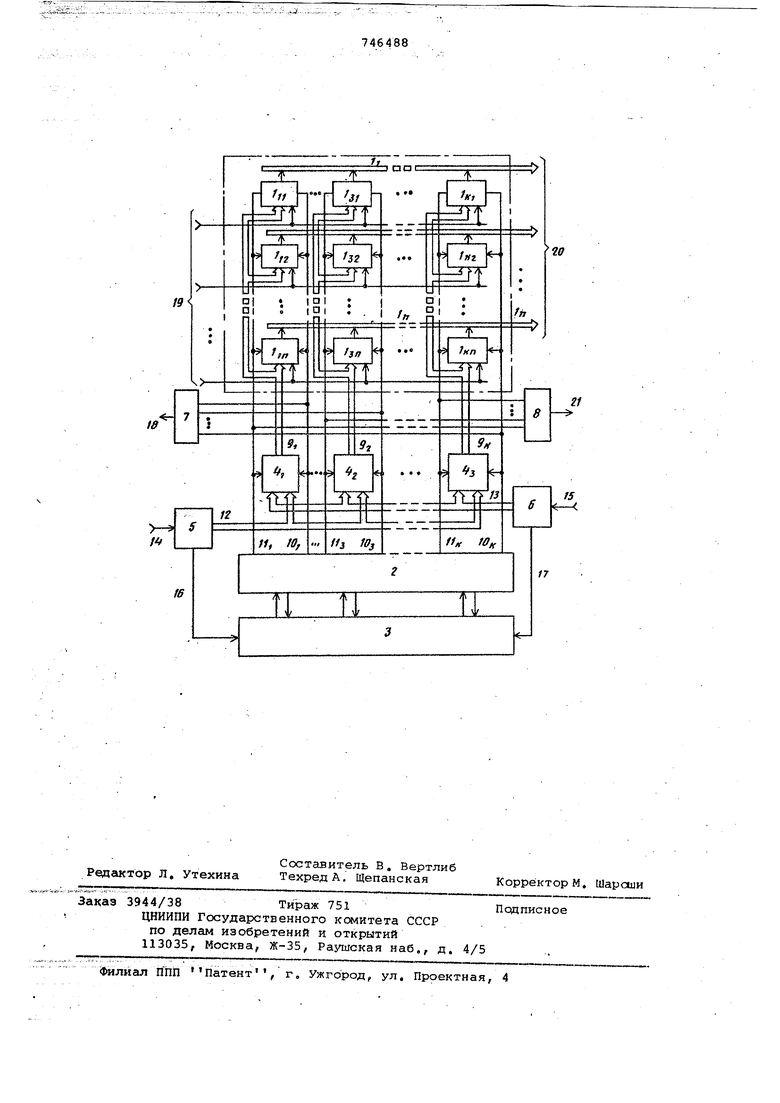

30 памяти, первые и вторые входы комму- таторов соед1Инены соответственно с выходами первого и второго счетчиков выходы переполнения которых подключе ны соответственно к первому и второму управляющим входам кольцевого мар керного регистра, а входы соответственно.к первому и второму управляю щим входам устройства. Выходы второй группы выходов дешифратора подключены к. соответствующим входам элемента ИЛИ, выход которого йвляется вторым управляющим выходом Ьтройства, Кром того, память содержит п элемейтов ИЛ и матрицу иэ п строк и К столбцов:э,з .поминающих М-раэрядных элементов, тф чем информационные выход и вход запо минающего элемента i-той строки (i, подключейм соответственно через элемент ИЛИ к i-му выходу и ду памяти, адресные, первый и второй входы запоминающего элемента J-ro столбца (,K) подключены соответственно к --ым адресному и управляющим входам из первой и вторЪЙ группы управляющих входов памяти. На чертеже представлена структурная схема устройства. Оно содержит память 1,дешифратор 2,кольцевой маркерный регистр 3,комму таторы 4/ первый счетчик 5, второй счетчик б, элемент И 7, и элементы ИЛИ 8, группу 9 адрусных шин памяти 1, первую группу 10 выходов дешифратора (подготовка зиписи), вторую группу 11 выходов дешифратора (подготовка чтения), груп пу 12 адресных шин счетчика 5, группу 13 адресных шин счетчика б, первый 14 управляющий вход устройства (стробирование записи), второй 15 управляющий вход устройства {стробирование чтения), выход 16 переполнения счётчика 5 (сдвиг по записи), выход 17 переполнения счетчика б (сдвиг по чтению), первый управляющий выход 18 устройства (блокирование источника), информационные входы 19 и выходы 20 устройства и второй управ ляющий вход 21 устройства. Память 1 содержит матрицу ддно типНИХ запоминающих модулей с произвольной выборкой (например Мх.1 бит со встроенными дешифраторами) In , . , и п элементов ИЛИ, обоз наченные 1, - In Дешифратор 2 содержит две группы логических трехвходовых элементов И и предназначен для дешифрации поло.жения двух границ между группой нуи группой единиц. находящих ся в регистре 3, а также для переключения коммутаторов и запоминающих модулей с режима запись на режим чтение , Управляющий вход кольцевого маркерного регистра 3 соединен с выходом 16 переполнения счетчика 5, служит для занесения единицы справа от границы 1 -О, а управляющий вход, соединенный с выходом 17 переполнения.счетчика б, - для занесения нуля справа от границы в регистре 3. Устройство работает следующим образом, В исходном сост оянии все разряды регистра 3 устанавливают в О, за исключением какого-либо одного. При этом комбинация подряд расположенных в регистре одной единицы и двух нулей дешифрируется соответствующим трехвходовым элементом И дешифратора 2 как сигнал подготовки записи (например, на выходе 10 ,-3 ) в ячейки запо1«1инающих модулей 1з :i.j третьего столбца памяти 1, Этот же сигнал подключает к адресн.ым входам этих модулей выходсчетчика 5. Первое слово, поступающее по информационному входу 19 и стробируемое синхроимпульсом записи по управляющему входу 14, заносится в .первую ячейку выбранных модулей, Переключаемый этим же Синхроноимпульсом в следующее состояние счетчик 5 подготавливает занесение второго входного слова во вторую ячейку и т.д. до заполнения все.х М ячеек запоминающих модулей третьего столбца, . . . В момент, когда модули окажутся заполненными, счетчик 5 переполнится и окажется в нулев ом состоянии, а сигнал его переполнения с выхода 16 поступит в регистр 3, вызовет занесение еще одной единицы в следующий справа разряд от единицы, находившейся тампервоначально, ТаКИМ образом, в регистре 3 будут находиться две подряд расположенные единицы. Комбинация вновь записанной .единицы и двух следующих за ней нулей дешифрируется другим трехвхЬдовым элементом И дешифратора 2 как сигнал подготовки записи по выходу 10 в модули четвертого столбца памяти 1. „ ... X Так как сигнал, подготавливающий запись, перешел с выхода 10 на выход 10 дешифратора 2, выход счетчика 5 подключается к адресным входам модулей четвертой строки через коммутатор 4 и вновь поступающие на информационный вход 19 слова будут последовательно записываться в ячейки этих модулей до очередного переполнения счетчика 5 и переключения сигнала на выходах первой группы 10 дешифратора 2, Запись информации в другие соседние модули происходит аналогично. Сразу после заполнения модулей третьего столбца подряд расположенные в регистре 3 один нуль и две единицы дешифриЕ)уются соответствующим трехвходовым элементом И дешифратора 2 на третьем выходе второй группы выходов 11J как сигнал подготонки чтения из этих модулей. Так как счетчик 6 адресов чтения находится в нулевом сост.оянии, первое слово будет считываться в приемник информации по первому адресу модулей третьего столбца, а каждый синхроимпульс чтения, поступающий из приемника по второму управляющему входу 15, подготавливает адрес очередной ячейки этих модулей до момента считывания всех слов переполнения счетчика 6,

Импульс переполнения счетчика б с выхода 17 поступает на вход регистра 3 и записывает нуль справа от группы нулей на место первоначально находившейся там единицы. Расположенные в этом регистре подряд нуль и две единицы дишифрируются-дешифратором 2 как сигнал подготовки чтения из ранее заполненных модулей четвертой строки аналогично описанному выше.

Для более надежной работы устройства при полном заполнении памяти элемент И 7 вырабатывает сигнал, выдаваемый на первый управляющий вьзхсд 15. и служащий для блокировки ввода информации со стороны источника.

Для исключения потерь информации чтение памяти 1 осуществляется только при наличии на втором управляющем выходе 21 сигнала, который вырабатывается элементом ИЛИ 8,

Таким образом, устройство позволяет осуществить независимые запись и чтение информации из памяти, что повышает его быстродействие.

Кроме того, объем памяти устройства может быть достаточно просто изменяться без изменения его структуры путем исключения или добавления запоминающих модулей вместе с соответствующим .коммутатором, частью дешифратора и частью кольцевого маркерного регистра.

Формула изобретения

5 адресному входу памяти,, первые и вторые входы коммутаторов соединены соответственно с выходами первого и второго счетчиков, выходы переполнения которых подключены соответствен0 но к первсму и второму управляющим входам кольцевого маркерного регистра, а входы - соответственно к первому и второму управляющим входам устройства, выходы второй группы выхо5 дов дешифратора подключены к соответствующим входам элемента ИЛИ, выход которого является вторым управляющим выходом устройства,

2, Устройство по п,1, отли 0 ч аю ще еся тем, что память содержит п элементов ИЛИ и матрицу из п строк и К столбцов запоминающих М-разрядных элементов, причем информационные выход и вход за помин ающего

5 элемента i-истроки (,n) подключены соответственно через i-й элемент ИЛИ к х-му выходу и 1-му входу памяти, адресные, первый и второй входы запоминающего элемента j-ro столбца

Q (,K) подключены соответственно к j-Ым адресному и управляющим входам из первой и второй групп управляющих входов памяти.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР по заявке 2166167/18-24, кл, G 06 F 3/04, 1975,

2,Авторское свидетельство СССР

№ 488202, кл, G 06 F 3/04, 1973 (прототип) ,

Авторы

Даты

1980-07-05—Публикация

1977-12-27—Подача