(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига | 1978 |

|

SU752488A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Регистр сдвига для буферного запоминающего устройства | 1985 |

|

SU1432609A1 |

| Устройство сопряжения | 1973 |

|

SU488202A1 |

| Буферное запоминающее устройство | 1980 |

|

SU858109A1 |

| Управляющий регистр для буферного запоминающего устройства | 1987 |

|

SU1499405A1 |

1

Изобретение относится к вычислительной технике и найти применение при построении быстродействующих буферных запоминающих устройств.

Известно запоминающее устройство, которое характеризуется низким быстродействием, обусловленным медленным продвижением информации на нужную позицию. Кроме того, это устройство имеет небольшую плотность записи информации, так как в каждом цикле может записываться только одно слово 11 .

Наиболее близким к предлагаемому по технической сущности является запоминающее устройство, содержащее одноступенчатые сдвиговые, регистры, связанш 1е с входным регистром, двухступенчатый регистр, группу схем управления сдвигами, счетчик и дешифратор, Устройство допускает запись очередного слова при продвижении на нужную позицию пре- дьщущего Г2 ..

Недостатком известного устройства является сложность схем управления продвижением информации (двухступенчатый регистр, счетчик, дешифратор, rpysina схем управления сдвигами).

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, .входы которого соединены с информациолными входами устройства, выходь накопителя подклк 10чены к первому и второму входам блоков регистров сдвига, выходы которого соединены с выходами устройства, шины записи и считывания, введены к последовательно соединенных элементов И и

15 элементов задержки (где k - число разрядов регистра сдвига и k -1,2...,1 , .,., N) и триггеров, причем первый вход i -го триггера, кроме последнего соединен с первым входом i -го элемен-:

20 та И, второй выход i -го триггера, кроме первого, соединен с вторым входом (i-l)-ro элемента И, первый вход -го триггера, кроме первого, подключен к

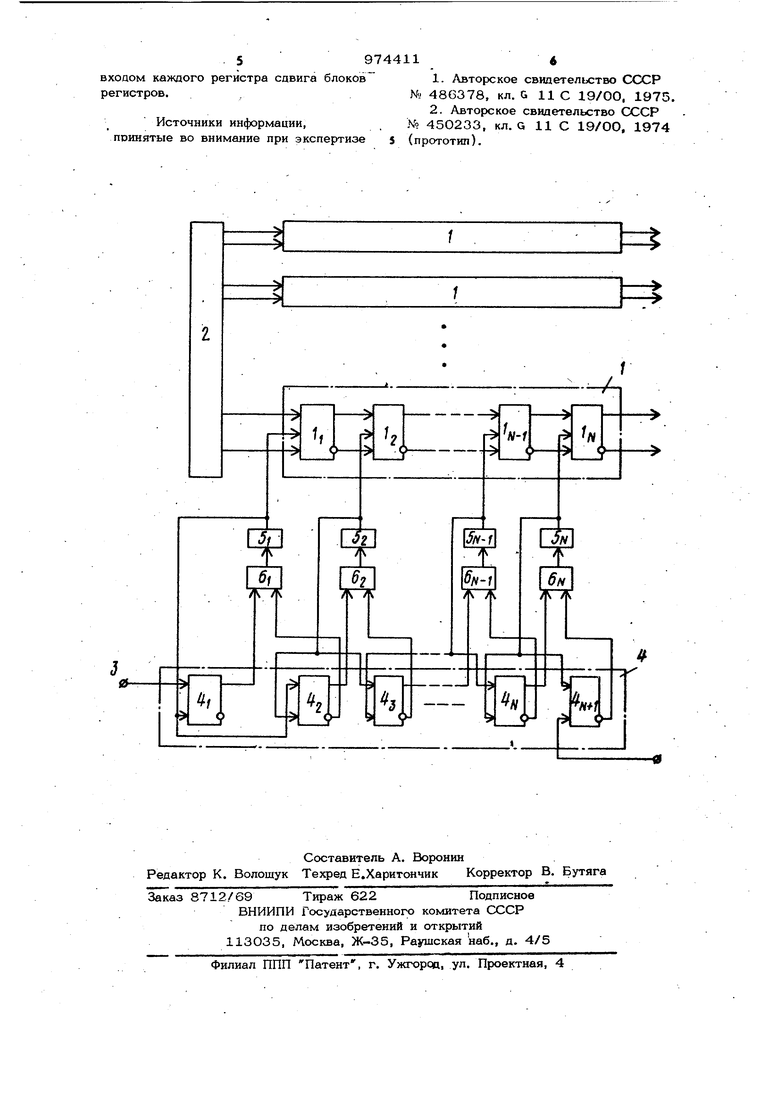

выходу ( -1 )-го элемента задержки, второй вход i -го триггера, кроме последнего, соединен с выходом п -го элембнта задержки и с первым входом (i +1)-го триггера, первый вход первоготриггера подключен к шине записи, второй вход последнего триггера соединен с шиной считывания, выход каждого элемента задержки соединен с третьим входом каждого регистра сдвига, блоков ре- to ными гистров. На чертеже представлена функциональ Мая схема предложенного устройства. Устройство содержит регистр 1 сдви накопитель 2, шину 3 записи, триггеры 4, последовательно соединенные элементы 5 задержки и элементы И 6 и шину 7 считывания. Предложенное устройство работает следующим образом. При записи информации по шине 3 поступает импульс Запись, который устанавливает первый триггер 4 в 1 Открывается первый элемент И 6 и на выходе первого элемента 5 задержки и следовательно, на выходе первого элемента И 6 появляется единичный разрешающий сигнал, по которому слово 3 накопителя 2 записывается в регистр 1 сдвига, а маркерная 1 из первого триггера.4 переписывается во второй триггер 4,j, первый триггер 4 при этом сбрасывается, в О, Далее разрешаюшлй сигнал появляется на выходе второго элемента И бд и слово перепис вается из первого регистра 1 сдвига во второй, а маркерная 1 поступает во второй триггер 4 и т.д. Продвижени маркерной 1 вправо по триггерам 4, а следовательно и информации по регист рам I, продолжается до тех пор, пока вновь поступившая Информация (маркерная 1) не расположится вплотную к ранее записанной информации, что обеспечивается элементами И 6 и элементам 5 задержки. Во время продвижения слова на нужную позицию в регистры. 1 может заноситься новое сл.ово накопителя 2 (а в триггеры 4 -.очередная маркерная 1) Пауза между последовательной записью двух слов должна быть не менее двух тактов сдвига, при этом ме.жду двумя сдвигаемыми словами будет пробел в од ну линейку. Чтение информации происходит по сигналу Выборка, поступающему по шине 7, Этот сигнал устанавливает последний М-ый триггер О. Элементы 5 и 6 обеспечивают сдвиг маркерной I из (N-l)-ro разряда регистра 1 в N-ый разряд, а из (N 2)-го разряда в (N -1)-ый и т.д. Соответственно происходит продвижение всей записанной в регистрах 1 информации на одну линейку вправо. На выходе устройства готово для выборки следующее слово. Период между двумя последовательсигналами Выборка должен быть. как и для сигнала Запись, не менее двух тактов сдвига. Таким образом, предложенное устройство позволяет осуществлять быструю запись и чтение информации, совмещая при этом запись (чтение) очередного слова с продвижением предыдущих. По сравнению с известным в предложенном устройстве исключены дешифратор, счетчик, д.вухйтупенчагый регистр, и группа схем управления сдвигами, а вместо них введены группа элементов И и элементов задержки и триггеры. Таким образом достигается упрощение устройства. . Фор. мула изобретения Буферное запоминающее устройство, содержащее накопитель, входы которого соединены с информационными входами, устройства, выходы накопителя подклк чены к первому и второму входам блоков регистров сдвига, выходы которого соединены с выходами устройства, шины записи и считывания, отл ичающее с я тем, что, с целью упрощения устройства, оно содержит I последовательно соединенных элементов И и элементов задержки (где. 1. - целое число разрядов регистра сдвига и k 1,2..., i , ... N) и k +1 триггеров, причем первый вход 1 -го триггера, кроме последнего, соединен с первым входом i -го элемента И,второй выход i -го триггера, кроме первого, соединен с вторым входом ( i -1 )-го элемента И, первый вход i-го триггера, кроме первого, подключен к выходу ( i -1)-го элемента задержки, второй вход i -го триггера, кроме последнего, соединен с выходом i -го элемента задержки и с первым входом (i +1 )-го триггера, первый вход первого триггера подключен к шине записи, второй вход последнего триггера соединен с шиной считьгаания, выход каждого э мента задержки соединен с третьим

. 5974411«

входом каждого регистра сдвига блоков 1. Авторское свидетельство

регистров.№ 486378, кл. G 11 С 19/00, 1975.

Источники информации,. № 450233, кл. G Ц С 19/ОО, 1974

принятые во внимание при экспертизе s (прототип).

Авторы

Даты

1982-11-15—Публикация

1980-02-27—Подача