(54) СУММАТОР.-ВЫЧИТАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для сложения и вычитания чисел с плавающей точкой | 1987 |

|

SU1481743A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для сложения и вычитания | 1988 |

|

SU1571575A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

1

Изобретение относится к цифровой вычислительной технике и может быть ис- нользовано в вычислительных машинах и устройствах., работающих в системе очисления остаточны.х классов.5

Известен сумматор-вычитатель, оне- рируюший с числами, представленными минимальными но абсолютной величине статками, содержащий блок элементов и двоичный сумматор, вход кото- ю oio соединен с входом устройства.

Однако большое количество каскадов переработки информации и, как следствие этого, относительно низкое быстродействие, а также различное время выполне-15 ПИЯ операций сложения и вычитания за- рудняет синхронизацию устройства.

Цель изобретения - увеличение быстро- /действия и выполнения операций сложеия и вычитания за одинаковое время и20 с;овместпое получение суммы и разности двух операндов по модулю F.

Достигается это блаходаря тому, что устройство содержит сумматор знаков оиергшдов, двоичный вычислитель, блок25

формирования абсолютной величины первого; результата, блок определения знака первого результата, блок формирования абсолютной величины второго результата, блок определения знака BTOpoix) результата, причем выходы двоичного сумматора соединены с блока формирования абсолютной величины nepBoiO результата и блока определения знака первого результата, другой Е«ОД которого соединен с входом устройства, выходы двоичного вычитателя соединены с входами блока формирования абсолютной величины второго результата и блока О1фи- деления знака второго результата, другой вход которого соединен с входом устройсчва, выходы сумматора знаков операндов, блока формирования абсолютной величины первого результата, блока определения знака первого результата, блока форкшрования абсолютной величины второго резул. и блока определения знака второго результата соединена с входами блока эл ;ментов И, выходы которого соединены с вы ходами устройства.

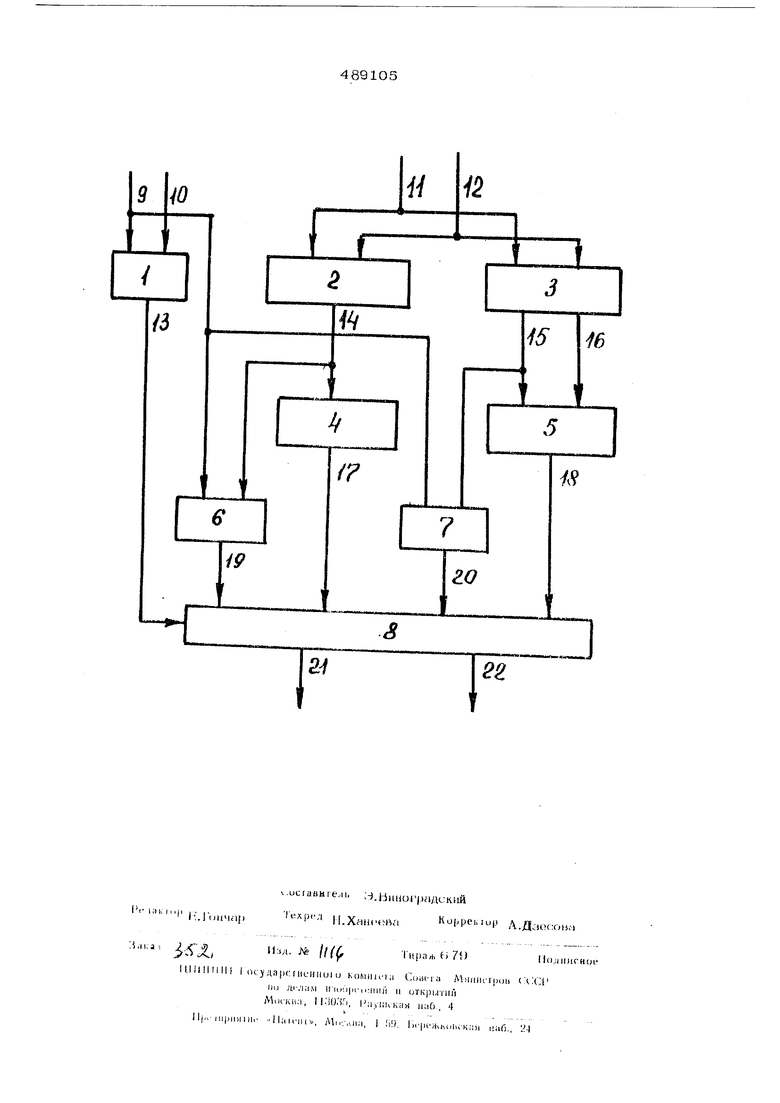

Сумматор-вычитатель использует симметричность матриц операций модульного сложения и вычитания, что позволяет аппаратурно реализовать только часть одной из этих; матриц (например, половину матри цы модульного сложения) и парг1ллельно, анализируя знаки операндов, получать все остальные значения матриц операций модульного сложения и вычитания. На чертеже приведена блок-с.хема сумKiaTopa-вычитателя (модульного). Сумматор-вычитатель состоит из сумм тора 1 знаков операндов, двоичного сумматора 2, двоичного вычитателя 3, блока 4формирования абсолютной величины перв го результата, блока 6 определения знака .второго результата и блока 8 элементов И-ИЛИ Кодовая шина 9 соединена с входами сумматора 1 и блоков 5 и 7. Кодовая шина 10 соединена с сумматором L Кодовые шины 11 и 12 соединены с входами сумматора 2 и вычитателя 3. Выкоды 13 сум матора 1 соединены о входами блока 8. В Выходы 14 сумматора 2 соединены с входами блоков 4 и 6. Выходы 16 вычитать ля 3 соединены с входами блока 5. Выхи- ды 15 вычитателя 3 соединены с входами блоков 5 и 7. Выходы 17 блока 4 соединены с входами блока 8. Выходы 18 блок 5соединены с входами блока 8. Выходы 19 блока 7 соединены с входами блока 8, соединенного с выходами блока 20. Блок 8 имеет выходы 21 и 22. Двоичный сумматоо 2 и двоичный .вычитатель 3 являются ( fl 1)-разрядными (2 Р72 ). Блок 8 элементов И-или состоит из 2 fl элементов тина 2И-2И- ИЛИ. Сумматор-вычитатель работает следующим образом. На сумматор 1 знаков операндов соответственно по кодовым шинам 9 и 10 посту11лв.;т знаки операндов А и В, которые складывается по модулю 2. С выхода 13 сумматора 1 эта сумм поступает на вход блока 8 элементов И-ИЛИ. Абсолютные величины операндов А и В соответственно по кодовым шинам 11 и 12 поступают на двоичный сумматор 2 и двоичный вычитатель 3. С выхода 14 сумматор 2 ()разрядная сумма и сигнал в М-ьш разряд HOCTjTiaeT на блок 4. Абсолютная величина первого результата на выходе блока 4 совпадает с суммой па выходе двоичного сумматора 2, если эта сумма не более, чем Bejni4Hna - , и равна дополнению cyMMt:,j до 1 если она больше величины - . г 2 Ьлок 6 определяет знак первого резул тата, который соьчшдает со знаком опергш да А, если сумма на выходах 14 двоичного сумматора 2 не больше, чем величина -, и противоположен знаку операнда А если эта сумма больше величины . Двоичный вычислитель 3 вычитает от абсолютной величины операнда А абсолютную величину операнда В. С выходом 16 вычитателя 3 ( ti-l)-разрядная разность поступает на блок 5. С выходов 15 вычитателя 3 сигнал заема из П -го разряда поступает на входы блоков 5 и 7, i Абсолютная величина второго результата на выходе блока 5 совпадает с разное тью на выходах 16 вычитателя 3, если нет заема из п-го разряда, и равна дополнению разности на вьгходе 16 вычитателя 3, если есть заем. Блок 7 определяет знак второго результата, который совпадает со знаком операнда А, если нет заема H3fi-го разряда вычитателя 3, и противополояен знаку операнда А, если есть заем. Абсолютные величины первого и второго результатов, знаки первого и второго результатов соответственно с выходов 17-20 блоков 4-7 поступают на входь блока 8. В зависимости от результата, поступающего с выхода 13 сумматора 1 знаков операндов блок 8 элементов и-ИЛИ коммутирует свои входы 17-20 в соответствии со следующим правилом: - если сумма по модулю двух знаков опер 1ндов равна нулю, то абсолютная величина модульной суммы и знак ее nocTyrf пают на выходы 21 блока 8 соотвотственн1 с выходов 17 и 19 блоков 4 и 6., а абсолютная величина модульной разности и ее знак поступают на выходы 22 блока 8 элементов И-ИЛИ соответственно с выходов 18 и 2О блоков 5 и 7., - если сумма по модулю двух знаков . операндов равна единице, то абсолютная величина модульной суммы и ее знак постунают на выхл)ды 21 блока 8 соответственно с выходов 18 и 2О блоков 5 и 7, а абсолютная величина модульной разности и ее знак поступают на выходы 22 блока 8 с выходов 17 и 19 блоков 4 и 6. С, выходов 21 блока 8 элекинтов И-ИЛМ снимается сумма по модулю F, а с libixoyion 22 снимается разность по модулю Р. 11 р в л м е I р е т е н и я С/умм(1Тор-в111Чита1ель, оперирунлций i числами, цредставле)пил(.л1 по абсолютнсй величине истачками, с-одор ьанаи блок элемннтои И и двоичный (-умматор, вход ксткpuro соединен (- входом устройства, о т л н ч а ю Q1 и ) i; я тем, что, с повышения оысч-родействня, он содержит сумматор знаков операнлов, двоичный .выч.. татель, блок формирования абсолютной ве- личины нервого результата, блок определения знака первого результата, блок формирования абсолютной величины второго результата, блок определения знака второго результата, причем выходы двоичното сумматора соедн -: }1ен1.1 с входами блока формирования абсолютной величины нервохо результата, и блок определения знака первого результата, другой вход которого соедин€ н с входом

устройства, Бь,1.ходы двоичного вычитателя соединены с входами блока формирования абсолютной величины второго результата ,и блока определения знака второго результата, другой .вход которого соединен с Fixt дом устройства, выходы сумматора знака операндов, блока формирования абсолютной величины первого резул{ тлта, блока определения знака первого результата, блок фо). мирования абсолютной величины второго результата и 0пока определения знака пто рого результата соединены с входами блока элементов ,И-ИЛИ, выходы которого соединены с выходами устройства.

2-/

2г

Авторы

Даты

1975-10-25—Публикация

1974-02-01—Подача