при наличии сигнала на выходе переполнения блока 3 формирования кода нормализации через коммутатор 14 передается значение суммы с сумматора 11 константы, в противном случае - одно из значений с выхода соответствующих разрядов порядка блока 1 выравнивания и разности с выходов вычитателей 3 константы группы в зависимости от унитарного кода нормализации на выходе блока 3 формирошего разряда знака сумматора-вычитателя соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом знака результата , устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит группу вычитателей константы и вычитатель константы, два сумматора константы, два коммутатора, элемент И и второй мультиплексор, причем выход резуль- вания кода нормализации. Значения заема 0 тата сумматора-вычитателя соединен с ин- с соответствующих выходов вычитателей 9формационным входом блока формирования

кода нормализации, первый и второй управляющие входы которого соединены соответственно с выходами старшего и младшего разрядов знаков сумматора-вычита- эс теля, выход старшего разряда знака которого соединен с вторым входом блока элементом ИСКЛЮЧАЮЩЕЕ ИЛИ, выход младших разрядов порядка блока выравнивания соединен с в ходам, и вычитателей константы группы и с входом первого сумконстанты группы поступают на информационные входы коммутатора 15, на выход которого выбирается, по значению унитарного кода нормализации, реальное значение заема. На выходе элемента И 13 формируется значение переноса в старшие разряды порядка в случае переполнения при сложении мантисс операндов. Указанные значения поступают на управляющие входы мультиплексора 16, через который

реальное значение старших разрядов поряд- 40 матора константы, выход младших разряка результата устройства.

поступает на выход 26

дов порядка блока выравнивания, выходы разности вычитателей константы группы ft выход суммы первого сумматора константы соединены соответственно с информационными входами первого коммутатора, выходы заема вычитателей константы группы соединены соответственно с информационными входами второго коммутатора, выход которого и выход элемента И соединены соответственно с управляющими входами - второго мультиплексора, выход которого и выход первого коммутатора являются выходом порядка результата устройства, выход старших разрядов порядка блока выравнивания соединен с входами вычигателей константы и второго сумматора константы,

Формула изобретения

Устройство для сложения и вычитания чисел с плавающей точкой, содержащее блок выравнивания, сумматор-вычитатель, блок формирования кода нормализации, блок элементов. ИСКЛЮЧАЮЩЕЕ ИЛИ, первый мультиплексор, сдвигатель и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход знака первого операнда устройства соединен с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход знака второго операнда устройства и

45

дов порядка блока выравнивания, выходы разности вычитателей константы группы ft выход суммы первого сумматора константы соединены соответственно с информационными входами первого коммутатора, выходы заема вычитателей константы группы соединены соответственно с информационными входами второго коммутатора, выход которого и выход элемента И соединены соответственно с управляющими входами - второго мультиплексора, выход которого и выход первого коммутатора являются выходом порядка результата устройства, выход старших разрядов порядка блока выравнивания соединен с входами вычигателей константы и второго сумматора константы,

вход вида операции устройства соединены 55 выходы которых и выход старших разрядов

порядка блока выравнивания соединены соответственное информационными входами второго мультиплексора, выход переноса персоответственно с вторым и третьим входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляю5

дов порядка блока выравнивания, выходы разности вычитателей константы группы ft выход суммы первого сумматора константы соединены соответственно с информационными входами первого коммутатора, выходы заема вычитателей константы группы соединены соответственно с информационными входами второго коммутатора, выход которого и выход элемента И соединены соответственно с управляющими входами - второго мультиплексора, выход которого и выход первого коммутатора являются выходом порядка результата устройства, выход старших разрядов порядка блока выравнивания соединен с входами вычигателей константы и второго сумматора константы,

порядка блока выравнивания соединены соответственное информационными входами второго мультиплексора, выход переноса первого сумматора константы соединен с пер вым входом элемента И, второй вход которого соединен с управляющим входом первого мультиплексора и с выходом пере-, полнения блока формирования кода нормализации, выходы разрядов кода нормализации блока формирования кода нормализации соединены с входами соответствующих разрядов величины сдвига сдвигателя, выходы разрядов, кроме старшего, кода нормализации блока формирования кода нормализации соединены соответственно с управляющими входами второго коммутатора, выходы разрядов кода нормализации и выход переполнения блока формирования кода нормализации соединены соответственно с управляющими входами первого коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

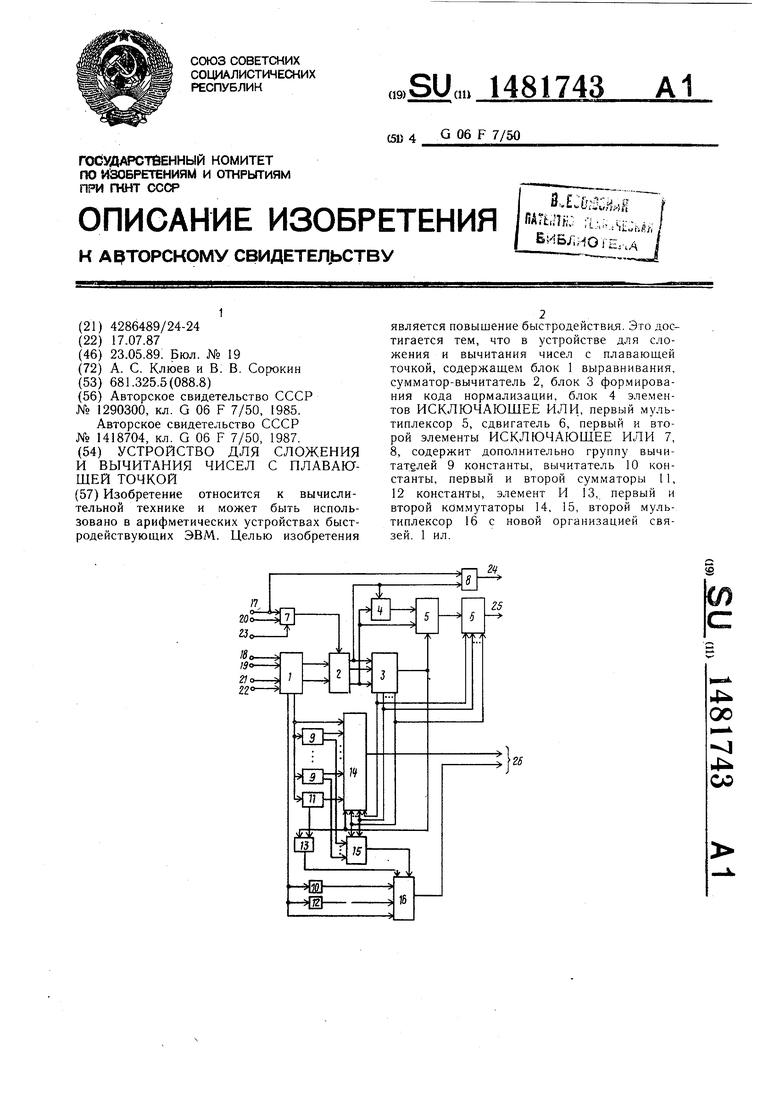

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах быстродействующих ЭВМ. Целью изобретения является повышение быстродействия. Это достигается тем, что в устройстве для сложения и вычитания чисел с плавающей точкой, содержащем блок 1 выравнивания, сумматор-вычитатель 2, блок 3 формирования кода нормализации, блок 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый мультиплексор 5, сдвигатель 6, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7, 8, содержит дополнительно группу вычитателей 9 константы, вычитатель 10 константы, первый и второй сумматоры 11, 12 константы, элемент И 13, первый и второй коммутаторы 14, 15, второй мультиплексор 16 с новой организацией связей. 1 ил.

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-07-17—Подача