(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор | 1974 |

|

SU512471A1 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Микропрограммный процессор | 1980 |

|

SU896629A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

1

Предлагаемое изобретение относится к вычислительной технике, в частности к процессорам с контролем.

Известен MHKponporpavMHWfi процессор-, содержащий операционный-блок, блок памяти, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, триггер фиксации сбоя и элементы И, ИЛИ 1.

В известном процессоре контроль функционирования адресного регистра и . схем управления выборкой п,амяти микрокоманд осуществляется с низкой достоверностью, которая обусловлена невозможностью полного контроля микропрограмм, содержащих переменные части выполняемых команд. В таких микропрограммах контролируется только количество микрокоманд в последовательности, постоянной для данной команды.

Наиболее близким к изобретению по технической сущности является микропрограммный процессор, содержащий операционный блок, первый вход которого соединен с первым входом первого элемента И и является входом процессора,второй вход - с первым выходом регистра микрокоманд

третий вход операционного блока соединен с единичным выходом триггера фиксации сбоя, первый выход операционного блока соединен с вторым входом первого элемента И и первым входом элемента ИЛИ, второй выход - с вторым входом элемента ИЛИ и первым информационным входом регистра адреса микрокоманд, а третий выход 0с счетным входом счетчика микрокоманд и управляю1цим входом блока памяти, инЛормационный вход которого подключен к выходу регистра адреса микрокоманд, а выход - к входу регистра микрокоманд, второй выход которого соединен с первым входом второго . элемента И, второй вход которого через элемент НЕ соединен с выходом элемента ИЛИ и установочным входом

С счетчика микрокоманд, а выход - с управляющим входом регистра адреса микрокоманд, второй информационный вход которого подключен к выходу первого элемента И 2.

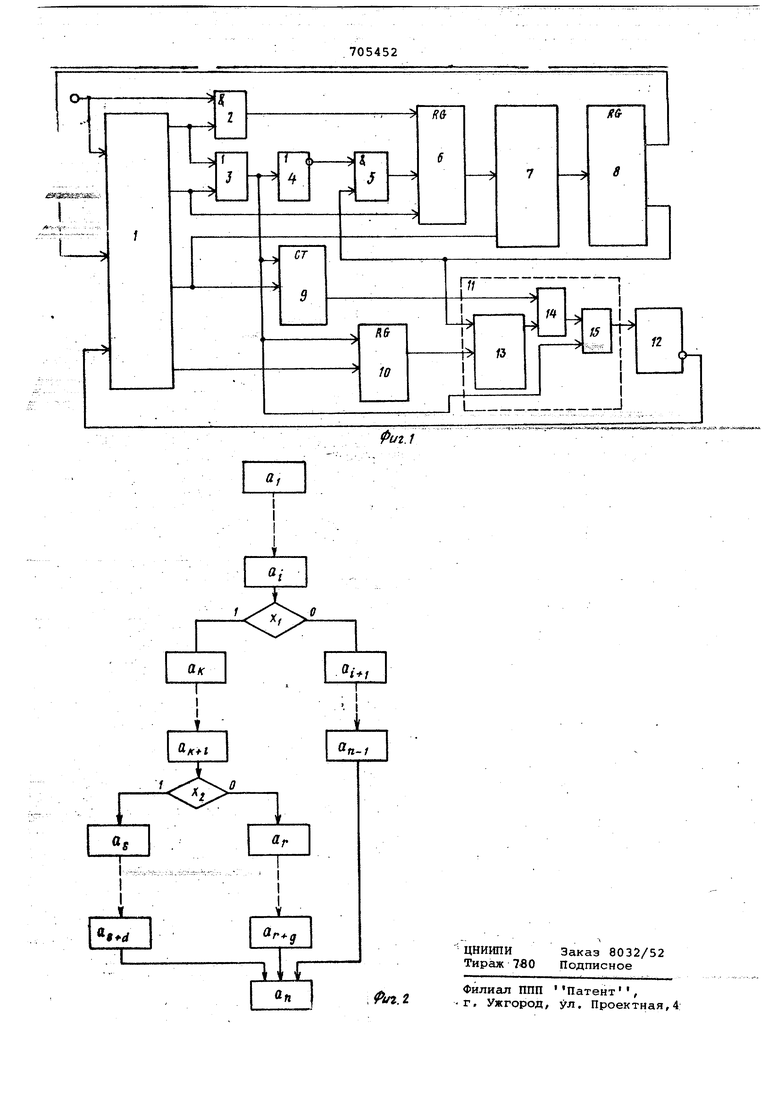

5

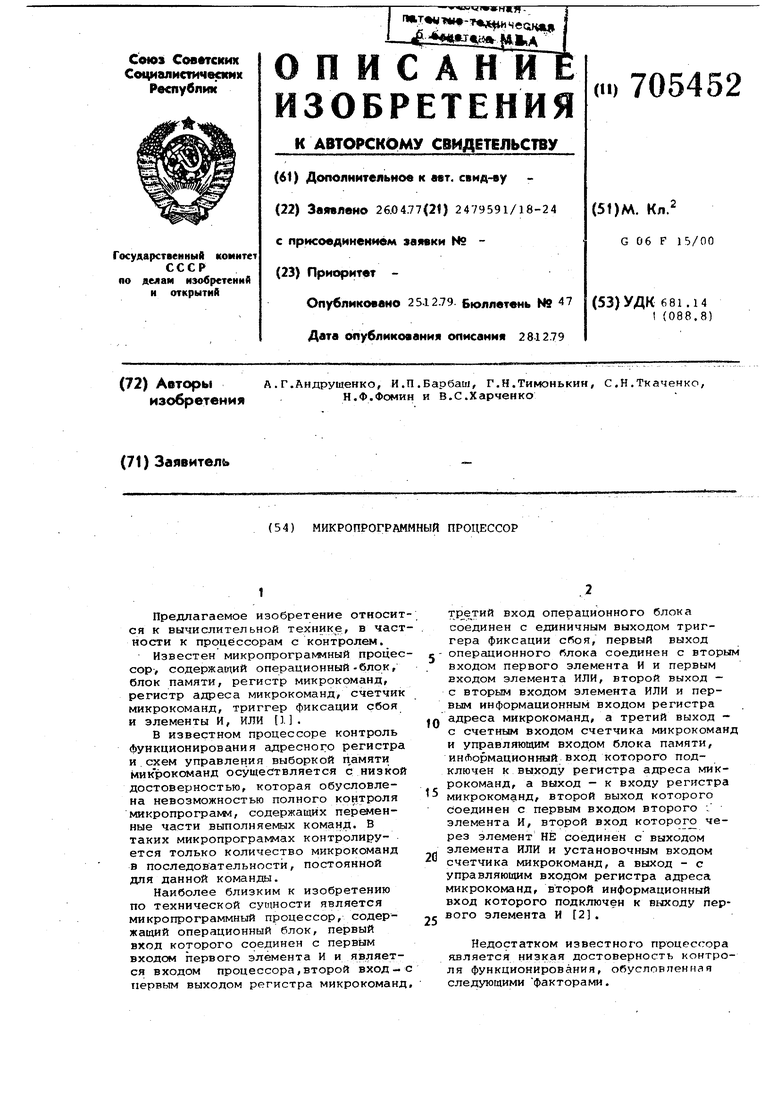

Недостатком известного процессора является низкая достоверность контроля функционирования, обусловпенная следующими факторами. В работе известного процессора осуществляется контроль работы адресного егнстра и схем управления выборкой памяти микрокоманд, так ,как сбои-в этой аппаратуре приводят R wapiJTiietmjo последовательности микро программ, которые не обнаруживаются схемами контроля считывания инЛормации из памяти микрокоманд. Суфнбстъ контроля сводится к подсчету числа реализованных микрокоманд и сравнению его с заданным. ОДнаГкО для микропрограмм, содержа tHjix участки микрокоманд, выполнение которых зависит от дополнительных логических условий выполнения команды, осуществляется контроль чиШй ййкрбкоманд только к неизменной части микропрограммы. При этом независимо от количёства выполняемых микрокоманд в переменной части выполннемой команды содержимое счетчика микрокоманд должно быть равно содержимому адресного поля последней микрокоманды. Количество микрокоманд в переменИбй Части микропрограммы, зависящее от порядка выполнения (проверки) и значений логических условий, в Из вёстном процессоре не контролируется. ЭтЬ связано с отсутствием в извес ном процессоре устройства, ФикСйрую щегб порядок проверки и значения лог ческих условий,что делает невозможны идентификацию последовательности мик Тро команд,которая реализуется при про Bepke тех или иных логических услови Целью изобретения является повьвд ййё достоверности информации. Указанная цель достигается тем, что в микропрограммный процессор до .йЬлнйтёльно введены регистр логичес условий, информационный вход.которо подключен к четвертому выходуопера ционного блока, а управляющий вход к выходу элемента ИЛИ, и блок авали за , , второй, третий и четвер тый входы которого, соединены с вторам выходом регистра микрокоманд, й1йХОд6м счетчика микрокоманд, ва хбдбм регистра логических условий и выходом элемента ИЛИ .сбо Вётствен S ёыХрд - с установочным входом, три гера фиксации сбоя, а также тем, чт блок анализа содержит узел фррмиро - ййия кбнтрольных признаков, первый и второй входы которого .подключены к первому и третьему входам блока соответственно, узел сравнения, пер .1 выЙ)зх6д которого соединен с вторым входом блока, а второй вход - с выхо дом узла формирования контрольных fipWsHakoB и элемент и, первый и вто входа которого подключены к выходу у зла сравнения и четвертому входу блока соответственно, а выход - к выходу блока. На фиг. приведена функциональная хема устройства; на Лиг .2 - алгоритм икропрограмглы. Процессор содержит операционный блок 1, первый элемент И 2, элемент ИЛИ 3, элемент НЕ 4, второй элемент 5, регистр 6 адреса микрокоманд, блок 7 памяти, регистр 8 микрокоманд, счетчик 9 микрокоманд, регистр.10 огических условий, блок 11 анализа, триггер 12 фиксации сбоя, узел 13 формирования контрольных признаков, узел 14 сравнения, элемент И 15. На рис.2 символами О (.,... ilkv-V--C; ,.,...r-tg;-i4i,...) обозначены микрокоманды, а через x Cd-i; г ) - логические условия. Неизменная Часть Мйкроп)ограммы представляет собой последовательностЬ микрокоманд О...а|, Далее реализуемая последовательность микрокоманд зависит от логических условий. В зависимости от логических условий -(5 в микропрограмме могУт реализоваться следующие три последовательности микрокоманд: а)первая последовательность соответствует порядку поступления и наборам логических условий равна a,.--Q,--ay и содержит -l1 микрокоманд; б)вторая последовательность соответствует порядку поступления и значениям логических условий равна av- -iQv-«v+e-«4-;VaS и содержит + t-t-d- - микрокоманд; в)третья последовательность соответствует порядку поступления и значениям логических условий XiX. paBHa a...,...ai.e-Sv -ap a y . и содержит/А -1 е, микрокоманд. Работает процессор следующим образом. Выборкой микрокоманд управляет операционный блок 1 путем передачи сигналов по третьему выходу в блок 7 памяти. Операционный блок 1 осуществляет ари(1метические и логические преобразования информации и контролирует правильность их выполнения. Кроме того, операционный блок 1 контролирует по четности правильность считывания информации из блока 7 памяти в регистр 8 микрокоманд. Порядок поступления и значения логических условий фиксируются . регистром .10 логических условий, ко- . торый тем самым осуществляет идентификацию конкретной последовательности микрокоманд в микропрограмме и формирование соответствующего признака. Блок 11 анализа выполняет следующие функции; а) формирует контрольный признак (код) заданного числа микрокоманд в последовательности, однозначно

соответствующий признаку порядка поступления и значений логических условий, формируемому регистром 10 логических условий, и. признаку данной микропрограммы, формируемому в адресном поле регистра 8 микрокоманд в конце циклов выборки и исполнения команд;

б)сравнивает признак (код) числа реализованных микрокоманд

в микропрограмме, который п оступает на второй вход-блока 11 анализа с выхода счетчика 9 микрокоманд, с контрольным признаком;

в)в случае несовпадения признака реализованных микрокоманд с контрольным подает сигнал сбоя на установочный вход триггера 12 фиксация сбоя.

Выполнение команды в предлагаемо устройстве разделено на два цикла: цикл выборки команды из оперативной памяти и преобразований адреса и цикл исполнения команды в соответствии с кодом операции.

В конце цикла выборки команды и адресных преобразований опергщионный блок 1 возбуждает сигнал по первому выходу. При этом кодоперации команды через первый элемент И 2 передается в регистр б адреса микрокоманд. После этого начинает выполняться микропрограмма цикла исполнения команды.

В конце исполнения команды операционный блок 1 возбуждает сигиал на втором выходе, который устанавливает в исходное состояние регистр 6 адреса микрокоманд и осуществляет переход к .выполнению микропрогра 1ы цикла выборки следующей команды.

В ходе выполнения микропрограмм сигнсшы на первом и втором выходах операционного блока 1 отсутствуют. При этом на выходе элемента ИЛИ 3 сигнал отсутствует, а на выходе элемента НЕ 4 присутствует единичны сигнал, который открывает второй элмент И 5, через первый вход которог с второго выхода регистра 8 адрес следующей микрокоманды передается в регистр б адреса микрокоманд.

При наличии сигнала на первом или втором выходе блока 1 и нулевом выходном сигнале элемента НЕ втор элемент И 5 закрывается..

Для обнаружения сбоев, которые приводят к нарушениям последователь ности микрокоманд и не обнаруживаются схемами контроля считывания информации из блока 7 памяти, необходим контроль работы этой аппаратры.

Работает микропрограммный процессор при контроле регистра 6 адреса микрокоманд и схе№ управления выборкой памяти микрокоманд след1тощим образом.

Каждая микропрограмма исполнения команд, цикл выборки команды и адресных преобразований имеет число микрокоманд, определяемое для данной микропрограммы порядком поступления (проверки) и значениями логических условий. Аппаратура процессора подсчитывает число микрокоманд, выполняемых в цикле выборки и в цикле исполнения команды и сравнивает его с заданным. При несовпадении фиксируешься сбой.

Микропрограммы могут содержать постоянное число микрокоманд и переменное. Количество микрокоманд в микропрограммах с переменными частями зависит от порядка поступления (про5верки) и значений логических условий.

KoHTpoJfb микропрограмм с постоянным числом микрокоманд.

При выполнении микрокоманд, форми0рующих сигналы на первом и втором выходах операционного блока 1, второй элемент И 5 закрыт и адресное поле регистра 8 свободно. В эти моменты времени адрес следующей микроко5манды определяется не содержимым адресного поля регистра 8 микрокоманд, а содержимым регистра кода операций операционного блока 1. В эти моменты вр емени адресное поле

0 регистра В используется для контроля правильности последовательности микрокоманд.

В микрокомандах, записанных в конце циклов, выборки и циклов испол5нения команд, записывается признак (код) данной микропрограммы Tj (где j - номер микpdпpoгpa wы ).

При считывании каждой микрокоманды сигнал с третьего выхода операционного блока 1 поступает на счет0ный вход сетчика 9 микрокоманд, который на своих выходах формирует признак (код) числа реализовакяых микрокоманд ot.

Регистр 10 логических условий

5 в рассматриваемом случае находится в исходном состоянии.

Блок 11 анализа формирует сигнал сбоя, если будет выявлено несоответствие между признаками оС и Xi

0

Сигналом с выхода элемента ИЛИ 3 блок 11 опрашивается и при.отсутствии сигнала сбоя на выходе блока 11 равен нулю. При наличии сигнала сбоя на выходе блока 11 анализа появится

5 сигнал, который установит триггер 12 фиксации сбоя, соединенный с третьим входом операционного блока 1, в единичное состояние.

i В конце цикла выборки и цикла исполнения команды сигнал с выхода элемента ИЛИ 3 устанавливает в нулевое состояние счетчик 9 микрокоманд ,, и регистр 10 логических условий и с началом нового цикла снова проводится подсчет микрокоманд аналогично описанному. Контроль микропрограмм с перемен ным числом микрокоманд. Предположим, что реализуется мик ропрограмма, алгоритм которой иэображен на фиг.2, В этсжм случае аналогично описанному вьзше происходит формирование признаков (кодов) данной микропрограммы Tj и числа реализованных мик рокомандоб г причем, так как в рассматриваемом случае могут реализова ся три последовательности микрокоманд, то oC-i может соответствоват либо , либо 2 , либо АЗ , т.е oL -CNVil,oL.. В регистр 10 логических условий в зависимости от порядка поступлени и значений логических условий Х и X может быть записан один из следующих кодов признаков |bytV-1,,33jb --i:ool,(l3.p -lAOl. Блок 11 анализа.сформирует сигна сбоя, если будет выявлено несоответ ствие между признаком (кодом) cL с одной стороны и признаками fy- и с другой стороны. Далгёё- устройство функционирует аналогично описанному выше для случ микропрограмм с постоянным числом микрокоманд. Формула изобретения 1, Микропрограммный процессор, содержащий операционный блок, первы вход которого соединен с первым вхо дом первого элемента И и является входом процессора, второй вход - с первым выходом регистра микрокоманд третий вход операционного блока со динен с единичным выходом триггера фиксации сбоя, первый выход операционного блока соединен с вторым входом первого элемента И и первым входом элемента ИЛИ, второй выход с вторьлл входом элемента ИЛИ и пер вым информационным входом регистра адреса микрокоманд, а третий выход с счетньы входсяи счетчика микрокоманд и управляющим входом блока памяти, информационный вход которого подключен к выходу регистра адреса икрокоманд, а выход - к входу регистра микрокоманд, второй выход которого соединен с первым входом второго элеглента И, второй вход которого через элемент НЕ соединен с вы содом элемента ИЛИ и установочным :,входом счетчика микрокоманд, а выход - с управляющим входом регистра адреса микрокаманд, второй информационный вход которого подключен к выходу первого элемента И, от л ичающийся тем, что, с целью повышения достоверности информации, в него дополнительно введены регистр логических условий, информационный вход которого подключен к четвертому выходу операционного блока, а управляющий вход - к выходу элемента ИЛИ, и блок анализа, первый, второй, третий и четвертый входы которого соединены с вторым выходом регистра микрокоманд, выходом счетчика микрокоманд, выходом регистра логических условий и выходом элемента ИЛИ соответственно, а выход - с установочным входом триггера фиксации сбоя. 2. Процессор по П.1, о т л ич а ю щ и и с я тем, что блок анализа содержит узел формирования контрольных признаков, первый и второй входы которого подключены к первому и третьему входам блока , соответственно, узел сравнения, первый вход которого соединен с вторым входом блока, а второй вход - с выходом узла формирования контрольных признаков и элемент И, первый и второй входы которого подключены к выходу уз.ла сравнения и четвертому входу блока соответственно, а выход - К выходу блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 481036, кл. Q06 F 9/14, 1975. 2.Авторское свидетельство СССР 490122, кл. G06 Т 9/14, 1975 . (прототип) .

Авторы

Даты

1979-12-25—Публикация

1977-04-26—Подача