(Sk} МИКРОПРОГРАММНЫЙ ПРОЦЕССОР С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммный процессор | 1980 |

|

SU896629A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

Изобретение относится к вычислительной технике, в частности к процессорам с контролем функционирова- J; ния и восстановлением при сбоях. |

Известен программный процессор, включающий в себя операционный блок, блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, триггер фиксации сбоя, элементы И, ИЛИ, НЕ 1 .

Недостатком указанного устройства являетс.я низкая оперативность контроля и восстановления работы устройства, большой объем контрольного оборудования.

Известен также микропрограммный i процессор с восстановлением при сбоях, содержащий операционный блок, блок памяти, регистры адреса и микрокоманд, счетчик, регистр адреса повтора, элементы И, ИЛИ Г2 J

Недостатками этого устройства являются ограниченные функциональные возможности, обусловленные тем, что,

восстановление информации осущест- , вляется путем рвторения микрокоманд, при выполнении которых обнаружен сбой. Это предъявляет дополнительные требования к характеру микрокоманд и средствам их восстановления.

Наиболее близким к предлагаемому по технической сущности является процессор, содержащий регистр логиtoческих условий, счетчик микрокоманд, четыре блока элементов И, первый элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки, первый одновибратор, триггер фиксации сбоя,

15 регистр микрокоманд,.регистр адреса, блок памяти и операционный блок, первый вход, которого связан с входом процессора и первым входом первого блока элементов И, второй, третий,

20 и четвертый входы, первый и второй выходы соединены с единичным выходом триггера фиксации сбоя,.входом синхронизирующих импульсов, первым вы39

ходом регистра микрокоманд, выходом результата операции и первым выходом третьего блока элементов И соответственно, третий выход соединен с вторым входом первого блока элементов И и первым входом элемента ИЛИ-НЕ, четвертый выход соединен с вторым входом .элемента ИЛИ-НЕ и установочным входом регистра адреса, пятый выход соединен с входом управления считывания блока памяти и счетным входом счетчика микрокоманд, выходы которого через первый элемент ИЛИ, первый элемент И и одновибратор соединены с единичным входом триггера фиксации сбоя, а установочный вход соединен с вы :одом четвертого блока элементов И, первый вход которого соединен с выходом регистра логических условий, информационный вход котОрого связан с выходом третьего блока элементов И и первым Выходом второго блока элементов И, выход которого, второй и третий входы соеди;нены соответственно с первым входом регистра адреса, выходом элемента ИЛИ-НЕ и вторым выходом регистра микрокоманд, третий выход которого соединен с вторым входом третьего и четвертого блоков элементов И, четвертый выход соединен с третьим вхО дом четвертого блока элементов И и через элемент задержки с установоч.ным входом первого регистра логических условий, пятый выход соединен с третьим входом одноименного блока элементов И и вторым входом первого элемента И, вход соединен с выходом блока памяти, вход которого соединен с выходом регистра адреса 31

Недостатком этого процессора является низкая оперативность восстановления работы при сбоях,

При обнаружении ошибки работа процессора блокируется и происходит обращение к ОЗУ для вызова программы анализа ошибки и восстановления работы устройства. Очевидно, что это сравнительно длительный процесс, так как такую программу необходимо вызвать, запросить соответствующие исходные данные (слово состояния программы ), проанализировать промежуточные результаты решения, если таковые имеются и т.д. Кроме того, программно необходимо формировать адрес микрокоманды повтора, что реализовать затруднительно, так как.

14

например, в ЕС ЭВМ нельзя в программе задавать адреса микрокоманд.Это приводит к необходимости повторного выполнения операции, при выполнении которой произошел сбой, хотя в этом, может быть и нет необходимости ввиду того, что восстановление зачастую можно начать с некоторой внутренней микрокоманды операции.

Цель изобретения - повьшение быстродействия восстановления вычислительного процесса при сбоях.

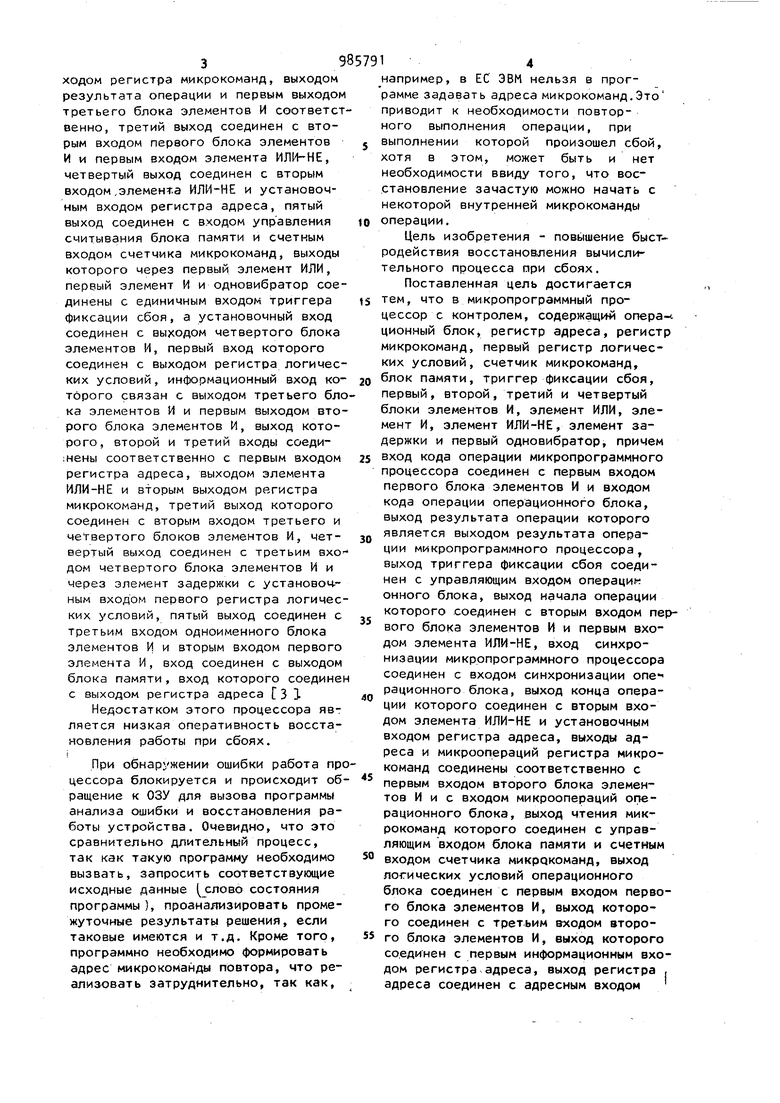

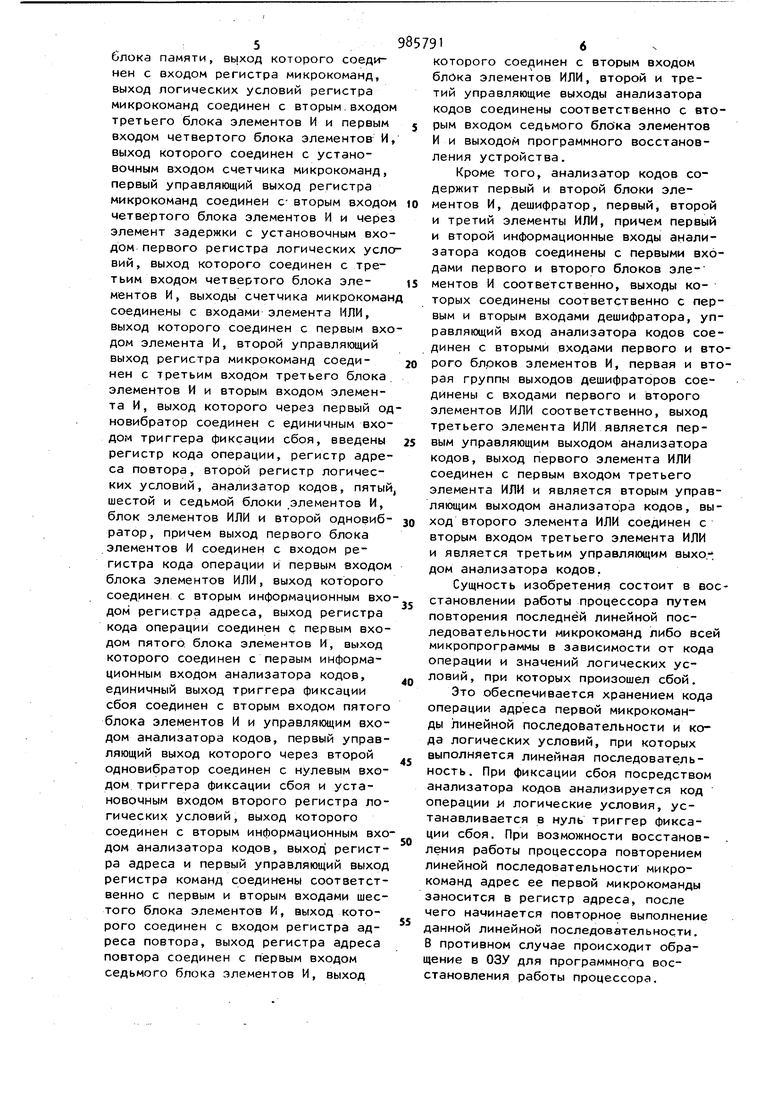

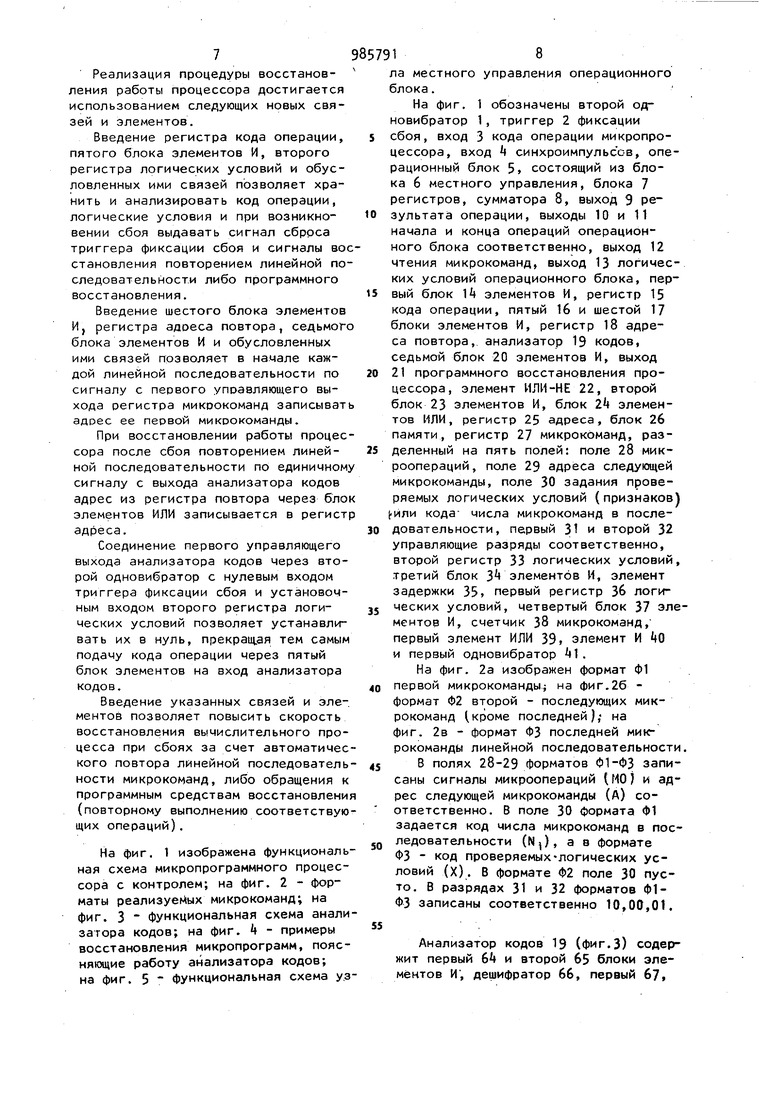

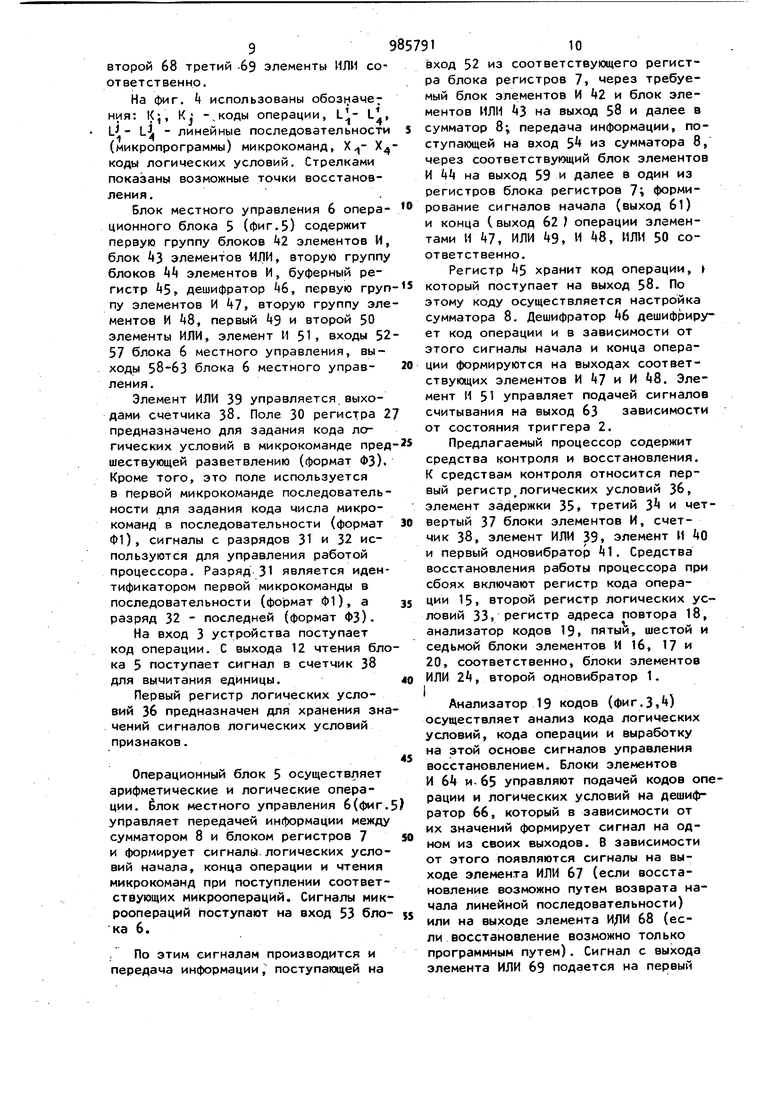

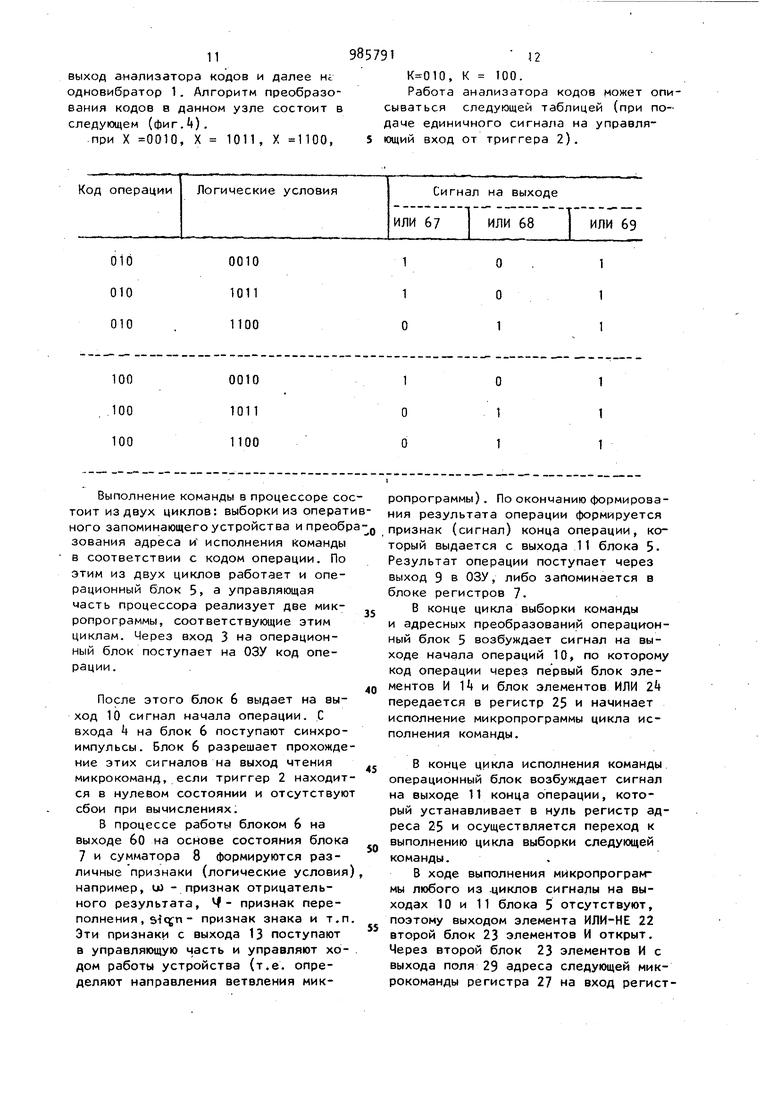

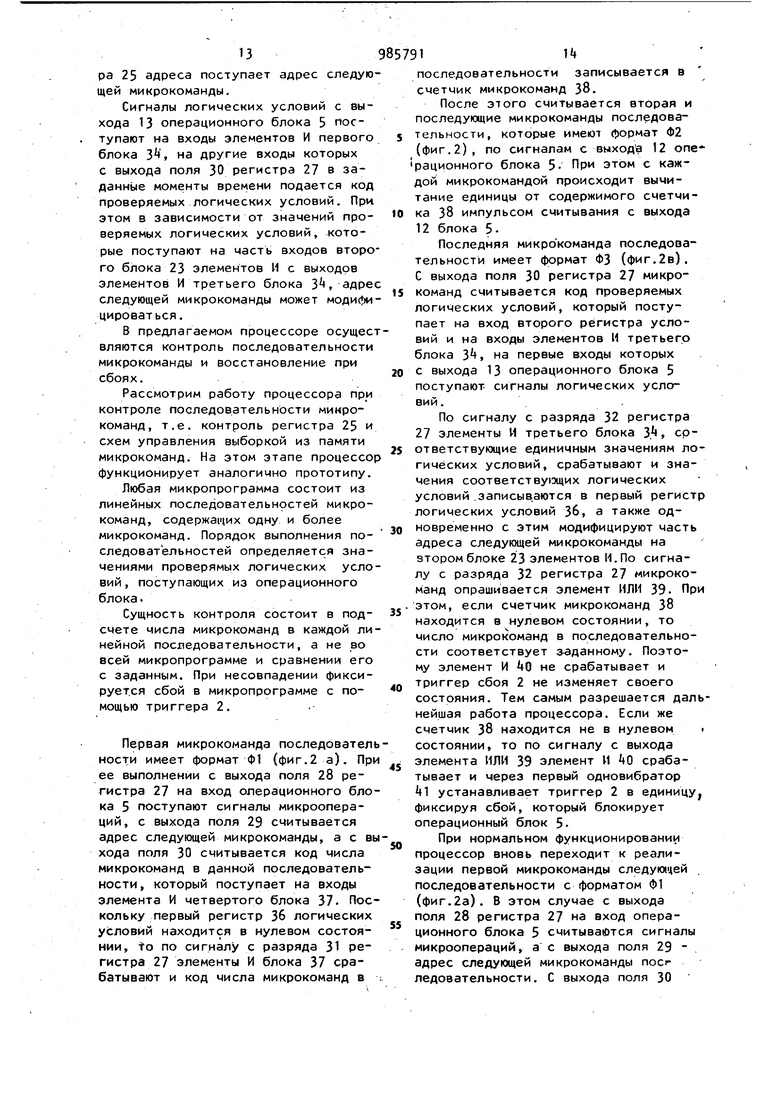

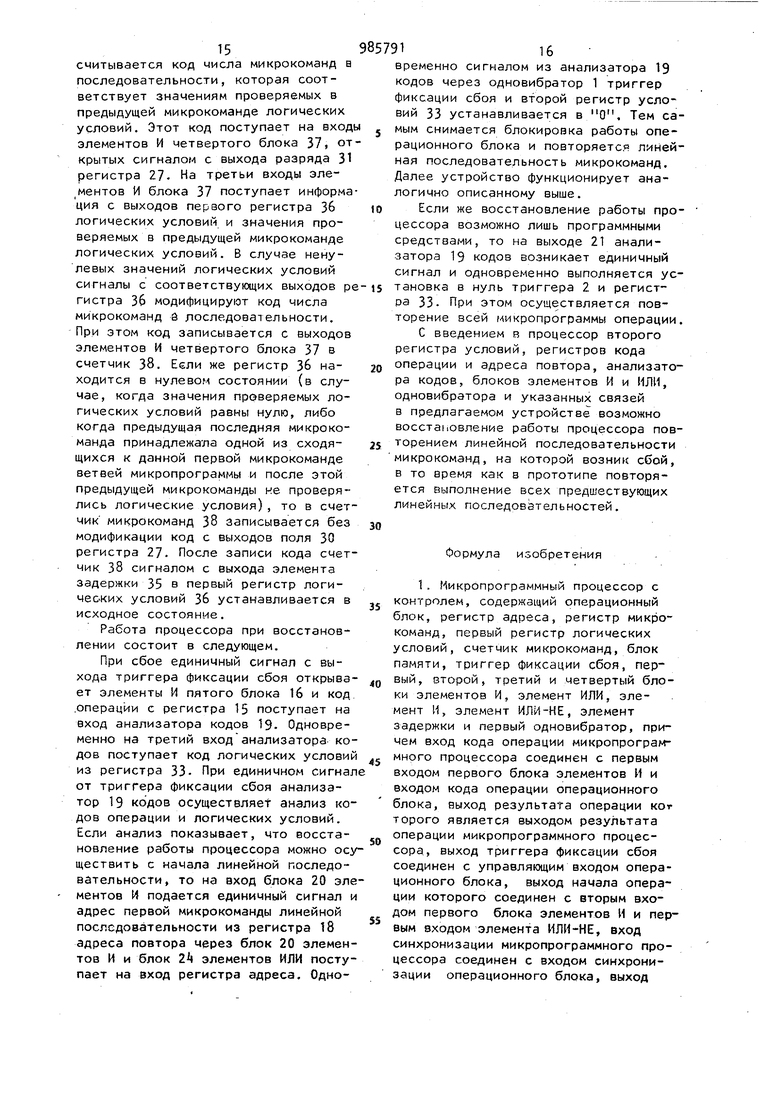

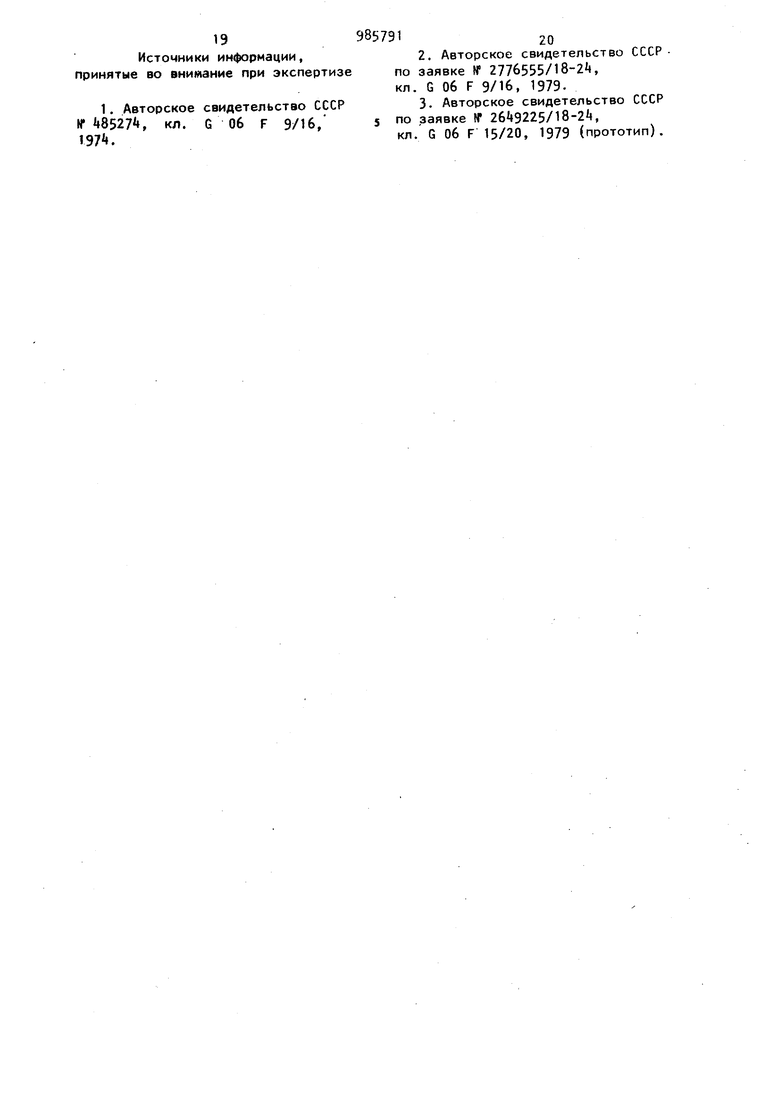

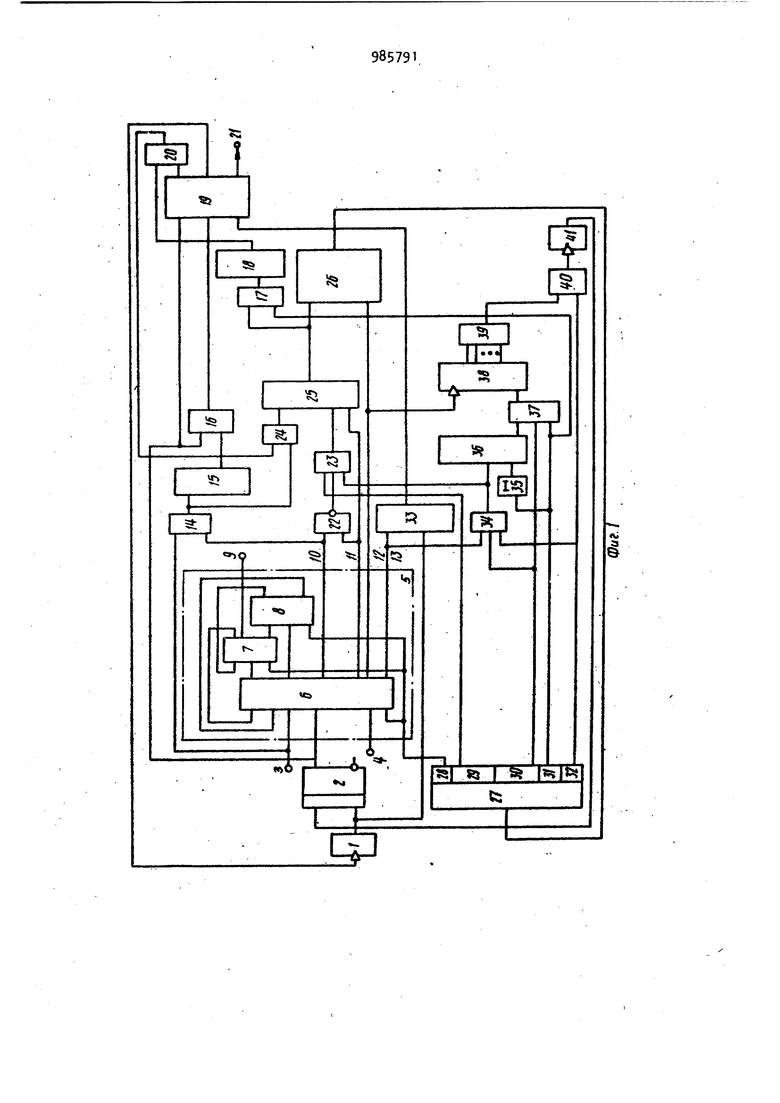

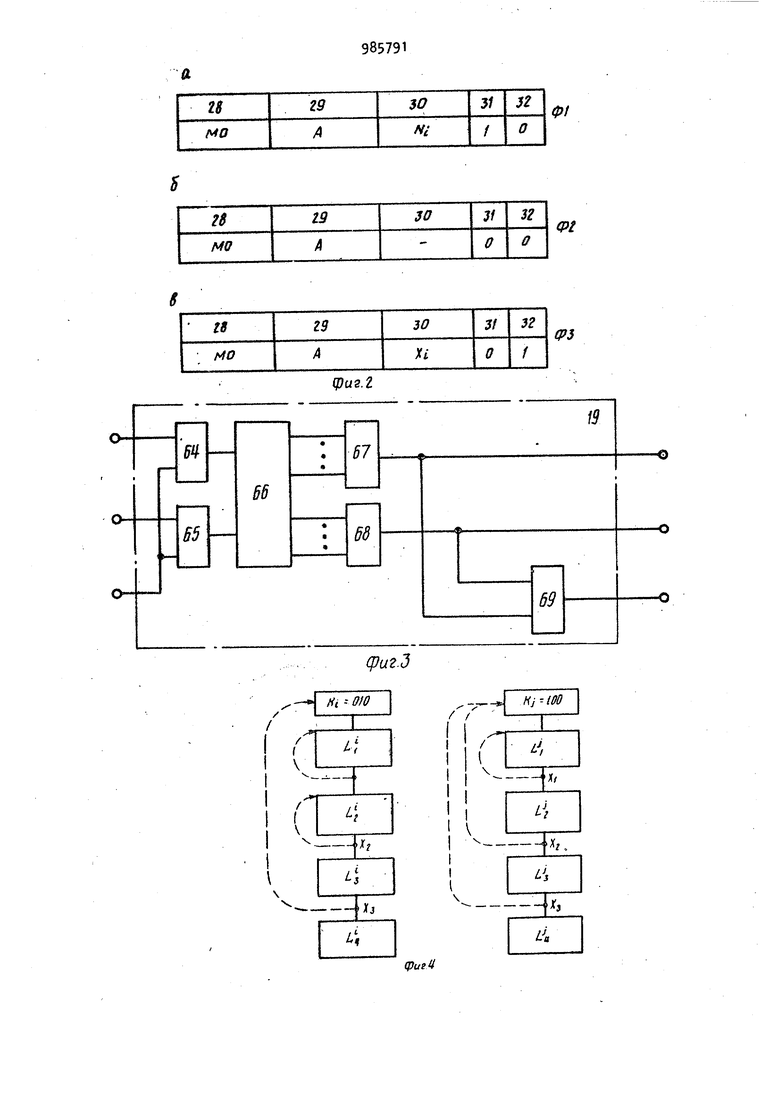

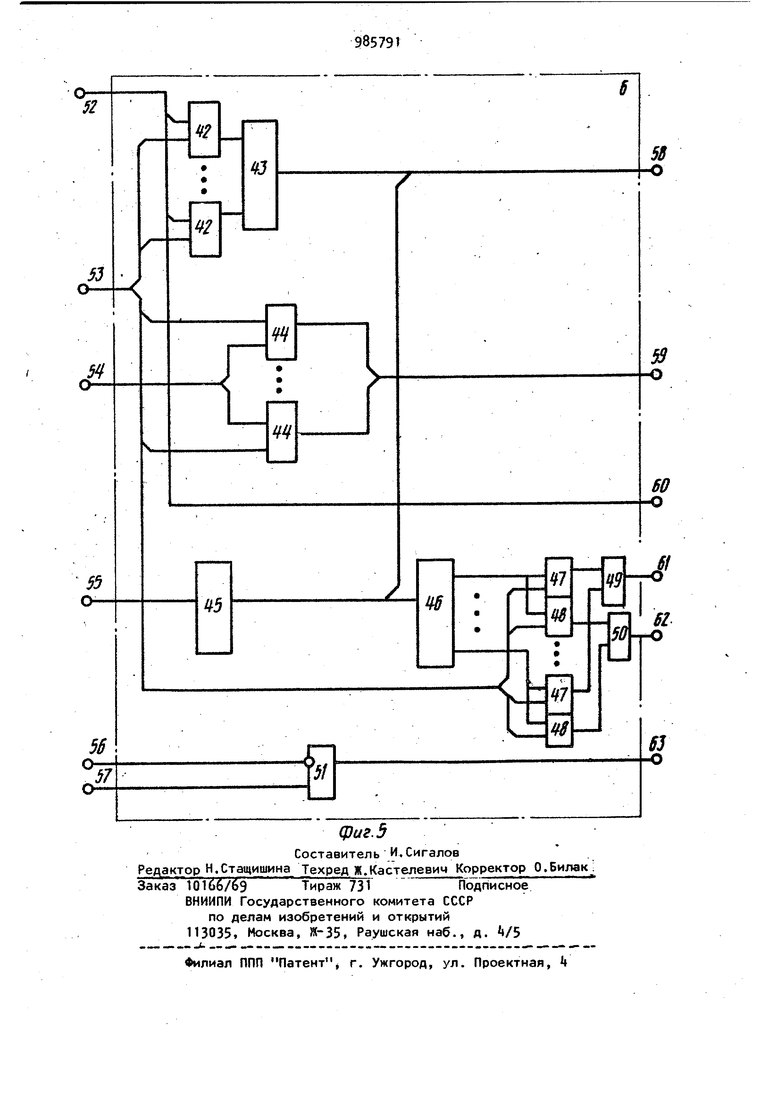

Поставленная цель достигается тем, что в микропрограммный процессор с контролем, содержащий опера ционный блок, регистр адреса, регист микрокоманд, первый регистр логических условий, счетчик микрокоманд, блок памяти, триггер фиксации сбоя, первый, второй, третий и четвертый блоки элементов И, элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки и первый одновибратор, причем вход кода операции микропрограммного процессора соединен с первым входом первого блока элементов И и входом кода операции операционного блока, выход результата операции которого является выходом результата операции микропрограммного процессора выход триггера фиксации сбоя соединен с управляющим входом операции онного блока, выход начала операции которого соединен с вторым входом певого блока элементов И и первым входом элемента ИЛИ-НЕ, вход синхронизации микропрограммного процессора соединен с входом синхронизации oneрационного блока, выход конца операции которого соединен с вторым входом элемента ИЛИ-НЕ и установочным входом регистра адреса, выходы адреса и микроопераций регистра микрокоманд соединены соответственно с первым входом второго блока элементов И и с входом микроопераций операционного блока, выход чтения микрокоманд которого соединен с управляющим входом блока памяти и счетным входом счетчика микрокоманд, выход логических условий операционного блока соединен с первым входом первого блока элементов И, выход которого соединен с третьим входом второго блока элементов И, выход которого соединен с первым информационным входом регистра адреса, выход регистра адреса соединен с адресным входом блока памяти, выход которого соединен с входом регистра микрокоманд, выход логических условий регистра микрокоманд соединен с вторым.входом третьего блока элементов И и первым входом четвертого блока элементов И, выход которого соединен с установочным входом счетчика микрокоманд, первый управляющий выход регистра микрокоманд соединен с- вторым входом четвертого блока элементов И и через элемент задержки с установочным входом первого регистра логических услс ВИЙ, выход которого соединен с третьим входом четвертого блока элементов И, выходы счетчика микрокоман соединены с входами элемента ИЛИ, выход которого соединен с первым вхо дом элемента И, второй управляющий выход регистра микрокоманд соединен с третьим входом третьего блока, элементов И и вторым входом элемента И, выход которого через первый од новибратор соединен с единичным входом триггера фиксации сбоя, введены регистр кода операции, регистр адреса повтора, второй регистр логических условий, анализатор кодов, пятый шестой и седьмой блоки элементов И, блок элементов ИЛИ и второй одновибратор, причем выход первого блока элементов И соединен с входом регистра кода операции и первым входом блока элементов ИЛИ, выход которого соединен с вторым информационным вхо дом регистра адреса, выход регистра кода операции соединен 5 первым входом пятого блока элементов И, выход которого соединен с первым информационным входом анализатора кодов, единичный выход триггера фиксации сбоя соединен с вторым входом пятого блока элементов И и управляющим входом анализатора кодов, первый управляющий выход которого через второй одновибратор соединен с нулевым входом триггера фиксации сбоя и установочным входом второго регистра логических условий, выход которого соединен с вторым информационным вхо дом анализатора кодов, выход регистра адреса и первый управляющий выход регистра команд соединены соответственно с первым и вторым входами шестого блока элементов И, выход которого соединен с входом регистра адреса повтора, выход регистра адреса повтора соединен с первым входом седьмого блока элементов И, выход которого соединен с вторым входом блока элементов ИЛИ, второй и третий управляющие выходы анализатора кодов соединены соответственно с вторым входом седьмого блока элементов И и выходо(Ц программного восстановления устройства. Кроме того, анализатор кодов содержит первый и второй блоки элементов И, дешифратор, первый, второй и третий элементы ИЛИ, причем первый и второй информационные входы анализатора кодов соединены с первыми входами первого и второго блоков элементов И соответственно, выходы которых соединены соответственно с первым и вторым входами дешифратора, управляющий вход анализатора кодов соединен с вторыми входами первого и второго блрков элементов И, первая и вторая группы выходов дешифраторов соединены с входами первого и второго элементов ИЛИ соответственно, выход третьего элемента ИЛИ является первым управляющим выходом анализатора кодов, выход первого элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и является вторым управляющим выходом анализатора кодов, выход второго элемента ИЛИ соединен с вторым входом третьего элемента ИЛИ и является третьим управляющим выхо. дом анализатора кодов. Сущность изобретения состоит в восстановлении работы процессора путем повторения последней линейной последовательности микрокоманд либо всей микропрограммы в зависимости от кода операции и значений логических условий, при которых произошел сбой. Это обеспечивается хранением кода операции адреса первой микрокоманды линейной последовательности и кода логических условий, при которых выполняется линейная последовательность . При фиксации сбоя посредством анализатора кодов анализируется код операции yi логические условия, устанавливается в нуль триггер фиксации сбоя. При возможности восстановления работы процессора повторением линейной последовательности микрокоманд адрес ее первой микрокоманды заносится в регистр адреса, после чего начинается повторное выполнение данной линейной последовательности. В противном случае происходит обращение в ОЗУ для программного восстановления работы процессора. Реализация процедуры восстановления работы процессора достигается использованием следующих новых связей и элементов. Введение регистра кода операции, пятого блока элементов И, второго регистра логических условий и обусловленных ими связей позволяет хранить и анализировать код операции, логические условия и при возникновении сбоя выдавать сигнал сброса триггера фиксации сбоя и сигналы вос становления повторением линейной по следовательности либо программного восстановления. Введение шестого блока элементов Mj регистра адреса повтора, седьмого блока элементов И и обусловленных ими связей позволяет в начале каждой линейной последовательности по сигналу с первого управляющего выхода регистра микрокоманд записыват адрес ее первой микрокоманды. При восстановлении работы процес сора после сбоя повторением линейной последовательности по единичном сигналу с выхода анализатора кодов адрес из регистра повтора через бло элементов ИЛИ записывается в регист адреса. Соединение первого управляющего выхода анализатора кодов через второй одновибратор с нулевым входом триггера фиксации сбоя и установочным входом второго регистра логических условий позволяет устанавливать их в нуль, прекращая тем самым подачу кода операции через пятый блок элементов на вход анализатора кодов. Введение указанных связей и элементов позволяет повысить скорость восстановления вычислительного процесса при сбоях за счет автоматичес кого повтора линейной последователь ности микрокоманд, либо обращения к программным средствам восстановлени (повторному выполнению соответствую щих операций). На фиг. 1 изображена функциональ ная схема микропрограммного процессора с контролем; на фиг. 2 - форматы реализуемых микрокоманд; на фиг. 3 функциональная схема анали затора кодов; на фиг. 4 - примеры восстановления микропрограмм, поясняющие работу анализатора кодов; на фиг. 5 - функциональная схема у.з 18 ла местного управления операционного блока. На фиг. 1 обозначены второй одновибратор 1, триггер 2 фиксации сбоя, вход 3 кода операции микропроцессора, вход Ц синхроимпульсов, операционный блок 5. состоящий из блока 6 местного управления, блока 7 регистров, сумматора 8, выход Э результата операции, выходы 10 и 11 начала и конца операций операционного блока соответственно, выход 12 чтения микрокоманд, выход 13 логических условий операционного блока, первый блок }Ц элементов И, регистр 15 кода операции, пятый 16 и шестой 17 блоки элементов И, регистр 18 адреса повтора,, анализатор 19 кодов, седьмой блок 20 элементов И, выход 21 программного восстановления процессора, элемент ИЛН-НЕ 22, второй блок 23 элементов И, блок 2 элементов ИЛИ, регистр 25 адреса, блок 26 памяти, регистр 27 микрокоманд, разделенный на пять полей: поле 28 микроопераций , поле 29 адреса следующей микрокоманды, поле 30 задания проверяемых логических условий (признаков) или кода- числа микрокоманд в последовательности, первый 31 и второй 32 управляющие разряды соответственно, второй регистр 33 логических условий, третий блок З элементов И, элемент задержки 35 первый регистр Зб логических условий, четвертый блок 37 элементов И, счетчик 38 микрокоманд, первый элемент ИЛИ 39 элемент И ЦО и первый одновибратор 1. На фиг. 2а изображен формат Ф1 первой микрокоманды; на фиг.26 формат Ф2 второй - последующих микрокоманд (кроме последней); на фиг. 2в - формат ФЗ последней микрокоманды линейной последовательности. В полях 28-29 форматов Ф1-ФЗ записаны сигналы микроопераций (МО) и адрес следующей микрокоманды (А) соответственно. В поле 30 формата Ф1 задается код числа микрокоманд в последовательности (N), а в формате ФЗ - код проверяемых-логических условий (X). В формате Ф2 поле 30 пусто. В разрядах 31 и 32 форматов Ф1ФЗ записаны соответственно 10,00,01. Анализатор кодов 19 (фиг.З) содержит первый 64 и второй 65 блоки элементов И, дешифратор 66, первый 67, второй 68 третий -б9 элементы ИЛИ соответственно. На фиг, k использованы обоз(;1аче7 Kj операции, L- L, ния: К:, L -i-iлинейные последовательности (микропрограммы) микрокоманд, Х Стрелками коды логических условии, показаны возможные точки восстановления . Блок местного управления 6 операционного блока 5 (фиг.5) содержит первую группу блоков 42 элементов И, блок 43 элементов I-W, вторую группу блоков 44 элементов И, буферный регистр 45, дешифратор 46, первую груп пу элементов И 47, вторую группу эле ментов И 48, первый 49 и второй 50 элементы ИЛИ, элемент И 51, входы 52 57 блока 6 местного управления, выходы 58-63 блока 6 местного управления. Элемент ИЛИ 39 управляется выходами счетчика 38. Поле 30 регистра 2 предназначено для задания кода логических условий в микрокоманде пред шествующей разветвлению (формат ФЗ). Кроме того, это поле используется в первой микрокоманде последовательности для задания кода числа микрокоманд в последовательности (формат Ф1), сигналы с разрядов 31 и 32 используются для управления работой процессора. Разряд 31 является идентификатором первой микрокоманды в последовательности (формат Ф1), а разряд 32 - последней (формат ФЗ). На вход 3 устройства поступает код операции. С выхода 12 чтения бло ка 5 поступает сигнал в счетчик 38 для вычитания единицы. Первый регистр логических условий 36 предназначен для хранения зна чений сигналов логических условий признаков. Операционный блок 5 осуществляет арифметические и логические операции. §лок местного управления 6(.5 управляет передачей информации между сумматором 8 и блоком регистров 7 и формирует сигналь, логических условий начала, конца операции и чтения микрокоманд при поступлении соответствующих микроопераций. Сигналы микроопераций поступают на вход 53 блока 6. По этим сигналам производится и передача информации, поступающей на 9110 вход 52 из соответствующего регистра блока регистров 7, через требуемый блок элементов И 2 и блок элементов ИЛИ на выхо/| 58 и далее в сумматор 8; передача информации, поступающей на вход 5 из сумматора 8, через соответствующий блок элементов И k на выход 59 и далее в один из регистров блока регистров 7; формирование сигналов начала (выход 61) и конца С выход 62 ) операции элементами И , ИЛИ Й9, И 48, ИЛИ 50 соответственно. Регистр 5 хранит код операции, который поступает на выход 58. По этому коду осуществляется настройка сумматора 8. Дешифратор 46 дешифрирует код операции и в зависимости от этого сигналы начала и конца операции формируются на выходах соответствующих элементов И 47 и И 48. Элемент И 51 управляет подачей сигналов считывания на выход 63 зависимости от состояния триггера 2. Предлагаемый процессор содержит средства контроля и восстановления. К средствам контроля относится первый регистр,логических условий 36, элемент задержки 35, третий 34 и четвертый 37 блоки элементов И, счетчик 38, элемент ИЛИ 39, элемент И 40 и первый одновибратор 41. Средства восстановления работы процессора при сбоях включают регистр кода операции 15, второй регистр логических условий 33, регистр адреса повтора 18, анализатор кодов 19, пятый, шестой и седьмой блоки элементов И 16, 17 и 20, соответственно, блоки элементов ИЛИ 24, второй одновибратор 1. Анализатор 19 кодов (фиг.3,4) осуществляет анализ кода логических условий, кода операции и выработку на этой основе сигналов управления восстановлением. Блоки элементов И 64 и.65 управляют подачей кодов операции и логических условий на дешифратор 66, который в зависимости от их значений формирует сигнал на одном из своих выходов. В зависимости от этого появляются сигналы на выходе элемента ИЛИ 67 (если восстановление возможно путем возврата начала линейной последовательности) или на выходе элемента ИЛИ 68 (если восстановление возможно только программным путем). Сигнал с выхода элемента ИЛИ 69 подается на первый 11 выход анализатора кодов и далее Hi одновибратор 1. Алгоритм преобразования кодов в данном узле состоит в следующем (фиг. if). при X 0010, X 1011 , X 1100,

0010 1011 1100 Выполнение команды в процессоре со тоит из двух циклов: выборки из операт ного запоминающего устройства ипреобр зования адреса и исполнения команды в соответствии с кодом операции. По этим из двух циклов работает и операционный блок 5 а управляющая часть процессора реализует две микропрограммы, соответствующие этим циклам. Через вход 3 на операционный блок поступает на ОЗУ код операции. После этого блок 6 выдает на выход 10 сигнал начала операции. С входа k на блок 6 поступают синхроимпульсы. Блок 6 разрешает прохожде ние этих сигналов на выход чтения микрокоманд, если триггер 2 находит ся в нулевом состоянии и отсутствую сбои при вычислениях. В процессе работы блоком 6 на выходе 60 на основе состояния блока 7 и сумматора 8 формируются различные признаки (логические условия например, u) - признак отрицательного результата, Ч- признак переполнения , - признак знака и т.п Эти признаки с выхода 13 поступают в управляющую часть и управляют ходом работы устройства (т.е. определяют направления ветвления микО О 1 85791 , К 100. Работа анализатора кодов может описываться следующей таблицей (при подаче единичного сигнала на управляющий вход от триггера 2), ропрограммы). По окончанию формирования результата операции формируется признак (сигнал) конца операции, который выдается с выхода 11 блока 5. Результат операции поступает через выход 9 в ОЗУ, либо запоминается в блоке регистров 7В конце цикла выборки команды и адресных преобразований операционный блок 5 возбуждает сигнал на выходе начала операций 10, по которому код операции через первый блок элементов И 1 и блок элементов ИЛИ 2k передается в регистр 25 и начинает исполнение микропрограммы цикла исполнения команды. В конце цикла исполнения команды операционный блок возбуждает сигнал на выходе 11 конца операции, который устанавливает в нуль регистр адреса 25 и осуществляется переход к выполнению цикла выборки следующей команды. В ходе выполнения микропрограммы любого из .циклов сигналы на выходах 10 и 11 блока 5 отсутствуют, поэтому выходом элемента ИЛИ-НЕ 22 второй блок 23 элементов И открыт. Через второй блок 23 элементов И с выхода поля 29 адреса следующей микрокоманды регистра 27 на вход регист13pa 25 адреса поступает адрес следую щей микрокоманды. Сигналы логических условий с выхода 13 операционного блока 5 поступают на входы элементов И первого блока 3, на другие входы которых с выхода поля 30 регистра 27 в заданные моменты времени подается код проверяемых логических условий. При этом в зависимости от значений проверяемых логических условий, которые поступают на часть входов второ го блока 23 элементов И с выходов элементов И третьего блока З, адре следующей микрокоманды может модифи цироваться. В предлагаемом процессоре осущес вляются контроль последовательности микрокоманды и восстановление при сбоях. Рассмотрим работу процессора при контроле последовательности микрокоманд, т.е. контроль регистра 25 и схем управления выборкой из памяти микрокоманд. На этом этапе процессо функционирует аналогично прототипу. Любая микропрограмма состоит из линейных последовательностей микрокоманд, содержащих одну и более микрокоманд. Порядок выполнения последовательностей определяется значениями проверямых логических усло вий, поступающих из операционного блока. Сущность контроля состоит в подсчете числа микрокоманд в каждой ли нейной последовательности, а не во всей микропрограмме и сравнении его с заданным. При несовпадении фиксируется сбой в микропрограмме с помощью триггера 2. Первая микрокоманда последователь ности имеет формат Ф1 (фиг.2 а). При ее выполнении с выхода поля 28 регистра 27 на вход операционного бло ка 3 поступают сигналы микроопераций, с выхода поля 29 считывается адрес следующей микрокоманды, а с вы хода поля 30 считывается код числа микрокоманд в данной последовательности , который поступает на входы элемента И четвертого блока 37. Поскольку первый регистр 36 логических условий находится в нулевом состоянии, to по сигналу с разряда 31 регистра 27 элементы И блока 37 срабатывают и код числа микрокоманд в 1 последовательности записывается в счетчик микрокоманд 38. После этого считывается вторая и последующие микрокоманды последовательности, которые имеют формат Ф2 (фиг.2), по сигналам с выхода 12 one рационного блока 5- При этом с каждой микрокомандой происходит вычитание единицы от содержимого счетчика 38 импульсом считывания с выхода 12 блока 5Последняя микрокоманда последовательности имеет формат ФЗ (фиг.2в). С выхода поля 30 регистра 27 микрокоманд считывается код проверяемых логических условий, который поступает на вход второго регистра условий и на входы элементов И третьего блока на первые входы которых с выхода 13 операционного блока 5 поступают сигналы логических условий. По сигналу с разряда 32 регистра 27 элементы И третьего блока 3, срответствующие единичным значениям логических условий, срабатывают и значения соответству1эщих логических условий .записыв.аются в первый регистр логических условий 36, а также одновременно с этим модифицируют часть адреса следующей микрокоманды на втором блоке элементов И. По сигналу с разряда 32 регистра 27 микрокоманд опрашивается элемент ИЛИ 39- При этом, если счетчик микрокоманд ЗВ находится в нулевом состоянии, то число микрокоманд в последовательности соответствует заданному. Поэтому элемент И 40 не срабатывает и триггер сбоя 2 не изменяет своего состояния. Тем самым разрешается дальнейшая работа процессора. Если же счетчик 38 находится не в нулевом состоянии, то по сигналу с выхода элемента ИЛИ 39 элемент И 40 срабатывает и через первый одновибратор 41 устанавливает триггер 2 в единицу, фиксируя сбой, который блокирует операционный блок 5При нормальном функционировании процессор вновь переходит к реализации первой микрокоманды следую1цей последовательности с форматом Ф1 (фиг.2а). В этом случае с выхода поля 28 регистра 27 на вход операционного блока 5 считываются сигналы микроопераций, а с выхода поля 29 адрес следующей микрокоманды пост ледовательности, С выхода поля 30 считывается код числа микрокоманд в последовательности, которая соответствует значениям проверяемых в предыдущей микрокоманде логических условий. Этот код поступает на входы элементов И четвертого блока 37, от крытых сигналом с выхода разряда 31 регистра 27. На третьи входы эле ментов И блока 37 поступает информа ция с выходов первого регистра 36 логических условий и значения проверяемых в предыдущей микрокоманде логических условий. В случае ненулевых значений логических условий сигналы с соответствугацих выходов ре гистра 36 модифицируют код числа микрокоманд S лоследовательности. При этом код записывается с выходов элементов И четвертого блока 37 в счетчик 38. Еели же регистр 36 находится в нулевом состоянии (в случае, когда значения проверяемых логических условий равны нулю, либо когда предыдущая последняя микрокоманда принадлежала одной из сходящихся к данной первой микрокоманде ветвей микропрограммы и после этой предыдущей микрокоманды не проверялись логические условия), то в счетчик микрокоманд 38 записывается без модификации код с выходов поля 30 регистра 27. После записи кода счет чик 38 сигналом с выхода элемента задержки 35 в первый регистр логических условий Зб устанавливается в исходное состояние. Работа процессора при восстановлении состоит в следующем. При сбое единичный сигнал с выхода триггера фиксации сбоя открыва ет элементы И пятого блока 16 и код .операции с регистра 15 поступает на вход анализатора кодов 19- Одновременно на третий вход анализатора ко дов поступает код логических услови из регистра 33. При единичном сигна от триггера фиксации сбоя анализатор 19 кодов ocyщecт8ляet анализ ко дов операции и логических условий. Если анализ показывает, что восстановление работы процессора можно ос ществить с начала линейной последовательности, то на вход блока 20 эл ментов И подается единичный сигнал адрес первой микрокоманды линейной последовательности из регистра 18 адреса повтора через блок 20 элемен тов И и блок 2 элементов ИЛИ посту пает на вход регистра адреса, Одно116временно сигналом из анализатора 19 кодов через одновибратор 1 триггер фиксации сбоя и второй регистр условий 33 устанавливается в О, Тем самым снимается блокировка работы операционного блока и повторяется линейная последовательность микрокоманд. Далее устройство функционирует аналогично описанному выше. Если же восстановление работы процессора возможно лишь программными средствами, то на выходе 21 анализатора 19 кодов возникает единичный сигнал и одновременно выполняется установка в нуль триггера 2 и регистра 33. При этом осуществляется повторение всей микропрограммы операции. С введением в процессор второго регистра условий, регистров кода операции и адреса повтора, анализатора кодов, блоков элементов И и ИЛИ, одновибратора и указанных связей в предлагаемом устройстве возможно восстановление работы процессора повторением линейной последовательности микрокоманд, на которой возник сбой, в то время как в прототипе повторяется выполнение всех предшествующих линейных последовательностей. Формула изобретения 1. Иикропрограммный процессор с контролем, содержащий операционный блок, регистр адреса, регистр микрокоманд, первый регистр логических условий, счетчик микрокоманд, блок памяти, триггер фиксации сбоя, первый, второй, третий и четвертый блоки элементов И, элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки и первый одновибратор, причем вход кода операции микропрограммного процессора соединен с первым входом первого блока элементов И и входом кода операции операционного блока, выход результата операции ког торого является выходом результата операции микропрограммного процессора, выход триггера фиксации сбоя соединен с управляющим входом операционного блока, выход начала операции которого соединен с вторым входом первого блока элементов И и первым входом элемента ИЛИ-НЕ, вход синхронизации микропрограммного процессора соединен с входом синхронизации операционного блока, выход конца операции которого соединен с вторым входом элемента ИЛИ-НЕ и установочным входом регистра адреса, выходы адреса и микроопераций регистра микрокоманд соединены соответственно с первым входом второго блока элементов И и с входом микроопераций операционного блока, выход чтения микрокоманд которого соединен с управляйщим входом блока памяти и счетным входом счетчика микрокоманд, выход логических условий операционного блока соединен с г ервым входом первого блока элементов И, выход которогго соединен с третьим входом второго блока элементов И,.выход которого соединен с первым информационным входом регистра адреса, выход регистра адреса соединен с адресным входом блока памяти, выход которого соеди- зо нен с входом регистра микрокоманд, выход логических условий регистра микрокоманд соединен с вторым входом третьего блока элементов И и первым входом четвертого блока элементов И, 25

выход которого соединен с установочным входом счетчика микрокоманд, пер вый управляющий выход регистра микрокоманд соединен с вторым входом четвертого блока элементов И и через зо элемент задержки с установочным входом первого,регистра логических условий , выход которого соединен с третьим входом четвертого блока элементов И, выходы счетчика микрокома соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй управляющий выход регистра микрокоманд соед нен с третьим входом третьего блока элементов И и вторым входом элемента И, выход которого через первый одновибратор соединен с единичным входом триггера фиксации сбоя, о тличающийся тем, что, с целью повышения быстродействия восстановления вычислительного процесса при сбоях, в микропрограммный процессор введены регистр кода операции, регистр адреса повтора, второй регистр логических условий, ана лизатор кодов,пятый, шестой и седьмой блоки элементов И, блок элементов ИЛИ и второй одновибратор, причем выход первого блока элементов И соединен с входом.регистра кода опе рации и первым входом блока элементов ИЛИ, выход которого соединен с вторым информационным входом регист

третии управляющие выходы анализатора кодов соединены соответственно с вторым входом седьмого блока элементов И и выходом программного восстановления микропрограммного процессора.

1998579120

Источники информации,2. Авторское свидетельство СССР

принятые во внимание при экспертизе по заявке № 2776555/18-2,

кл. G 06 F 9/16, 1979.

Авторы

Даты

1982-12-30—Публикация

1981-07-02—Подача