Изобретение относится к области вычислительной и электронной техники, в частности к интегральным запоминающим устройствам, и может быть использовано в ирограммируемых системах памяти, сохраняющих информацию при отключении питания.

Известен накопитель для полупостоянного запоминающего устройства с электрической перезаиисью информации, содержащий матририцу заиомииающих МДП-транзисторов, истоки транзисторов каждого столбца которой подключены к разрядной шине, стоки - к истоку нагрузочного транзистора, затвор и сток последнего - к щиие питания. Затворы запоминающих транзисторов строк подсоединены к адресной щине.

Недостатком известного накопителя является невозможность совмещения высокого быстродействия в режиме считывания информации и малой рассеиваемой мощности в режиме перезаписи в связи с противоречивыми требованиями к нагрузочным транзисторам: для повышения быстродействия крутизну их необходимо увеличивать, для сиижения рассеиваемой мощности - уменьшать.

Цель изобретения - повышение быстродействия и надежности работы накопителя для иолупостояиного запоминающего устройства с электрической перезаписью информации.

Это достигается благодаря тому, что накопитель содержит в каждом столбце матрицы дополнительный тактирующий транзистор, включенный параллельно нагрузочному транзистору, причем затвор дополнительного тактирующего транзистора соединен с шиной тактирующего сигнала.

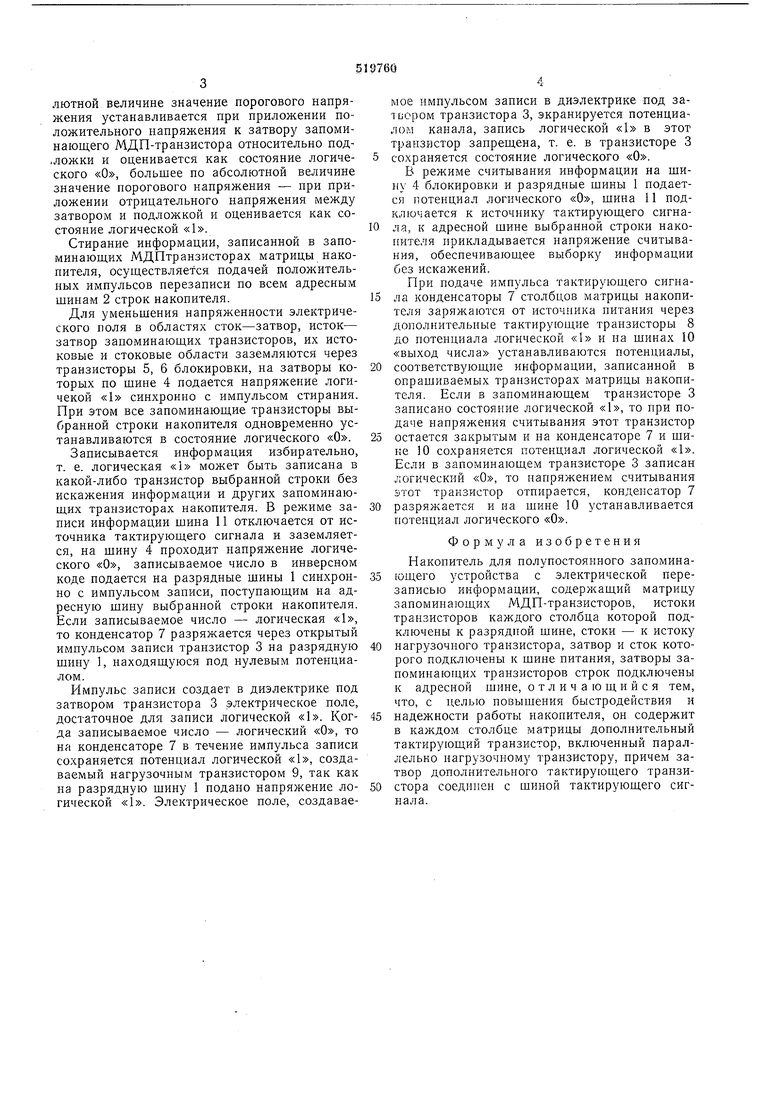

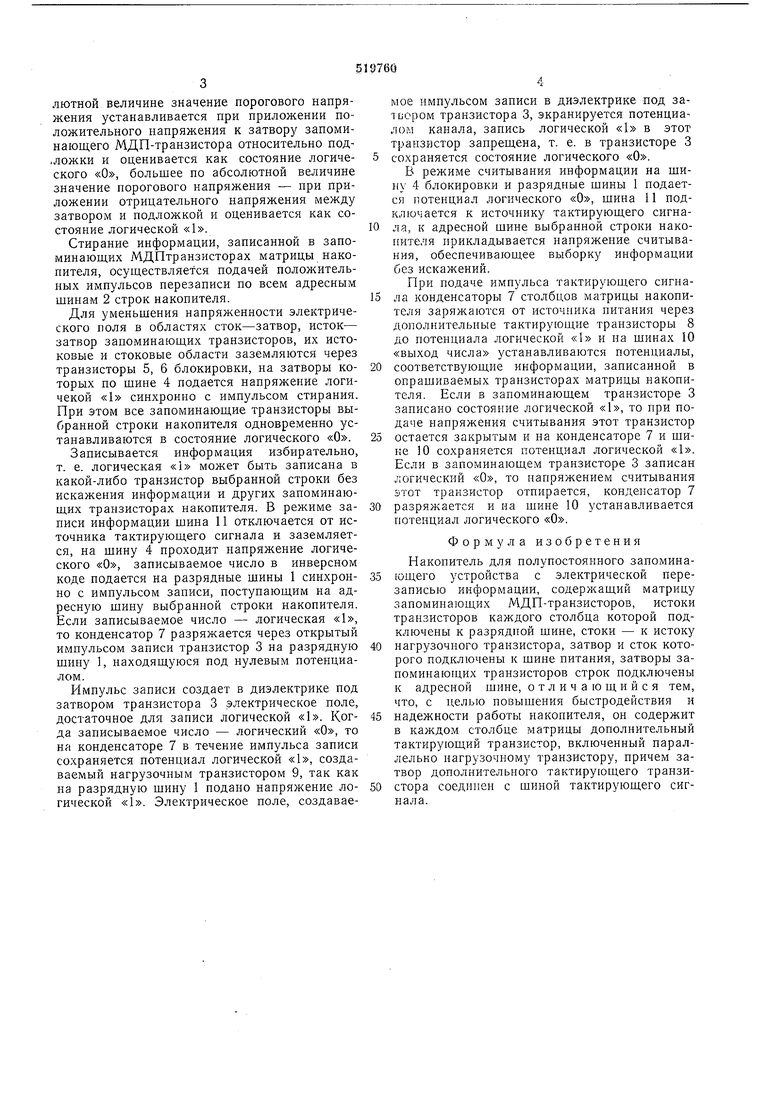

На чертеже представлена схема накопителя полупостоянного запоминающего устройства с электрической перезаписью ипформации.

Она содержит разрядные щины 1, адресные шины 2, запоминающие МДН-транзисторы 3 матрицы накопителя, обладающие электрически изменяемым пороговым напряжением, шину 4 блокировки, МДП-транзисторы 5, 6 блокировки, конденсаторы 7, образованные узловыми емкостями столбцов матрицы накопителя, дополнительные тактирующие МДНтранзисторы 8, нагрузочные МДП-транзнсторы 9, шины «выход числа 10, тактирующего сигнала 11, ннтания 12.

Накопитель полупостоянного запоминающего устройства работает в режимах стирания, записи и считывания информации. Двоичная информация отображается в запоминающем МДП-транзисторе накопителя в виде двух электрически изменяемых значений порогового напряжения, определяемых величиной заряда, наконленного на границе раздела двух диэлектриков. Меньшее по абсолютной величине значение порогового напряжения устанавливается при приложении положительного напряжения к затвору запоминающего МДП-транзистора относительно под,ложки и оценивается как состояние логического «О, большее но абсолютной величине значение порогового напряжения - при приложении отрицательного напряжения между затвором и подложкой и оценивается как состояние логической «1.

Стирание информации, записанной в запоминающих МДПтранзисторах матрицы накопителя, осуществляется подачей положительных импульсов перезаписи по всем адресным шинам 2 строк накопителя.

Для уменьшения напряженности электрического поля в областях сток-затвор, исток- затвор запоминающих транзисторов, их истоковые и стоковые области заземляются через транзисторы 5, 6 блокировки, на затворы которых по шине 4 подается напряжение логичекой «1 синхронно с импульсом стирания. При этом все запоминающие транзисторы выбранной строки накопителя одновременно устанавливаются в состояние логического «О.

Записывается информация избирательно, т. е. логическая «1 может быть записана в какой-либо транзистор выбранной строки без искажения информации и других запоминающих транзисторах накопителя. В режиме записи информации шина 11 отключается от источника тактирующего сигнала и заземляется, на шину 4 проходит напряжение логического «О, записываемое число в инверсном коде подается на разрядные шины 1 синхронно с импульсом записи, поступающим на адресную шину выбранной строки накопителя. Если записываемое число - логическая «1, то конденсатор 7 разряжается через открытый импульсом записи транзистор 3 на разрядную шину 1, находящуюся под нулевым потенциалом.

Импульс записи создает в диэлектрике под затвором транзистора 3 электрическое поле, достаточное для записи логической «1. Когда записываемое число - логический «О, то на конденсаторе 7 в течение импульса записи сохраняется потенциал логической «1, создаваемый нагрузочным транзистором 9, так как на разрядную шину 1 подано напряжение логической «1. Электрическое поле, создаваемое импульсом записи в диэлектрике под затьсром транзистора 3, экранируется потенциалом канала, запись логической «1 в этот транзистор запрещена, т. е. в транзисторе 3

5 сохраняется состояние логического «О.

В режиме считывания информации на шину 4 блокировки и разрядные шины 1 подается потенциал логического «О, шина 11 подключается к источнику тактирующего сигпа0 ла, к адресной шине выбранной строки накопителя прикладывается напряжение считывания, обеспечивающее выборку информации без искажений. При подаче импульса тактирующего сигнала конденсаторы 7 столбцов матрицы накопителя заряжаются от источника питания через дополнительные тактирующие транзисторы 8 до потенциала логической «1 и на шинах 10 «выход числа устанавливаются потенциалы,

0 соответствующие информации, записанной в опрашиваемых транзисторах матрицы накопителя. Если в запоминающем транзисторе 3 записано состояние логической «1, то при подаче напряжения считывания этот транзистор

5 остается закрытым и на конденсаторе 7 и щине 10 сохраняется потенциал логической «1. Если в запоминающем транзисторе 3 записан логический «О, то напряжением считывания этот транзистор отпирается, конденсатор 7

0 разряжается и на шине 10 устанавливается потенциал логического «О.

Формула изобретения

Пакопитель для полупостоянного запоминающего устройства с электрической перезаписью информации, содержащий матрицу запоминающих МДП-транзисторов, истоки транзисторов каждого столбца которой подключены к разрядной шине, стоки - к истоку

0 нагрузочного транзистора, затвор и сток которого подключены к шипе питания, затворы запоминающих транзисторов строк подключены к адресной шине, отличающийся тем, что, с целью повышения быстродействия и

5 надежности работы накопителя, он содержит в каждом столбце матрицы дополнительный тактирующий транзистор, включенный параллельно нагрузочному транзистору, причем затвор дополнительного тактирующего трапзи0 стора соединен с шиной тактирующего сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

Авторы

Даты

1976-06-30—Публикация

1973-10-01—Подача