1

Запоминающий элемент относится к области вычислительной техники и предназначен для работы в составе оперативного запоминающего устройства (ОЗУ).

В известном запоминающем элементе (ЗЭ) информация хранится в форме заряда на запоминающем конденсаторе, включенном между затвором информационного транзистора и землей, и определяет открытое или закрытое состояние информационного транзистора. Доступ к запоминающему конденсатору осуществляется через вентильный транзистор записи, когда на затворе последнего имеется разрешающий адресный импульс. Условный (в зависимости от состояния информационного транзистора) разряд шины считывания происходит через вентильный транзистор считывания при наличии на его затворе отпирающего адресного импульса, а также через информационный транзистор. Регенерация хранимой информации осуществляется путем ее считывания, пропускания через специальный усилитель регенерации и последующей записи в тот же ЗЭ, К запоминающему элементу подключены еще четыре шины, кроме нулевой.

Недостатками известного ЗЭ являются: необходимость в специальных усилителях регенерации при использовании ЗЭ в оперативных запоминающих устройствах, а также наличие большого числа шин доступа к ЗЭ, что приводит к сравнительно большой площади, занимаемой элементом на кристалле и снижению степени интеграции ОЗУ в целом. Наличие усилителей регенерации вызывает, кроме того, удлинение цикла регенерации.

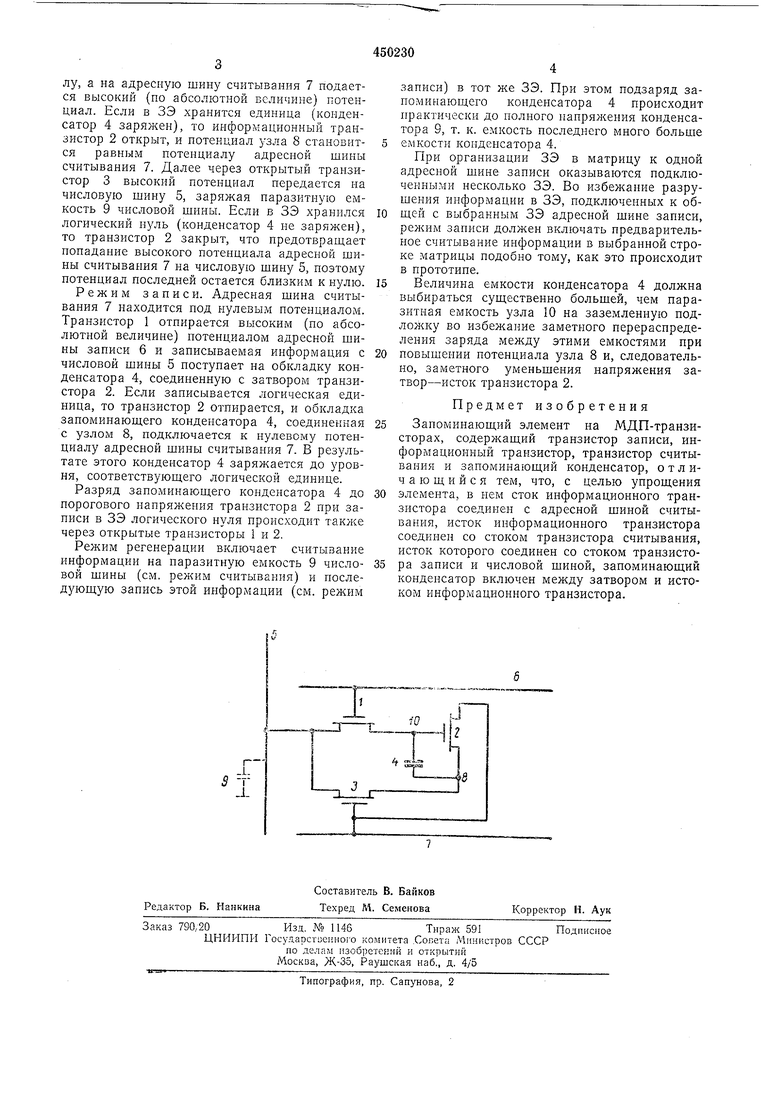

С целью упрощения элемента сток информационного транзистора соединен с адресной шиной считывания, исток его соединен со стоком транзистора считывания, исток которого соединен со стоком транзистора записи и числовой шиной; запоминающий конденсатор включен между затвором и истоком И1 формационного транзистора.

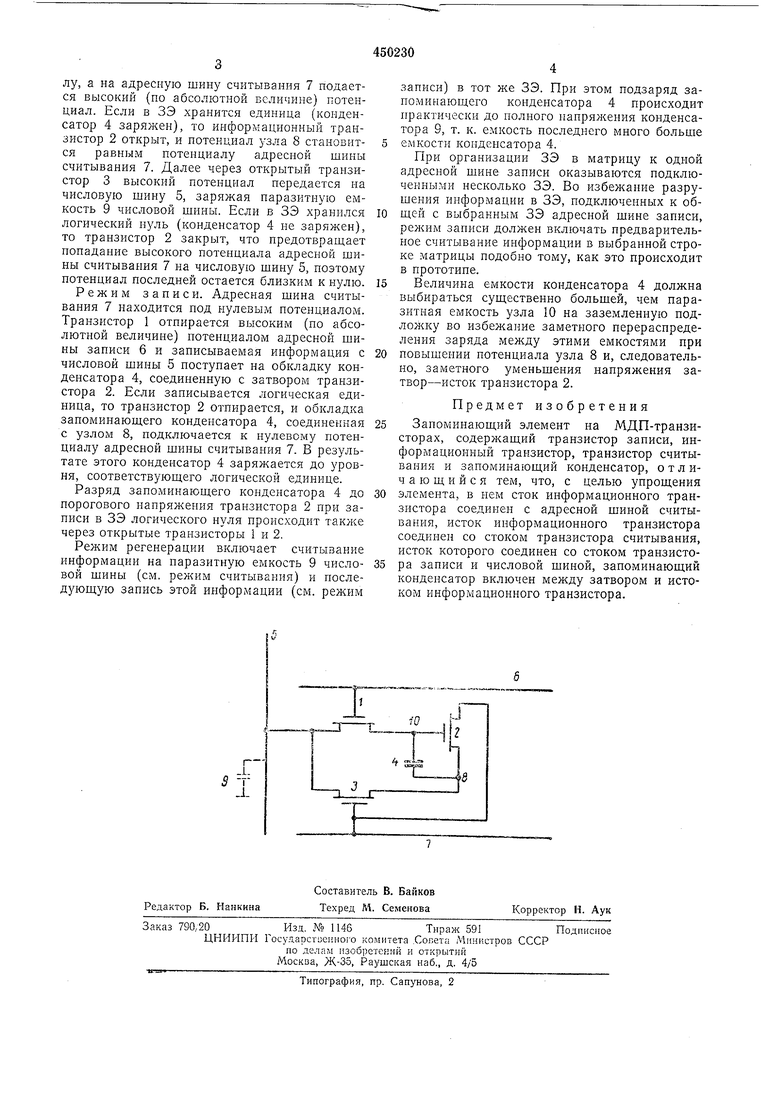

На чертеже представлена схема предлагаемого запоминающего элемента, где 1 - транзистор записи; 2 - информационный транзистор; 3 - транзистор считывания; 4 - запоминающий конденсатор; 5-числовая шина; 6 - адресная щина записи; 7 - адресная шина считывания; 8 - исток информационного транзистора; 9 - паразитная емкость числовой шины.

ОЗУ на предлагаемых ЗЭ может работать в одном из трех режимов: считывание, запись, регенерация.

Перед началом режимов считывания и регенерации числовую шину 5 цсобходи.мо разрядить до нулевого потенциала.

Режим считывания. Адресная шина записи 6 подключается к нулевому потенциалу, а на адресную шину считывания 7 подается высокий (по абсолютной величине) потенциал. Если в ЗЭ хранится единица (конденсатор 4 заряжен), то информационный транзистор 2 открыт, и потенциал узла 8 становится равным потенциалу адресной шины считывания 7. Далее через открытый транзистор 3 высокий потенциал передается на числовую шину 5, заряжая паразитную емкость 9 числовой шины. Если в ЗЭ хранился логический нуль (конденсатор 4 не заряжен), то транзистор 2 закрыт, что нредотврашает попадание высокого потенциала адресной шины считывания 7 на числовую шину 5, поэтому потенциал последней остается близким к нулю.

Режим записи. Адресная шина считывания 7 находится под нулевым потенциалом. Транзистор 1 отпирается высоким (по абсолютной величине) потенциалом адресной шины записи 6 и записываемая информация с числовой шины 5 поступает на обкладку конденсатора 4, соединенную с затвором транзистора 2. Если записывается логическая единица, то транзистор 2 отпирается, и обкладка запоминаюш,его конденсатора 4, соединенная с узлом 8, подключается к нулевому потенциалу адресной шины считывания 7. В результате этого конденсатор 4 заряжается до уровня, соответствующего логической единице.

Разряд запоминающего конденсатора 4 до порогового напряжения транзистора 2 при записи в ЗЭ логического нуля происходит также через открытые транзисторы 1 и 2.

Режим регенерации включает считывание информации на паразитную емкость 9 числовой шины (см. режим считывания) и последующую запись этой информации (см. режим

записи) в тот же ЗЭ. При этом подзаряд запоминающего конденсатора 4 происходит практически до полного напрялсения конденсатора 9, т. к. емкость последнего много больше

емкости конденсатора 4.

При организации ЗЭ в матрицу к одной адресной шине записи оказываются подключенными несколько ЗЭ. Во избежание разрушения информации в ЗЭ, подключенных к общей с выбранным ЗЭ адресной шине записи, режим записи должен включать предварительное считывание информации в выбранной строке матрицы подобно тому, как это происходит в прототипе.

Величина емкости конденсатора 4 должна выбираться существенно большей, чем паразитная емкость узла 10 на заземленную подложку во избежание заметного перераспределения заряда между этими емкостями при

повышении потенциала узла 8 и, следовательно, заметного уменьшения напряжения затвор-исток транзистора 2.

Предмет изобретения

Запоминающий элемент на МДП-транзисторах, содержащий транзистор записи, информационный транзистор, транзистор считывания и запоминающий конденсатор, отличающийся тем, что, с целью упрощения

элемента, в нем сток информационного транзнстора соединен с адресной шиной считывания, исток информационного транзистора соединен со стоком транзистора считывания, исток которого соединен со стоком транзистора записи и числовой шиной, запоминающий конденсатор включен между затвором и истоком информационного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1975 |

|

SU542243A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Элемент памяти | 1984 |

|

SU1274000A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

Авторы

Даты

1974-11-15—Публикация

1973-03-12—Подача