1

Изобретение относится к области вычислительной .

Известны ячейки намяти на МДП-транзисторах, состоящие из статического или динамического заиоминающего элемента (ЗЭ) и выходных МДИ-транзисторрв, служащих для ввода и вывода и 1форма11,ии.

При работе известных ячеек в режиме с неразрущающим считыванием амплитуда входного сигнала выборки выбирается при считывании меньшей, чем при записи информации, - так называемый двухамплитудный режим работы. Двухамилитудный режим работы позволяет получить достаточно высокое быстродействие, однако, ячейки памяти нри таком режиме могут иметь существенные разбросы по параметру L,,,(где

гггrj рээ-мин.

Us „ - минимальное напряжение на заР з-мин.

творах входных транзисторов, при котором происходит разрущение хранимой в ячейке Информации). В связи с этим для обеспечения Надежного неразрушаюндего считывания приходится выбирать напряжение вхсч

/2 и.

считывании U,,

ЧТО в свою

ВХсч - Зраз.„„„.

очередь снижает величину выходного сигнала считывания особенно при небольщой длительности Твхсч входного сигнала выборки. В результате отношение сигнал/номеха на выходных щинах ухудщается.

Кроме того, для обеснечения высокого быстродействия длительность Тпхсц выходного сигнала выборки U Р считывании должна быть достаточно малой. Это требует увелнчения крутизны фронтов сигнала выборки, что в свою очередь увеличивает амплитуду емкостных помех.

Цель изобретения - повышение надежности работы устройства.

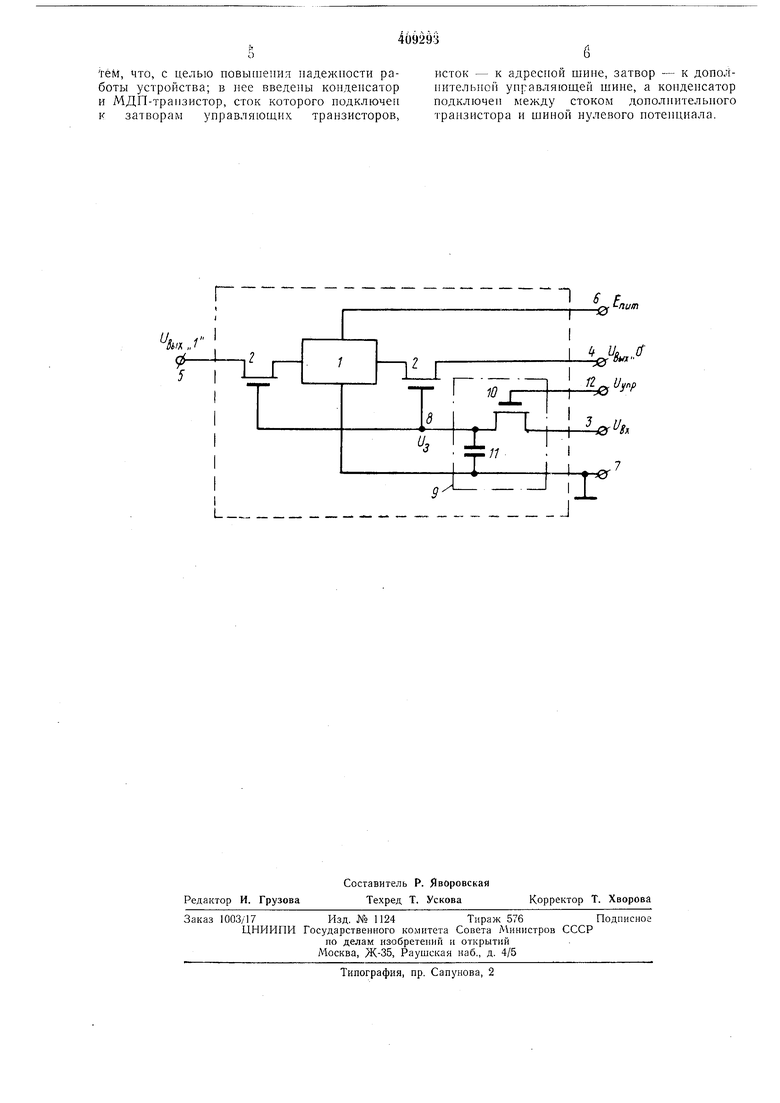

Это достигается тем, что на входе ячейки .между затворами управляюн их траизисторов и шиной выборки включены дополнительные

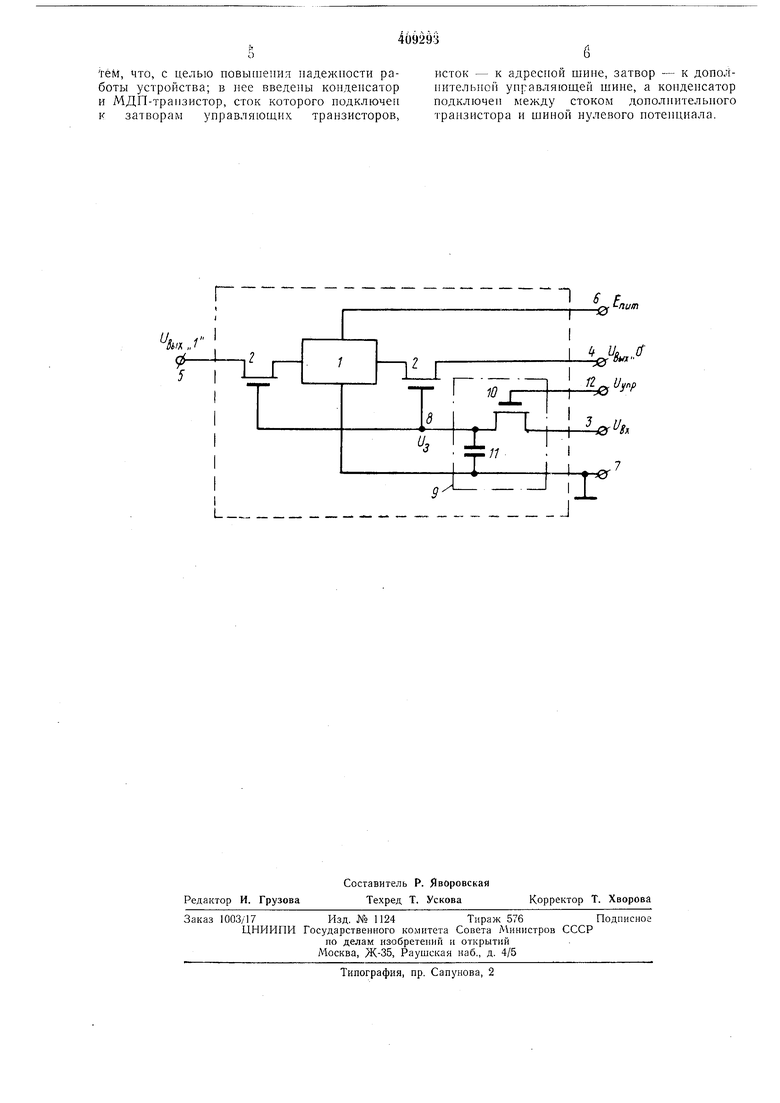

МДИ-транзистор и конденсатор, преобразую1цие форму входного сигнала выборки Lnx из нрямоугольной в экспонен 1.иальну о или линейно нзменяюшуюся. В результате такого преобразования сигнал выборки t/y на затвоpax управляющих транзисторов плавно изменяется как но длительности, так и ио а.милнтуде. Это обстоятельство позволяет плавно подходить к порогу разрушения хранимой в ячейке информации и, таким образом, ослабить влияние разброса заномииающнх эле.ментов но данному параметру. Поскольку крутизна фронта экспоненниального или линейно изменяющегося сигнала выборки меньше, чем нрямоугольного, то величина емкостных номех также меньше, чем в нерво.м случае. Схема ячейки памяти показана на чертеже, где 1 - запоминающий элемент; 2 - управляющие транзисторы; 3 - адресная щина; 4 и 5 - информационпые щины; 6 - щииа источника питания; 7 - щина нулевого потенциала;8 - затворы унравляюахих транзнсторов; 9 - четырехнолюсник; 10 - донолнительпый МПД-транзистор; 11 - дополнительный конденсатор; 12 - дополнительная щина управления. Входной сигнал выборки ьхсч подается на адресную щину 3 и формируется четырехполюсником 9. Сформированный сигнал выборки постунает на затворы транзнсторов 2 и открывает их. В зависимости от храняп1,ейся в ячейке информации считанный сигнал (/3 появляется на щине 5 или 4. Для обеснечения неразрущающего считывания режим работы дополнительного транзистора 10 выбирается, исходя из условия (,„„„,, где t/зсч (О - напряжение на затворах управляющих транзисторов при считывапии;длительность сигнала считывания на затворах управляющих транзисторов, отсчитываемая по уровню t/o; Uo - пороговое напряжение управляющих транзисторов; минимальная площадь, нри которой происходит разрущение хранящейся информации при условии эо„„ минимальное постояпное напряжение на затворах управляющих транзисторов, при котором происходит разрущение информацииВ УСЛОВИИ (1) заложена также дополнительная устойчивость предлагаемой системы выборки против влияния разбросов параметров ячейки на характеристики хранения информации. Для того, чтобы задний фронт сигнала на затворах управляющих транзисторов 7зсч ехр не был растянут после окончапия входного сигнала выборки (вхсч за счет больщого сопротивления МДП-транзистора 10, на затвор этого транзистора (щина 12) подается импульс управляющего напряжения L/ynp длительностью Тд;. н амплитудой бд;,, дополнительно открывающий транзистор 10, обеспечивая тем самым необходимый задний фронт сигнала И . Это позволяет сохрапить быстродействие ячейки практически таким же, что и у известного в режиме двухамплитудной выборки. Так как передний и задний фронты сигнала f/зсч ехр менее крутые, чем фронты входного сигнала выборки U вхсч то помехи, появляющиеся на выходных щинах 4 и 5 по передпему и заднему фронтам за счет паразитных емкостных связей между этими Щинами и затворами выходных транзисторов 2, оказываются меньше, чем в случае нрименения известной ячейки памяти. Для обеспечения надежной записи информации необходимо вынолнить условие зап . з,,,,,,Т,,(2) taan - длительность сигнала записи на затворах выходных транзисторов, отсчитываемая по уровню и о; минимальная плонхадь, при коЗо макс Эо торойпроисходит надежная запись информации в МДП-ЭП условии Для выполнения условия (2) при записи на управляющую щину 12 подается импульс управляющего нанряжения заниси длительностью Тдззп и амплитудой . В результате этого дополнительный транзистор 10 переходит в крутую область своей выходной характеристики, обеспечивая тем самым нужный входной импеданс формирующего четырехполюсника 9. Поэтому сигнал . в режиме записи информации практически не отличается от входного сигнала выборки вхзап Таким образом, осуществляется надежная запись информации в ячейку памяти. При записи «1 или «О па щины 5 или 4 поступает соответствующий импульс записи «1 или записи «О. При необходимости предлагаемая ячейка может работать в обычном режиме с двухамплитудпой выборкой. Для этого следует лищь подать соответствующее постоянное нанряжение на управляющую щину 12, обеспечивая тем самым нужный входной импеданс четырехполюсника как при записи, так и при считывании. Таким образом предлагаемая ячейка памяти по сравнению с ранее известными имеет более щирокую область применения, меиьщую величину помех на выходных щинах считывания - записи, позволяет уменьщить влияние разброса параметров и пестабильности амплитуды входного сигнала выборки на характеристики хранения информации. Предмет изобретения Ячейка памяти, содержащая запоминающий элемент, выходы которого соединены со стоками управляющих МДП-транзисторов, истоки которых подключены к информационным щинам, затворы объединены и подключены к адресной щине, отличающаяся

Тем, что, с целью повьинеиил надежности работы устройства; в нее введены конденсатор и МДП-транзистор, сток которого подключен к затворам управляющих транзисторов.

исток - к адресной шине, затвор - к дополнительной унравляющей шине, а конденсатор подключен между стоком дополнительного транзистора и шиной нулевого нотенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Динамическая ячейка памяти | 1974 |

|

SU488258A1 |

| Формирователь импульсов записи | 1986 |

|

SU1381594A2 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1987 |

|

SU1436735A3 |

Г

А/;(„/

L

пит

Даты

1973-01-01—Публикация