1

Изобретение относится к области вычислительной техники и, в частности, может быть использовано ири проектировании устройств оперативной памяти вычислительных машин.

Известно устройство для обмена информацией между оперативной памятью и процессором, содержащее регистр адреса, блок управления обменом, подключенный к буферным регистрам памяти, буферпые регистры процессора.

Недостатком известного устройства является невысокое быстродействие.

Описываемое устройство отличается от известного тем, что оно содержит блок сравнения, регистр предыдущего адреса и блок коммутации, входы и выходы которого подключены к соответствующим выходам и входам буферных регистров, а управляющие входы соединены с выходом блока управления обменом, к одному из входов которого подключен выход блока сравнения, первый вход которого соединен с выходом регистра адреса и одним из входов регистра предыдущего адреса, второй вход - с выходом регистра предыдущего адреса, другой вход которого соединен с выходом блока управления обменом.

Эти отличия позволяют повысить быстродействие устройства.

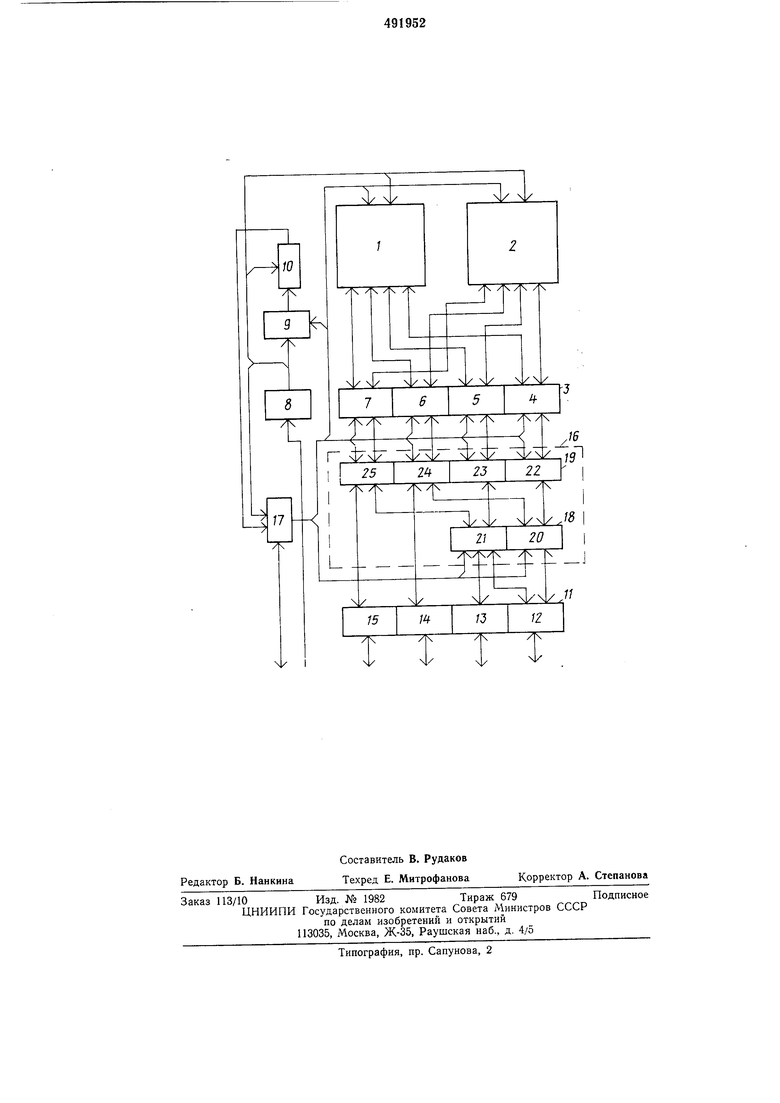

На чертеже изображена структурная схема предложенного устройства, например, для числа символов /п 4.

Устройство содержит модули памяти 1 и 2,

каждый из которых предназначен для хранения информации, обрабатываемой вычислительной машиной, и команд (или микрокоманд), под управлением которых происходит обработка информации, по тп двоичных

разрядов в одной физической ячейке памяти, буфер памяти 3, предназначенный для приема данных, подлежащих записи в модуль памяти 1 или 2, а также для приема считанного кода, состоящий из буферных регистров памяти (с первого 4 по четвертый 7) (все регистры /г-разрядные), регистр адреса 8, нредиазначенный для указания адреса запрашиваемого или заиисываемого слова, регистр 9 предыдущего адреса, предназначенный для хранения адреса физической ячейки памяти, к которой произошло предыдущее обращение, блок сравнения 10, предназначенный для сравнения содерлсимого регистра 9 предыдущего адреса с содерл имым соответствующих полей

регистра адреса 8, буфер процессора П. предназначенный для хранения слова, подлежащего записи в модуль памяти 1 или 2, а также для приема запрошенного слова, состояпшй из буферных регистров 11 процессора (с перБОго 12 по четвертый 15) (все регистры и-разР51ДНЫ-:-), блок коммутации 16, предназначенiiHfi для передачи слова, подлежащего записи в палять, 3 буфера процессора 11 в некоторые из бус{)ерцых регистров памяти 4-7 или во все буфер ые регпстры памяти 4-7, а такж:: для передачи запрошенного слова, храняп;,сгося в некоторых из буферных регистров лар,:ятя 4--7 в буфер процессора 11, блок 17 упраБлешя об.меиом, предназначенный для -правлеппя обменом информацией между буфером процессора 11 и модулями памяти 1 н 2 в соответствии с адресом запрашиваемого HJiii записываемого слова и кодом операции обращепия к памяти.

Ка чертеже приведена одна из возможных структурпых схем блока коммутации 16, в соответствии с которой ои состоит из первой

18и второй 19 ступеней коммутации, предназначенных для совместного переключения кодовых шин, связывающих буфер памяти 3 и буа)ер процессора И.

В общем случае количество ступеней коммутации может быть произвольным. Блок коммутации 16, состоящий из k ступеней комл1утацин, обеспечивает передачу слов, длина когооых равна 2л-двоичных разрядов, где ,2,....,k.

В состав первой ступени коммутации 18 входят первый 20 и второй 21 блоки переключения, в состав второй ступени коммутации

19- первый 22, второй 23, третий 24 и четвертый 25 блоки переключения. Количество блоков переключения в любой ступени коммутации равно 2, где f - номер ступени коммутации.

Блоки переключения 20-25 предназначены для выполнения следующих функций в режиме записи.

Блок переключения 20 служит для подключения выходов первого буферного регистра 12 по входам первого 22 и третьего 24 блоков переключенпя второй ступени коммутации 19. Блок переключения 21 предназначен для подключения выходов первого 12 или второго буферного регистра 13 процессора ко входам второго и четвертого блоков переключения 23 и 25 второй ступени коммутации 19.

Блок переключения 22 служит для подключения выходов первого блока переключения

20первой ступени коммутации 18 ко входам первого буферного регистра памяти. Блок переключения 23 используется для подключения выходов второго блока переключения 21 первой ступени коммутации 18 ко входам второго буферного регистра памяти 5. Блок переключения 24 предназначен для подключения выходов третьего буферного регистра 14 процессора или первого блока переключения 20 первой ступени коммутации 18 ко входам третьего буферного регистра памяти 6. Блок переключения 25 служит для подключения выходов четвертого буферного регистра 15 процессора или второго блока переключения

21 первой ступени коммутации 18 ко входам четвертого буфериого регистра памяти 7.

В режиме чтения из памяти блоки переключения 20-25 служат для выполнения следующих функций:

блок переключения 22 - для подключения выходов первого буферного регистра памяти 4 ко входам первого блока переключения 20 первой ступени коммутации 18; блок переключения 23-для подключения выходов второго буферного регистра памяти 5 ко входам второго блока переключения 21 первой ступени коммутации 18; блок переключения 24 - для подключения выходов третьего буферного регистра памяти 6 ко входам третьего буферного регистра 14 процессора или первого блока переключения 20 первой ступени коммутации 18; блок переключения 25- для подключения выходов четвертого буферного регистра памяти 7 ко входам четвертого буферного регистра 15 процессора или второго блока переключения 21 первой ступени коммутации 18; блок переключения 20 - для подключения выходов первого блока переключения 22 или третьего блока переключения 24 второй ступени коммутации 19 ко входам первого буферного регистра 12 процессора; блок переключения 21 --для подключения выходов второго блока переключения 23 или

четвертого блока переключения 25 второй ступени коммутации 19 ко входам первого 12 или второго буферного регистра 13 процессора.

Входы и выходы блока коммутации 16 подключены к соответствующим выходам и входам буферных регистров 4-7 и 12-15, а управляющие входы блока 16 соединены с выходом блока 17 управления обменом, к одному из входов которого подключен выход

блока сравнения 10, первый вход которого соединен с выходом регистра адреса 8 и одним из входов регистра 9 предыдущего адреса, второй вход - с выходом регистра 9, другой вход которого соединен с выходом блока

17 управления обменом.

Остальные связи между блоками устройства показаны на чертеже.

Минимальной единицей информации, адресуемой индивидуально, является слово длиной п двоичных разрядов. Физической ячейке модулей памяти 1 и 2 соответствует четыре различных адреса, отличающихся двумя младшими разрядами. Условимся, что коду 00 этих разрядов соответствуют разряды физических ячеек памяти, связанные с буферным регистром памяти 4, коду 01 - разряды, связанные с буферным регистром памяти 5 и т. д. Слово длиной 2п двоичных разрядов размещается в первой или второй половине

физической ячейки памяти и его адрес, представленный в двоичном коде, оканчивается по крайней мере одним нулем. Слово длиной 4п двоичных разрядов занимает одну физическую ячейку памяти и имеет адрес, оканчивающийся по крайней мере двумя нулями. Указание

длины слова, как правило, содержится в коде операции обращения к памяти и поступает в устройство оперативной памяти из процессора как при чтении, так и при записи. Исключение составляют операции чтения в тех случаях, когда процессор не может заранее указать длину запрашиваемого слова.

Номер модуля памяти, к которому производится обращение, указывается в соответствующем поле адреса.

Устройство работает следующим образом.

Для записи в память слова длиной п двоичных разрядов записываемое слово должно находиться в первом буферном регистре 12 процессора, а его адрес - в регистре адреса 8. В случае, если младший двоичный разряд адреса равен нулю, производится выдача записываемого слова на выходы первого блока переключения 20 первой ступени коммутации 18, если равен единице-на выходы второго блока переключения 21 первой ступени коммутации 18; аналогично в соответствии со значением следующего двоичного разряда адреса записываемое слово поступает на чыходы одного из блоков переключения второй ступени коммутации 19 и принимается в требуемый буферный регистр памяти 4, 5, 6 или 7, после чего происходит его запись в модуль памяти 1 или 2, при этом остальные три «-разрядных символа, хранящиеся в физической ячейке памяти, к которой произошло обращение, остаются без изменения, т. е. в этих частях ячейки производится чтение, и считанные символы принимаются в соответствующие буферные регистры памяти. Эти символы, как и вновь записанный символ, сохраняются в буфере памяти 3 до момента очередного запуска модуля памяти 1 или 2.

Запись в память двухсимвольных слов производится следующим образом. Записываемое слово помещается в первый и второй буферные регистры 12, 13 процессора и передается на выходы первой ступени коммутации 18 без изменения. Если второй младший двоичный разряд адреса равен нулю, записываемое слово передается посредством первого и второго блоков переключения 22, 23 второй ступени коммутации 19 в первый и второй буферные регистры памяти 4, 5, если равен единице - посредством третьего и четвертого блоков переключения 24, 25 второй ступени коммутации 19 в третий и четвертый буферные регистры памяти 6, 7, после чего происходит его запись в модуль памяти I или 2.

Для записи в память слова максимальной длины записываемое слово помещается в буфер процессора 11, откуда без изменения передается в буфер памяти 3 с помощью блока коммутации 16.

Каждая запись в модуль памяти 1 или 2 сопровождается переписью адреса физической ячейки памяти, в которую производится запись, в регистр 9 предыдущего адреса.

Таким образом, в результате любой из описанных операций записи слово, переданное

из процессора, записывается в модуль памяти 1 или 2; кроме этого, адрес физической ячейки памяти, в которую произведена запись, передается в регистр 9 предыдущего адреса, а содержимое этой ячейки устанавливается в буфер памяти 3.

Выполнение алгоритма обмена словом переменной длины обеспечивает блок 17 ynjiaoления обменом: необходилтые переключеиия з блоке коммутации 16, запуск модуля памяти 1 или 2, прием в буфер памяти 3 записываемых символов с выходов блока коммутации

16 и остальных символов с выходов МОДУЛЯ

памяти 1 или 2, перепись адреса физической ячейки памяти в регистр 9 предыду Г1его адреса осуществляются под управлением С1 Г5а;-оз, вырабатываемых этим блоком. По окончании цикла обращения к памяти блок 17 управления обменом посылает в процессор сигпал. указывающий, что возможно следуюнтее обращение к памяти.

Операции чтения из оперативной памяти производятся путем обращения к модулю памяти 1 или 2 только в случае, если запрошенное слово отсутствует в буфере па,;ятн 3. Поэтому любая операция чтения начинается с анализа сигнала сравнения, вырабатываемого блоком сравнения 10. Еслт сигнал сравнения отсутствует, производится обращение к модулю памяти 1 или 2 по адресу, указанному в регистре адреса 8, после чего адрес опрашиваемой ячейки памяти передается в регистр 9 предыдущего адреса. Через определенное время, необходимое для приема считанного кода в буфер памяти 3, блок 17 управления обменом вырабатывает сигналы управления блоком коммутации 16, необходимые для передачи запрошенного слова из буфера памяти 3 в буфер процессора 11. После завершения цикла обращения к модулю памяти 1 или 2 в процессор передается сигнал, указывающий, что возможно следующее обращение к памяти.

Обращение к модулю памяти 1 или 2 не производится, если блок сравнения 10 вырабатывает сигнал сравнения. В этом случае блок 17 управления обл1еном сразу после приема кода операции чтения вырабатывает сигналы управления, обеспечивающие передаму запрошенного слова посредством блока коммутации 16 из буфера памяти 3 в буфер процессора 11, а затем снгнализпрует, что устройство готово к обмену следлчопцтм словом.

В случае, когда процессор указывает длнну запрашиваемого слова, связь между буфером памяти 3 и буфером процессора 11 организуется следующим образом.

Слова максимальной длины передаются в буфер процессора И посредством блока коммутации 16 без изменения. Двухсимвольные слова передаются на входы первого н второго блоков переключепня 20, 21 первой ступени коммутации 18 из первого н второго буферных регистров памяти 4, 5 посредством первого и второго блоков переключения 22,

7

23 второй ступени коммутации 19, если второй младший двоичный разряд адреса равен нулю, и из третьего и четвертого буферных регистров памяти 6, 7 посредством третьего и четвертого блоков переключения 24, 25 второй ступени коммутации 19, если этот разряд равен единице. Первая ступень коммутации 18 передает двухсимвольное слово в первый и второй буферные регистры 12, 13 процессора без изменения. Выделение односимвольного слова в процессе его передачи в буфер процессора 11 происходит в два этапа: в соответствии со значением второго младшего двоичного разряда адреса первая либо вторая пара символов, хранящихся в буфере памяти 3, посредством второй ступени коммутации 19 передается на входы первой ступени коммутации 18, а затем в соответствии со значением младшего двоичного разряда адреса требуемый символ поступает в первый буферный регистр 12 процессора.

Чтение из оперативной памяти может также выполняться без указания длины запрашиваемого слова, например, при выборке команды (или микрокоманды). Пусть в вычислительной машине используются двухсимвольные, четырехсимвольные, шестисимвольпые п восьмисимвольные команды, размешаемые в памяти следующим образом: двухсимвольная команда располагается в первой или второй половине физической ячейки памяти, четырехсимвольная занимает целую ячейку, шестисимвольпая-одну ячейку и первую половину второй, восьмисимвольная - две физические ячейки памяти. Адрес команды указывает ее первый символ, являющийся кодом операции. Двоичная запись адреса двухсимвольной команды оканчивается по крайней мере одпим нулем, любой другой команды - по крайней мере двумя нулями.

Выборка команды (микрокоманды) из оперативной памяти производится следующим образом. В соответствии с адресом, установленным в регистр адреса 8, производится считывание содержимого требуемой физической ячейки в буфер памяти 3. Поскольку в блок управления обменом не поступило указания длины запрашиваемого слова, исходной информацией для управления передачей из буфера памяти 3 в буфер процессора 11 является только адрес команды. Если адрес оканчивается двумя нулями, содержимое буфера памяти 3 без изменения передается в буфер процессора 11, если адрес оканчивается одним нулем, содержимое третьего и четвертого буферных регистров памяти 6 и 7 передается в первый и второй буферный регистры процессора 12 и 13 соответственно, в результате

код операции всегда оказывается в первом буферном регистре процессора. Далее происходит передача содержимого буфера процессора в первую половину регистра команд (микрокоманд) устройства управления вычислительной машины, где происходит определение длины команды по коду операции. Если команда двухсимвольная, третий и четвертый символы, переданные в регистр команд, не учитываются, и вычислительная

машина приступает к выполнению команды. Если команда четырехсимвольная, используются все четыре переданные символа. В случае щестисимвольной команды производится повторное обращение к устройству оперативной

памяти, передача считанного кода из буфера процессора 11 во вторую половину регистра команд и начинается ее выполнение, причем два последних символа не учитываются. Аналогично происходит выборка восьмисимвольной команды.

Описанный алгоритм выборки слов без указания процессором их длины может использоваться в вычислительной машине также при чтении данных, представляемых, например,

словами произвольной длины, при этом количество символов, используемых в слове, может указываться первым символом слова.

Формула изобретения

Устройство для обмена информацией между оперативной памятью и процессором, содержащее регистр адреса, блок управления обменом, подключенный к буферным регистрам памяти, буферные регистры процессора,

отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит блок сравнения, регистр предыдущего адреса и блок коммутации, входы и выходы которого подключены к соответствующим выходам и входам буферных регистров, а управляющие входы соединены с выходом блока управления обменом, к одному из входов которого подключен выход блока сравнения, первый вход которого соединен с выходом

регистра адреса и одним из входов регистра предыдущего адреса, второй вход - с выходом регистра предыдущего адреса, другой вход которого соединен с выходом блока управления обменом.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ВХОЖДЕНИЯ ОБРАЗЦА | 2002 |

|

RU2223539C2 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор | 1976 |

|

SU670935A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

Авторы

Даты

1975-11-15—Публикация

1974-01-18—Подача