Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке системы ввода-вывода ЭВМ, в частно сти для управления работой аппаратуры обрймл ния буфера данных в селекторном канале.

Цель изббретенй.я - повышение скорости; пер e,naii-H данных при работе с цепочкой данных. | ,

Поставленная/цель достигается те что I во время смены УСК при работе с { епоЧкой данных канал одновременно может работать с двумя УСК. Одно УСК используется для работы интер- фейсом, а другое для работы с оперативной памятью.- , .

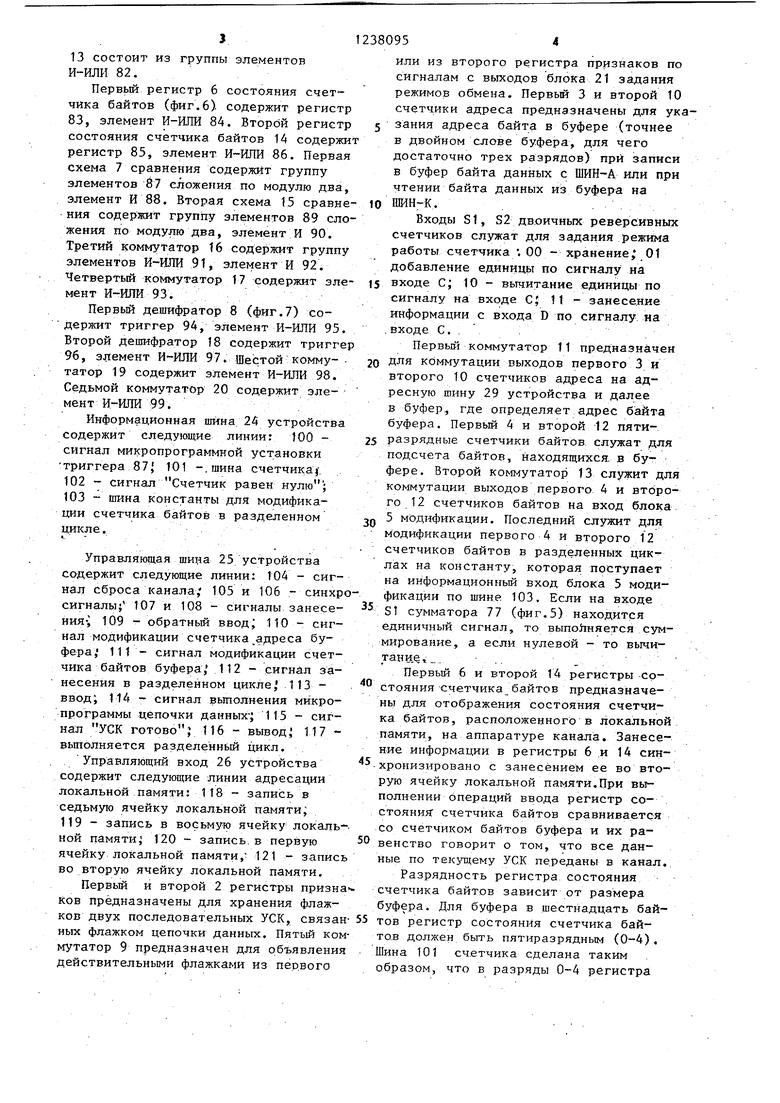

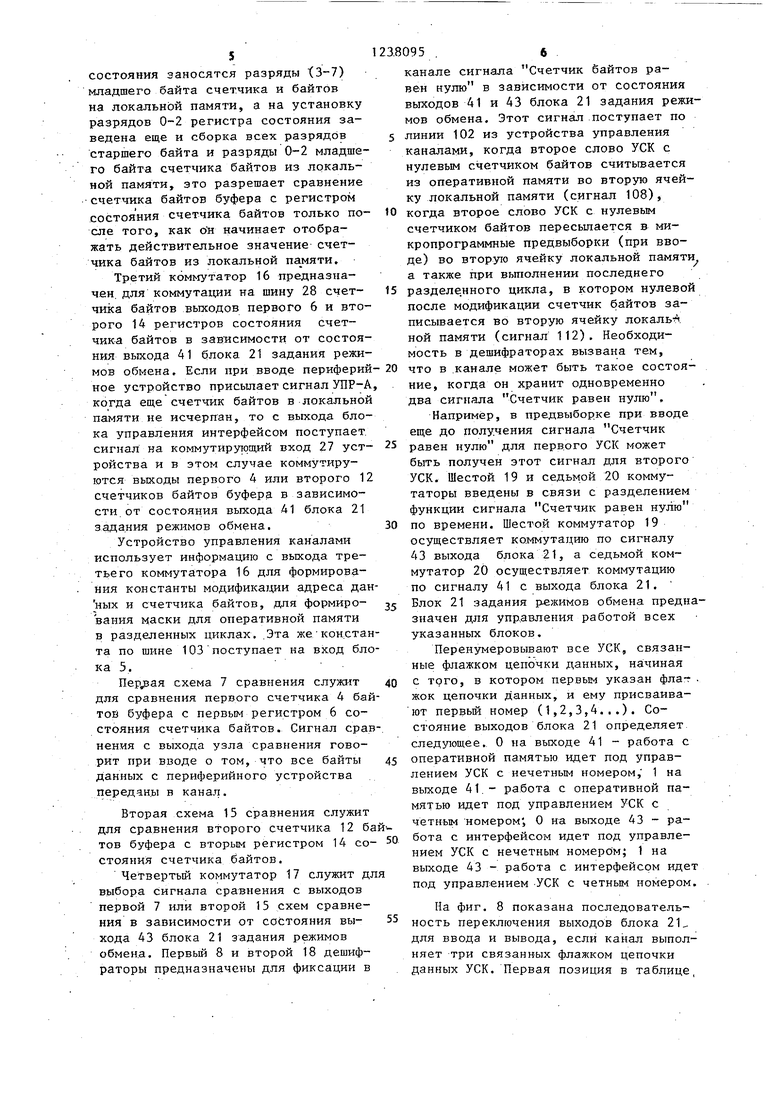

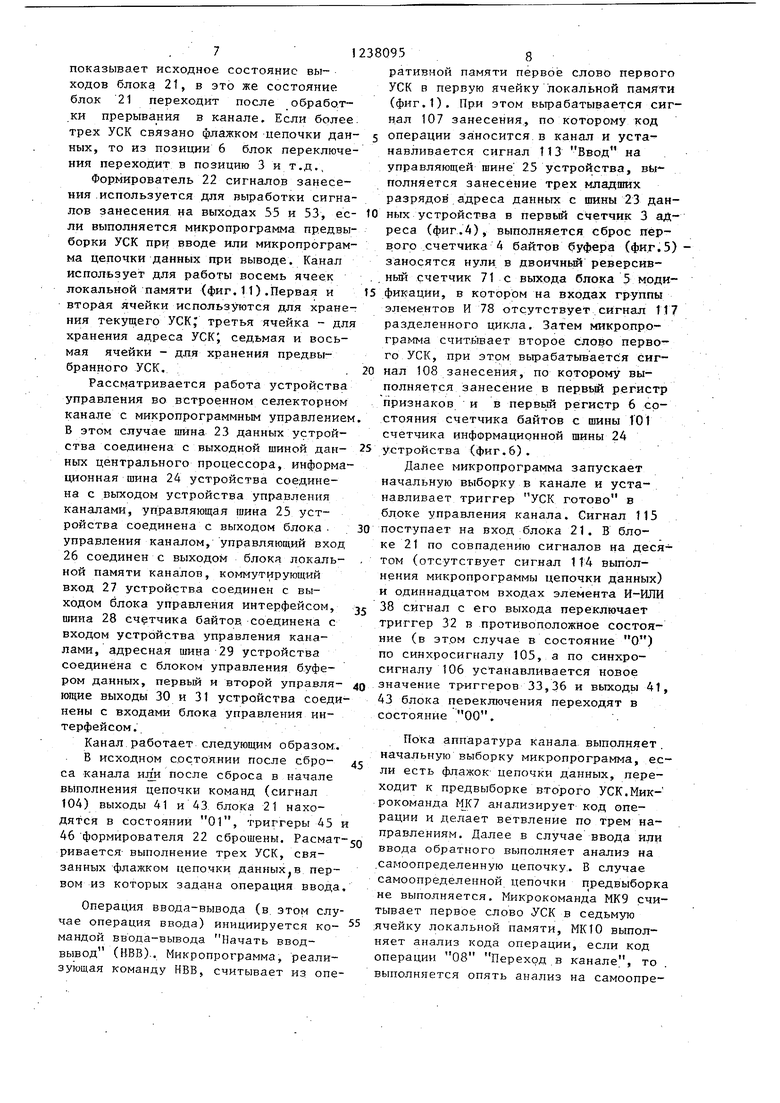

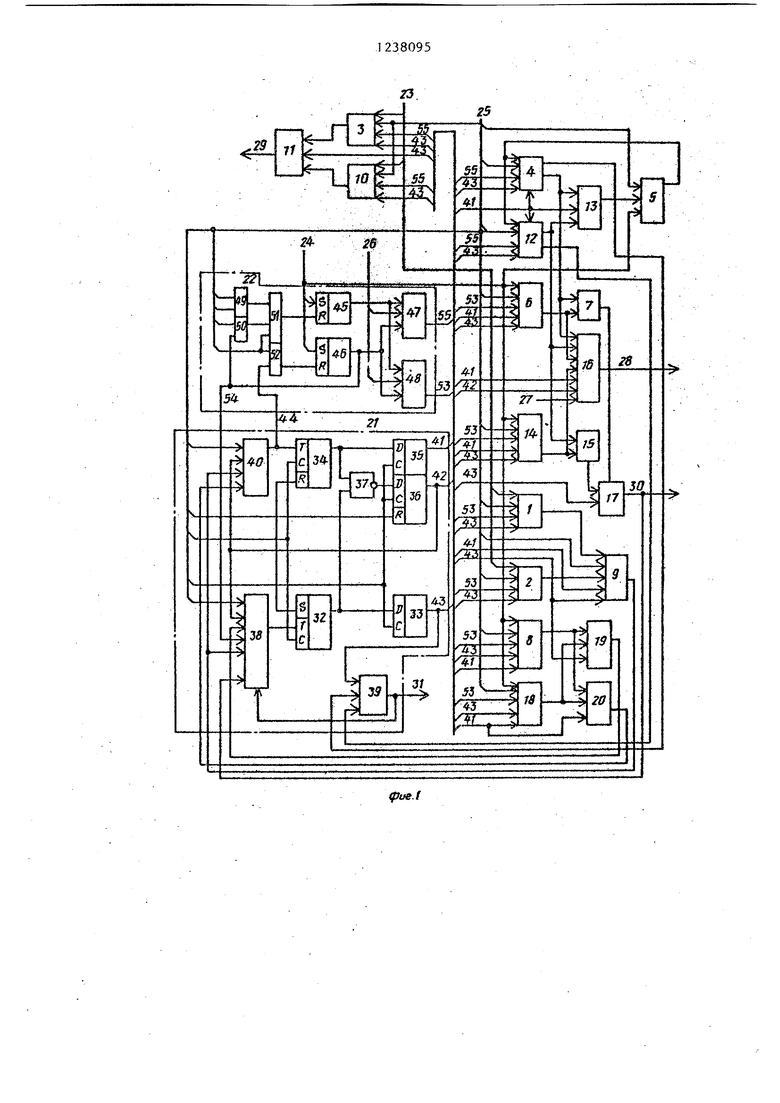

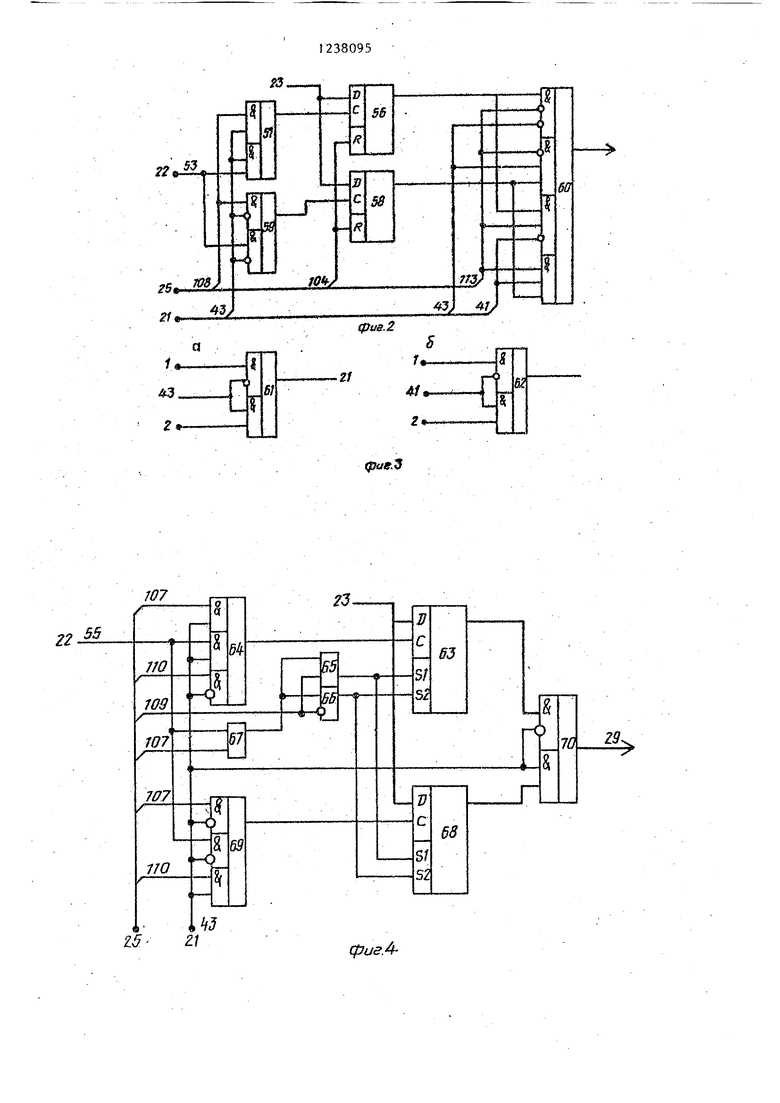

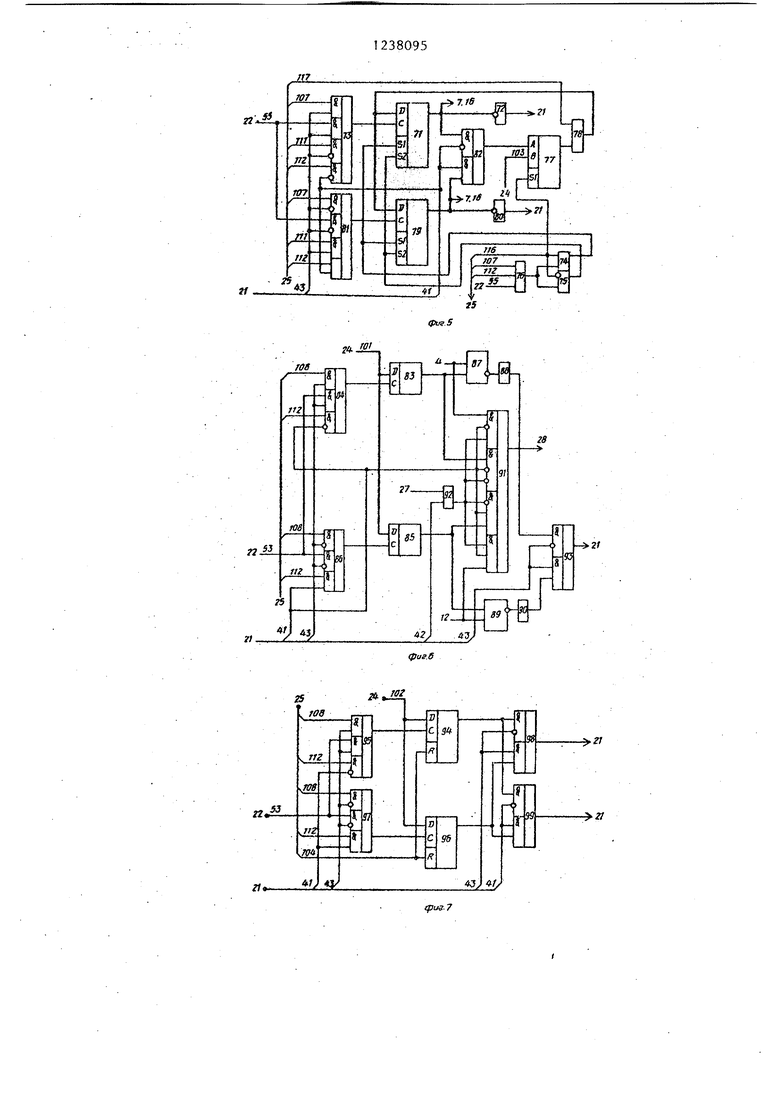

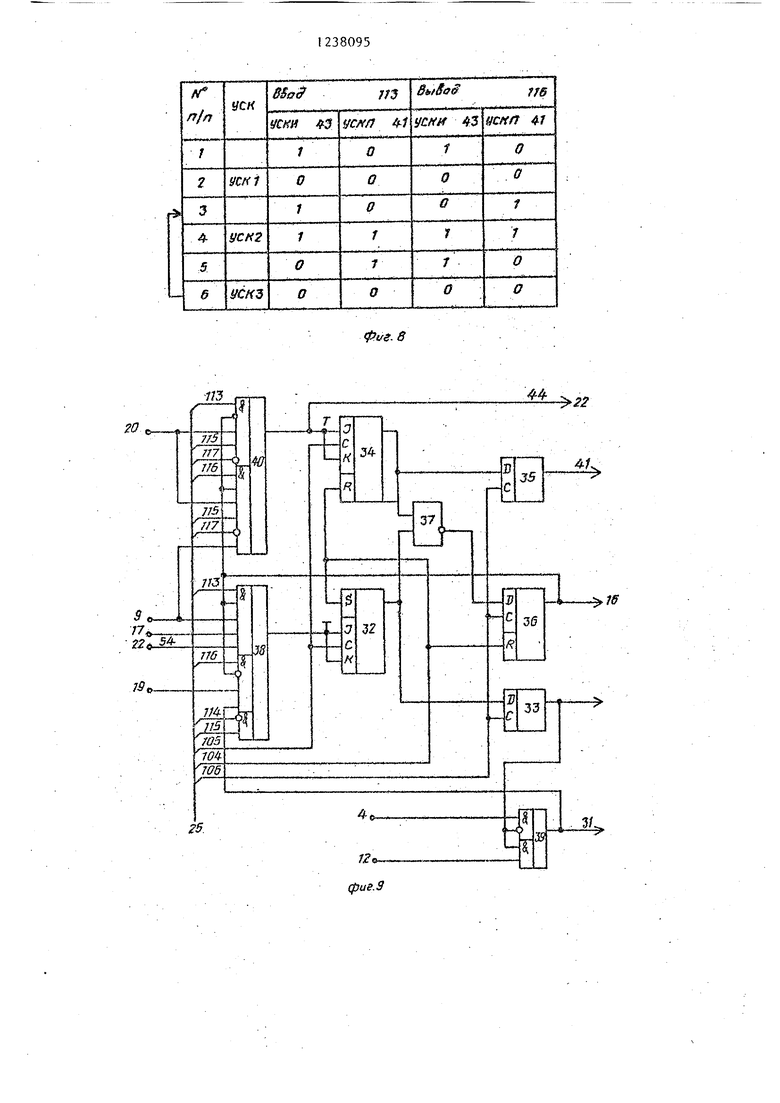

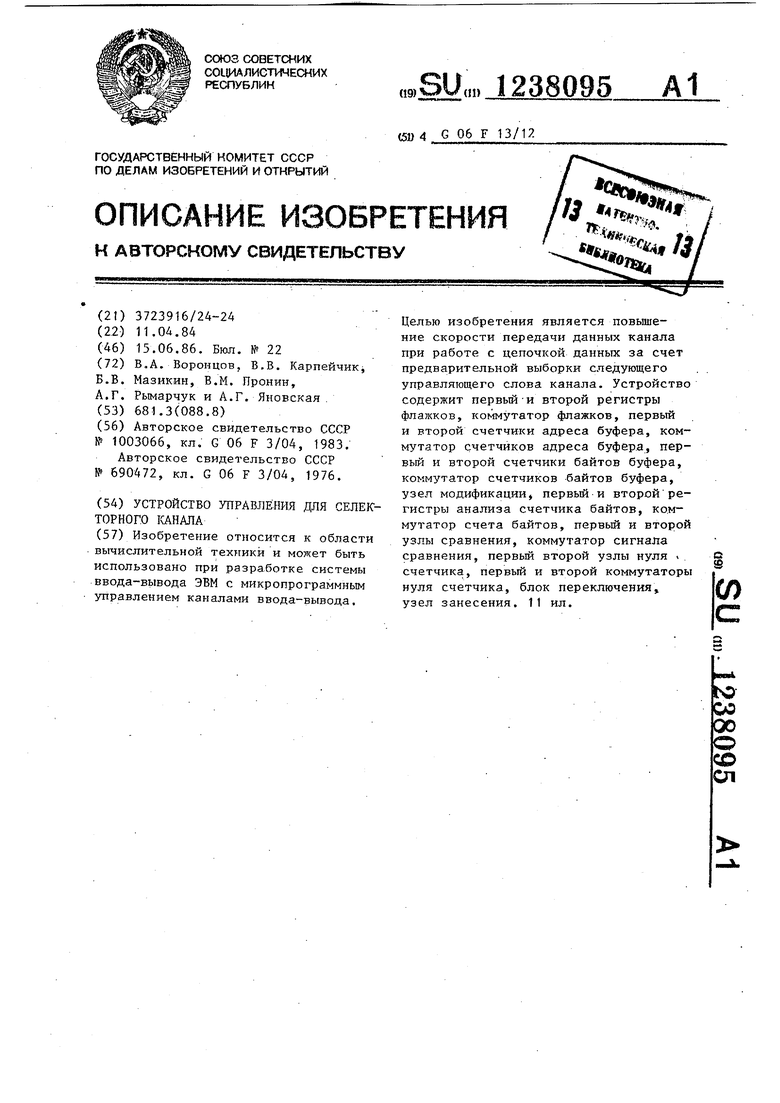

На фиг. 1 представлена структурная схема устройства управления для селекторного канала; на фиг. 2 - функдаональная схема первого регистра признаков, второго регистра признаков, пятого коммутатора {по-. казана коммутация флажка программно управляе юго прерывания), на фиг.З коммутация флажков цепочки команд, цепочки данных и подавления индикации неверной длины, а также коммута ция флажков блокировки записи в память и флажка косвенной адресации; на фиг. 4 - .функциональная схема дервого счетчика .адреса,, второго сччика адреса, первого коммутатора; на фиг. 5 - функциональная схема первого счетчика байтов, блока модифика- ции, второго .счетчика байтов, второго коммутатора) на фиг. б - первый регистр состояния счетчика байтов, второй регистр состояния счетчика байтов, первая схема сравнения, вто- .рая схема сравнения, третий и чет- вертьм коммутаторы ; на фиг. 7 - первЬм дешифратор, второй дешифратор шестой и седьмой кoммyтaтopыJ на фиг. 8 - таблица переключения выхо- дон блока задания режимов обмена; на фиг. 9 - блок задания режимов обмена; на фиг. 10 - формирователь сигналов занесения, на фиг. 11 - распределение локальной памяти ка .нала.

Устройство управления (фиг,1) содержит первый регистр 1 признаков, второй регистр 2 признаков, первый счетчик 3 адреса, первый счетчик 4 байтов, блок 5 модификации, первый регистр 6 состояния счетчика байтов, первую схему 7 сравнения, первый дешифратор 8, пятый коммутатор 9 флажков, второй счетчик 10 адреса, первый коммутатор 11, второй счетчик 12 байтов, второй коммутатор13, второй регистр 14 состояния счетчика байтов, вторую схему 15 сравнения, третий коммутатор 16, четвер- тьм коммутатор 17, второй дешифратор 18, шестой коммутатор 19, седьмой коммутатор 20, блок 21 задания режимов обмена, формирователь 22 сигналов занесения, шину 23 данных устройства, информационную шину 24 устройства, управляющую шину 25 устройства, управляющий вход 26 устройства коммутирующий вход 27 устройства, шину 28 счетчика .байтов, адресную шину 29 устройства, первый управляющий выход 30 устройства, второй управляющий выход 31 устройства.

Блок 21 задания режимов обмена (фиг.9) содержит триггеры 32-36,элемент 37 сложения по модулю два, элементы И-ИЛИ 38-40, первый режимный выход .41, третий режимньш выход 42, второй режимный выход 43,разрешающий выход 44,

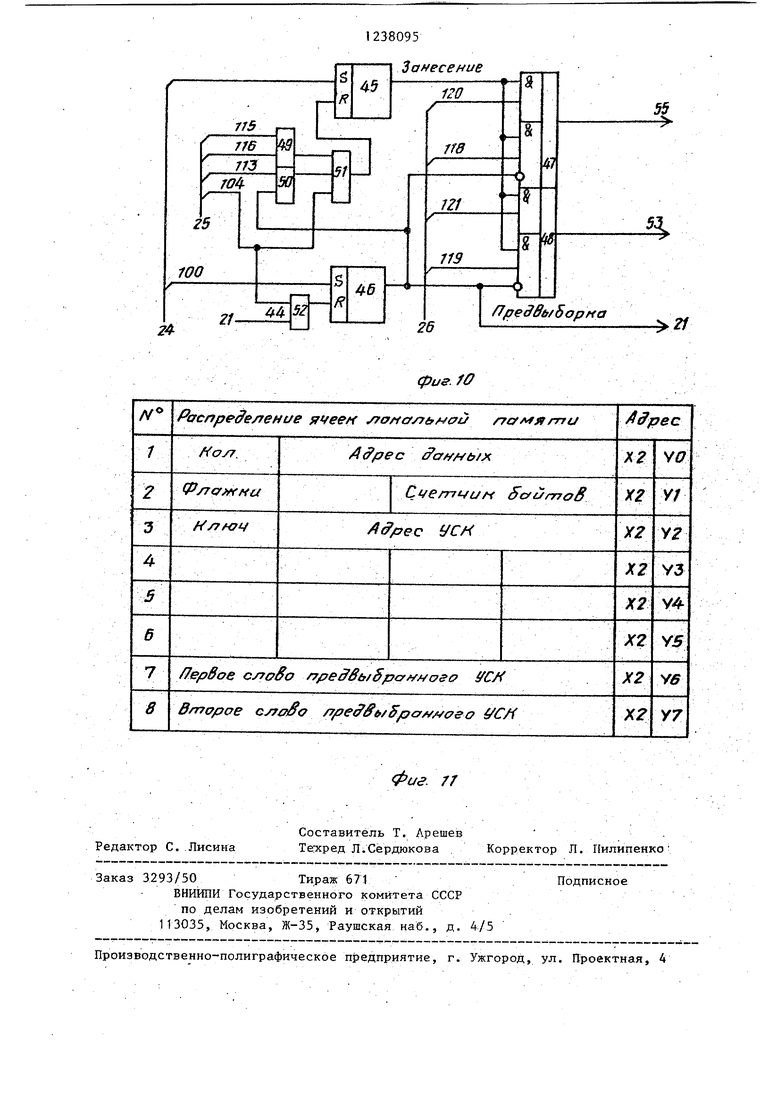

Формирователь. 22 сигналов занесения (фиг.10) содерткит триггеры 45 и 46, элементы И-ИЛИ 47 и 48, элементы И 49 и 50, э.лементы ИЛИ 51 и 52, второй выход 53 формирователя, третий выход 54 формирователя, первый выход 55 формирователя.

Первьй регистр 1 признаков (фиг.2) содержит группу триггеров 56 и элемент И-ИЛИ 57. Второй регистр 2 признаков содержит гр.уппу триггеров 58 и элемент И-ИЛИ 59. Пятьй коммутатор 9 содержит элемент И-ИЛИ 60, три элемента И-ИЛИ 61 (фиг.За) и два элемента И-ИЛИ 62 (фиг.36).

Первый счетчик 3 адреса (фиг.4) содержит реверсивньй двоичный счетчик 63, элемент И-ИЛИ 64,. элемент 1ШИ 65-67. Второй счетчик 10 адреса содержит реверсивньй двоичньй счетчик 68 и элемент И-ИЛИ 69..Первйш коммутатор 11 состоит из группы элементов И-ИЛИ 70. Первьш счетчик 4 байтов (фиг.5) содержит реверсивный двоичный счетчик 71, элемент И 72,. элемент И-ИЛИ 73, элементы ИЛИ 74-76. Блок модификации содержит сумматор 77, группу элементов И 78. Второй счетчик 12 байтов содержит реверсивньй двоичньй счетчик 79, элемент И 80 элемент И-ИЛИ 81. Второй коммутатор

13 состоит из группы элементов И-ИЛИ 82.

Первый регистр 6 состояния счетчика байтов (фиг.6). содержит регистр 83, элемент И-ИЛИ 84. Второй регистр состояния счетчика байтов 14 содержит регистр 85, элемент И-ИЛИ 86. Первая схема 7 сравнения содержит группу элементов 87 сложения по модулю два, элемент И 88. Вторая схема 15 сравнения содержит группу элементов 89 сложения по модулю два, элемент И 90. Третий коммутатор t6 содержит группу элементов И-ШТИ 91, элемент И 92. Четвертый коммутатор 17 содержит элемент И-ИПИ 93.

Первый дешифратор 8 (фиг.7) содержит триггер 94, элемент И-ИЛИ 95. Второй дешифратор 18 содержит триггер 96, элемент И-ИЛИ 97. Шестой комму- татор 19 содержит элемент И-ИЛИ 98. Седьмой коммутатор 20 содержит элемент И-ШШ 99..

Информационная шина 24 устройства содержит следующие линии: 100 - сигнал микропрограммной установки триггера 87{ 101 -,шина счетчика}-.

102- сигнал Счетчик равен

103- шина константы для модификации счетчика байтов в разделенном цикле.

Управляющая шина 25 устройства содержит следующие линии: 104 - сигнал сброса канала, 105 и 106 - синхросигналы; 107 и 108 - сигналы занесения- 109 - обратньй ввод; 110 - сигнал модификации счетчика адреса буфера, 111 - сигнал модификации счетчика байтов буфера, 112 - сигнал занесения в разделенном цикле, 1 13 - ввод; 114 - сигнал вьтолнения микропрограммы цепочки данных ; 115 - сигнал УСК готово ; 116 - вывод; 117 - выполняется разделенный цикл.

Управляющий вход 26 устройства содержит следующие линии адресации локальной памяти: 118 - запи12ь в седьмзоо ячейку локальной памяти; 119 - запись в восьмую ячейку локальНой памяти; 120 - запись, в первую ячейку локальной памяти, 121 - запись во вторую ячейку локальной памяти.

Первый и второй 2 регистры признаков предназначены для хранения флажков двух последовательных УСК, связанных флажком цепочки данных. Пятъй коммутатор 9 предназначен для объявления действительными флажками из первого

или из второго регистра признаков по сигналам с выходов блока 21 задания режимов обмена. Первый 3 и второй 10 счетчики адреса предназначены для ука- 5 зания адреса байта в буфере (точнее в двойном слове буфера, для чего достаточно трех разрядов) при записи в буфер байта данных с ШИН-А или при чтении байта данных из буфера на 0 ШИН-К. .

Входы S1, S2 двоичных реверсивных счетчиков служат для задания режима работы счетчика . 00 - хранение, .01 добавление единицы по сигналу на 5 входе С; 10 - вычитание единицы по сигналу на входе С; 11 - занесение информации с входа D по сигналу на .входе С, . .

Первый коммутатор 11 предназначен 0 для коммутации выходов первого 3 и второго 10 счетчиков адреса на адресную шину 29 устройства и далее в буфер, где определяет адрес байта буфера. Первый 4 и второй 12 пяти- 5 разрядные счетчики байтов служат для подсчета байтов, находящихся, в буфере. Второй коммутатор 13 служит для коммутации выходов первого 4 и второго 12 счетчиков байтов на вход блока Q 5 модификации. Последний служит для модификации первого 4 и второго 12 счетчиков байтов в разделенных циклах на константу, которая поступает на инфopмaциoн fый вход блока 5 модификации по шине 103. Если на входе S1 сумматора 77 (фиг.5) находится

единичный сигнал, то выполняется суммирование, а если нулевой - то вычи- тани.е .. ..

Первый 6 и второй 14 регистры со- стояния счетчика байтов предназначены для отображения состояния счетчика байтов, расположенного в локальной памяти, на аппаратуре канала. Занесение информации в регистры 6 .и 14 син- 5 хронизнровано с занесением ее во вторую ячейку локальной памяти.При зы- полнении операций ввода регистр состояния счетчика байтов сравнивается со счетчиком байтов буфера и их ра50

венство говорит о том, что все да.н-

ные по тек тцему УСК переданы в канал..

Разрядность регистра состояния счетчика байтов зависит от размера буфера. Для буфера в шестнадцать бай- 55 тов регистр состояния счетчика байтов должен быть пятиразрядным (0-4). Шина 101 сч.етчика сделана таким образом, что в разряды 0-4 регистра

состояния заносятся разряды ХЗ-7) младшего байта счетчика и байтов на локальной памяти, а на установку разрядов 0-2 регистра состояния заведена еще и сборка всех разрядов старшего байта и разряды 0-2 младшего байта счетчика байтов из локальной памяти, это разрешает сравнение счетчика байтов буфера с регистром состояния счетчика байтов только после того, как о н начинает отображать действительное значение счетчика байтов из локальной .

Третий коммутатор 16 предназначен, для коммутации на шину 28 счетчика байтов выходов первого 6 и второго 14 регистров состояния счетчика байтов в зав исимости от состояния выхода 41 блока 21 задания режимов обмена. Если при вводе периферий- 20 что в .канале может быть такое состояное устройство присьшает сигнал УПР-А, когда еще счетчик байтов в локальной памяти не исчерпан, то с выхода блока управления интерфейсом поступает, сигнал на коммутирутощий вход 27 уст- ройства и в этом случае коммутируются выходы первого 4 или второго 12 счетчиков байтов буфера в зависимости от состояния выхода 41 блока 21 задания режимов обмена.

Устройство управления каналами использует информацию с выхода третьего коммутатора 16 для формирования константы модификации адреса дан- ных и счетчика байтов, для формиро- вания маски для оперативной памяти в разделенных циклах. .Эта же/кон.стан- та по шине 103 поступает на вход блока 5.

Первая схема 7 сравнения служит для сравнения первого счетчика 4 бай- той буфера с первым регистром 6 состояния счетчика байтов. Сигнал сравнения с выхода узла сравнения говорит при вводе о том, что все байты данных с периферийного устройства переданы в канал.

Вторая схема 15 сравнения служит для сравнения второго счетчика 12 бай тов буфера с вторым регистром 14 со- стояния счетчика байтов.

Четвертый коммутатор 17 служит для выбора сигнала сравнения с выходов первой 7 или второй 15 схем сравнения в зависимости от состояния вы- хода 43 блока 21 задания режимов обмена. Первый 8 и второй 18 дешифраторы предназначены для фиксации в

23.8095 .6

канале сигнала Счетчик байтов равен нулю в зависимости от состояния выходов 41 и 43 блока 21 задания режимов обмена. Этот сигнал поступает по

5 линии 102 из устройства управления каналами, когда второе слово УСК с нулевым счетчиком байтов считывается из оперативной памяти во вторую ячейку локальной памяти (сигнал 108),

О когда второе слово УСК с нулевым счетчиком байтов пересылается в микропрограммные предвыборки (при вводе) во вторую ячейку локальной памяти а также при выполнении последнего

15 разделе.нного цикла, в котором нулевой после модификации счетчик байтов записывается во вторую ячейку локальг. ной памяти (сигнал 112). Необходимость в дешифраторах вызвана тем.

7

ние, когда он хранит одновременно два сигнала Счетчик равен нулю,

Например, в предвыборке при вводе еще до получения сигнала Счетчик равен нулю для перв.ого УСК может быть получен этот сигнал для второго УСК. Шестой 19 и седьмой 20 коммутаторы введены в связи с разделением функции сигнала Счетчик равен нулю по времени. Шестой коммутатор 19 осуществляет коммутацию по сигналу 43 выхода блока 21, а седьмой коммутатор 20 осуществляет коммутацию по сигналу 41 с выхода блока 21. Блок 21 задания режимов обмена преднзначен для управления работой всех указанных блоков.

Перенумеровывают все УСК, связанные флажком цепочки данных, начиная с того, в котором первым указан фла жок цепочки данных, и ему присваивают первьш номер (1,2,3,4...). Состояние выходов блока 21 определяет следующее. О на выходе 41 - работа с оперативной памятью идет под управлением УСК с нечетным номером, 1 на выходе 41.- работа с оперативной памятью идет под управлением УСК с четным номером; О на выходе 43 - работа с интерфейсом идет под управлением УСК с нечетным номером; 1 на выходе 43 - работа с интерфейсом иде под управлением -УСК с четным номером

На фиг. 8 показана последовательность переключения выходов блока 21., для ввода и вывода, если канал выполняет три связанных флажком цепочки данных УСК. Первая позиция в таблице

показывает исходное состояние выходов блока 21, в это же состояние блок 21 переходит после обработки прерывания в канале. Если более, трех УСК связано флажком цепочки данных, то из позиции 6 блок переключения переходит в позицию 3 и т.д.,

Формирователь 22 сигналов занесения .используется для выработки сигналов занесения на выходах 55 и 53, если выполняется микропрограмма предвы- борки УСК при вводе или микропрограмма цепочки данных при выводе. Канал использует для работы восемь ячеек локальной памяти (фиг.11).Первая и вторая ячейки используются для хранения текущего УСКJ третья ячейка - для хранения адреса УСК седьмая и восьмая ячейки - для хранения предвы- бранного УСК.

Рассматривается работа устройства управления во встроенном селекторном канале с микропрограммным управлением В этом случае шина 23 данных устройства соединена с выходной шиной дан- 25 устройства (фиг.6).

35

ных центрального процессора, информационная шина 24 устройства соединена с выходом устройства управления каналами, управляющая шина 25 устройства соединена с выходом блока 30 управления каналом, управляющий вход 26 соединен с выходом блока локаль- . ной памяти каналов, коммутирующий вход 27 устройства соединен с выходом блока управления интерфейсом, шина 28 счетчика байтов, соединена с входом устройства управления каналами, адресная шина 29 устройства соединена с блоком управления буфером данных, первый и второй управля- 40 гощие выходы 30 и 31 устройства соединены с входами блока управления интерфейсом.

Канал работает следующим образом.

В исходном состоянии после сбро- 45 са канала или после сброса в начале выполнения цепочки команд (сигнал 104) выходы 41 и 43 блока 21 находятся в состоянии 01, триггеры 45 и 46 формирователя 22 сброшены. Расмат- о ривается выполнение трех УСК, связанных флажком цепочки данных.в первом из которых задана операция ввода.

Операция ввода-вывода (в. зтом слуДалее микропрограмма запускает начальную выборку в канале и устанавливает триггер УСК готово в блоке управления канала. Сигнал 115 поступает на вход блока 21. В блоке 21 по совпадению сигналов на десятом (отсутствует сигнал 114 выполнения микропрограммы цепочки данных) и одиннадцатом входах элемента И-ИЛИ 38 сигнал с его выхода переключает триггер 32 в противоположное состояние (в эт.ом случае в состояние О) по синхросигналу 105, а по синхросигналу 106 устанавливается новое значение тр-иггеров 33,36 и выходы 41, 43 блока переключения переходят в состояние 00.

Пока аппаратура канала выполняет. начальную выборку микропрограмма, если есть флажок цепочки данных, переходит к предвыборке второго УСК.Мик- рокоманда Г-1К7 анализирует код операции и делает ветвление по трем направлениям. Далее в случае ввода или ввода обратного выполняет анализ на .самоопределенную цепочку.. В случае самоопределенной цепочки предвыборка не выполняется. Микрокоманда МК9 считывает первое слово УСК в седьмую

чае операция ввода) инициируется ко- ;ячейку локальной памяти, МК10 выполмандой ввода-вывода Начать ввод-няет анализ кода операции, если код

вывод (НВВ).. Микропрограмма, реали-операции 08 Переход.в канале., то

зующая команду НВВ, считывает из опе выполняется опять анализ на самоопре

380958

ративной памяти первое слово первого УСК в первую ячейку локальной памяти (фиг.1). При этом вырабатывается сигнал 107 занесения, по которому код 5 операции заносится в канал и устанавливается сигнал 113 Ввод на управляющей шине 25 устройства, вЫ- полняется занесение трех младших разрядов адреса данных с шины 23 дан- Юных устройства в первьй счетчик 3 адреса (фиг.А), выполняется сброс первого счетчика 4 байтов буфера (фиг,5) - заносятся нули, в двоичный реверсив- . ный с-четчик 71 с выхода блока 5 моди- 15 фикации, в котором на входах группы элементов И 78 отсутствует сигнал 117 разделенного цикла. Затем микропрограмма считывает второе слово первого УСК, при этом вырабатьгеается еиг- 20 нал 108 занесения, по которому выполняется занесение в первьй регистр признаков и в первый регистр 6 ср- . стояния счетчика байтов с шины 101 счетчика информационной шины 24

5

0 .

Далее микропрограмма запускает начальную выборку в канале и устанавливает триггер УСК готово в блоке управления канала. Сигнал 115 поступает на вход блока 21. В блоке 21 по совпадению сигналов на десятом (отсутствует сигнал 114 выполнения микропрограммы цепочки данных) и одиннадцатом входах элемента И-ИЛИ 38 сигнал с его выхода переключает триггер 32 в противоположное состояние (в эт.ом случае в состояние О) по синхросигналу 105, а по синхросигналу 106 устанавливается новое значение тр-иггеров 33,36 и выходы 41, 43 блока переключения переходят в состояние 00.

Пока аппаратура канала выполняет. начальную выборку микропрограмма, если есть флажок цепочки данных, переходит к предвыборке второго УСК.Мик- рокоманда Г-1К7 анализирует код операции и делает ветвление по трем направлениям. Далее в случае ввода или ввода обратного выполняет анализ на .самоопределенную цепочку.. В случае самоопределенной цепочки предвыборка не выполняется. Микрокоманда МК9 считывает первое слово УСК в седьмую

деление и считывание первого слова УСК и анализ кода операщш на 08. Микрокоманда МК11 считывает второе слово УСК в восьмую ячейку локальной памяти, МК13 устанавливает триггер 45 занесения формирователя 22 сигналом микропрограммной установки 39. При выполнении MKU по сигналу 118 с вьпсода.блока локальной памяти каналов и сброшенному триггеру 46 предвыборки вырабатывается сигнал занесения с выхода 55, по которому младшие три разряда адреса данных пред- выбранного УСК заносятся во второй счетчик 10 адреса и происходит сброс второго счетчика 12 байтов, как указано для первых счетчика адреса и байтов.

Во время выполнения МК15 по сигналу 119с выхода блока локальной памяти вырабатывается сигнал 53 занесения, по которому выполняется занесение во второй регистр 14 анализа счетчика байтов и во второй per гистр 2 признаков. Во время выполнения Щ16 сигналом 100 микропрограммной установки с выхода устройства управления канала устанавливается триггер 46 предвыборки формирователя 22, сигнал с выхода которого (есть сигнал 113 Ввод)через элемент И 50 и элеме.нт ИЛИ 51 сбрасывается триггер 45 занесения. Затем микропрограмма предвыборки передает управление микропрограмме реализации команды НВВ, которая анализирует результат начальной выборки и, если он успешен, заканчивает выполнение НВВ с нулевым признаком результата Перифсфийное устройство, с которым канал устанавливает связь в начальной выборке, чере.з некоторое время начинает передавать данные, которые поступают с шин абонента в канал и записываются в буфер согласно адресу, которьй поступает на вход блока управления буфером с выхода первого счетчика 3 адреса буфера через коммутатор 1 1 счетчиков адреса буфера. Первый счетчик 3 адреса буфера модифицируется на +1 по сигналу 110 модификации с блока управленрЕЯ каналом первый счетчик 4 байтов буфера модифицируется на +1 по сигналу 111 модификации. По мере поступления дан- Hbix с интерфейса буфер заполняется, а когда первый регистр адреса бу- ;фера после очередной модификации по510с 15

т20

,

23809510

казывает границу двойного слова, данные из первого двойного слова буфера передаются в память в так называемом разделенном цикле, а данные с интерфейса записываются во второе двойное слово буфера. В разделенном цикле двойное слово данных из буфера канала передается в оперативную память, модифицируется адрес данных в регистре адреса данных канала, счетчик байтов во второй ячейке локальной памяти. Разделенный цикл - это одна микрокоманда, аппаратурно формируемая в регистре микрокоманд по запросу из канала, вставляемая в любую последовательность микрокоманд, выполняемых центральным процессором.

В разделенном цикле выполняется модификация счетчика байтов буфера и регистра состояния счетчика байтов. Первьм счетчик 4 байтов буфера уменьшается на константу, численно равную количеству байтов, переданных из канала в оперативную память. Модификация выполняется узлом 5 модификации, на первый вход которого поступает константа модификации по шине 103 с выхода устройства управления каналами. На второй вход узла 5 поступает сигнал 1.17 разделенного цикла, на третий вход поступает выход первого счетчика 4 байтов буфера через коммутатор 13. счетчиков байтов буфера (фиг.5),. занесение модифицированного значения в первый счетчик 4 байтов с выхода узла 5 модификации выполнения по сигналу 112 занесения в разделенном цикле.

Счетчик байтов из локальной памяти в разделенном цикле для модификации считывается на вход АЛУ, модифицируется и модифицированный записывается во вторую ячейку локальной памяти. Одновременно идет и занесение в пер- вьй регистр 6 анализа счетчика байтов с шины 101 счетчика с выхода устройства управления каналами, по сигналу 112 занесения в разделенном цикле ..

«5

30

35

40

45

Когда последний байт по первому УСК УСК принят в буфер, вырабатывается сигнал сравнения с выхода первой схемы 7 сравнения, которьш проходит через коммутатор 17 на вход блока 21, а с выхода 30 устройства в блок управления интерфейсом, где определяет конец передачи данных при вводе, если в.канале нет флажка цепочки

15 2/

фигА

r08

fw

07

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке системы ввода-вывода ЭВМ с микропрограммным управлением каналами ввода-вывода. Целью изобретения является повьше- ние скорости передачи данных канала при работе с цепочкой данных за счет предварительной выборки следующего управляющего слова канала. Устройство содержит первый-и второй регистры флажков, коммутатор флажков, первый и второй счетчики адреса буфера, коммутатор счетчиков адреса буфера, первый и второй счетчики байтов буфера, коммутатор счетчиков байтов буфера, узел модификации, первый и второй регистры анализа счетчика байтов, ко.м- мутатор счета байтов, первый и второй узлы сравнения, коммутатор сигнала сравнения, первый второй узлы нуля « счетчика, первый и второй коммутаторы нуля счетчика, блок переключения, узел занесения. 11 ил. W с (Х) 00 о со ел

fos

n

S3

т

S3

75

гг.

.

43,

иг.

«.

(. в

Редактор С..Лисина

Составитель Т. Арешев

Л.Серяюкова . Корректор Л. Пилипенко

Заказ 3293/50Тираж 67t

ВНИЙПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое пзредприятие, г. Ужгород, ул. Проектная, 4

Фиг. 77

Подписное

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Селекторный канал | 1977 |

|

SU690472A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-04-11—Подача