ходы всех блоков обнаружения ошнбо, кроме аос:лвдн(го, подключены а управлй ошим входам соответствукяаих регистров сд йга, их икформаинонные взкгаЬг с вяанейы i оа- ними из выходов блоков дейодвровани i,

подключекными хо входам блока свер- кв по модулю йва по , выход кото ого соединен со входом допсмшк-гельао 88 дея- наго Б. устройство Еоктрояьного регйс гра сдвйге выходы которого сюдвлючекы ю ; входам соотавтстэующихрэг5к;т ров сяв tra.

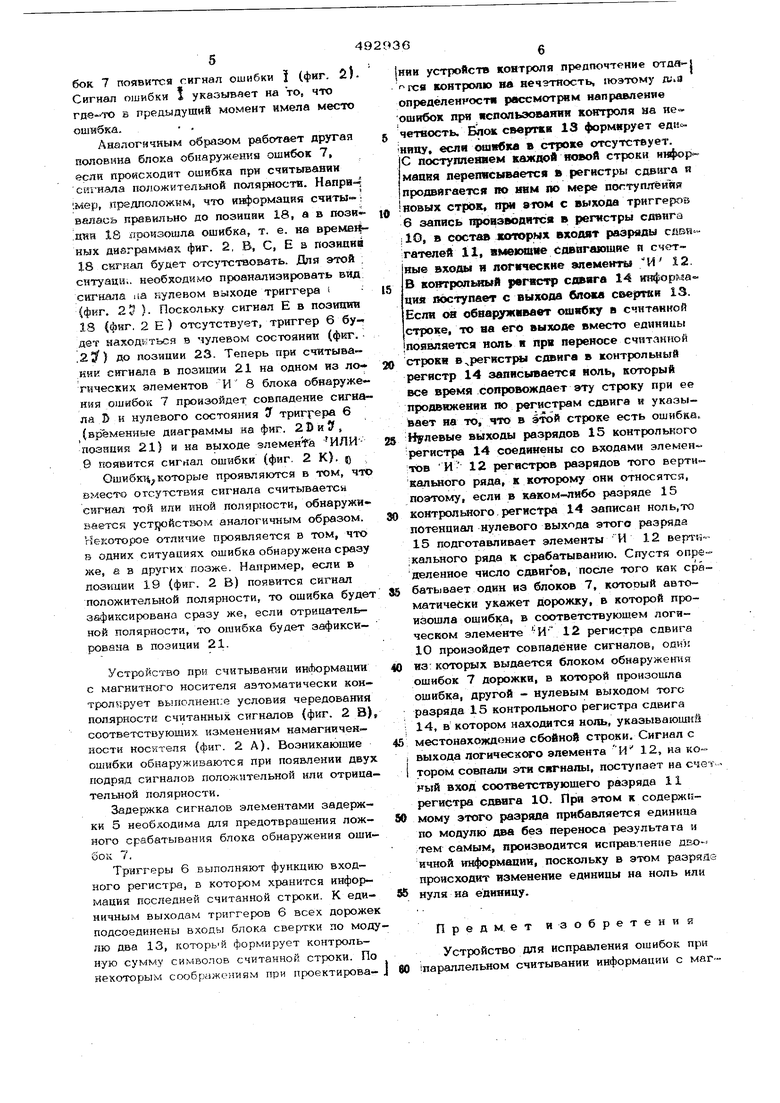

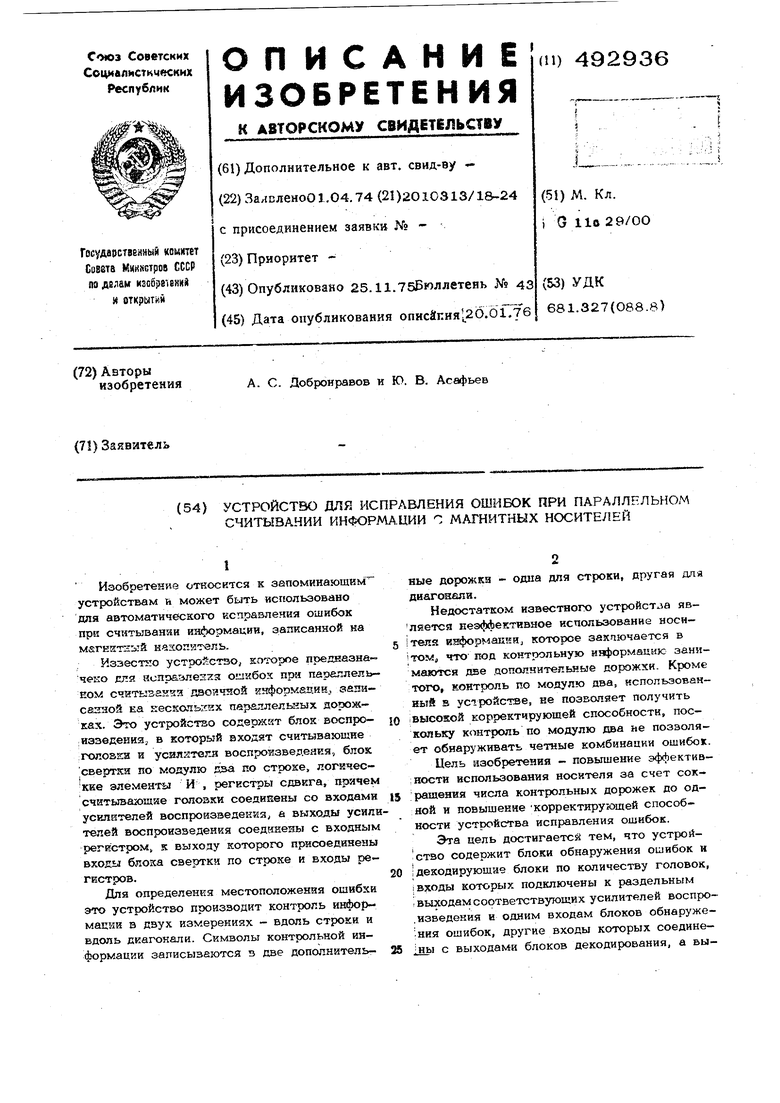

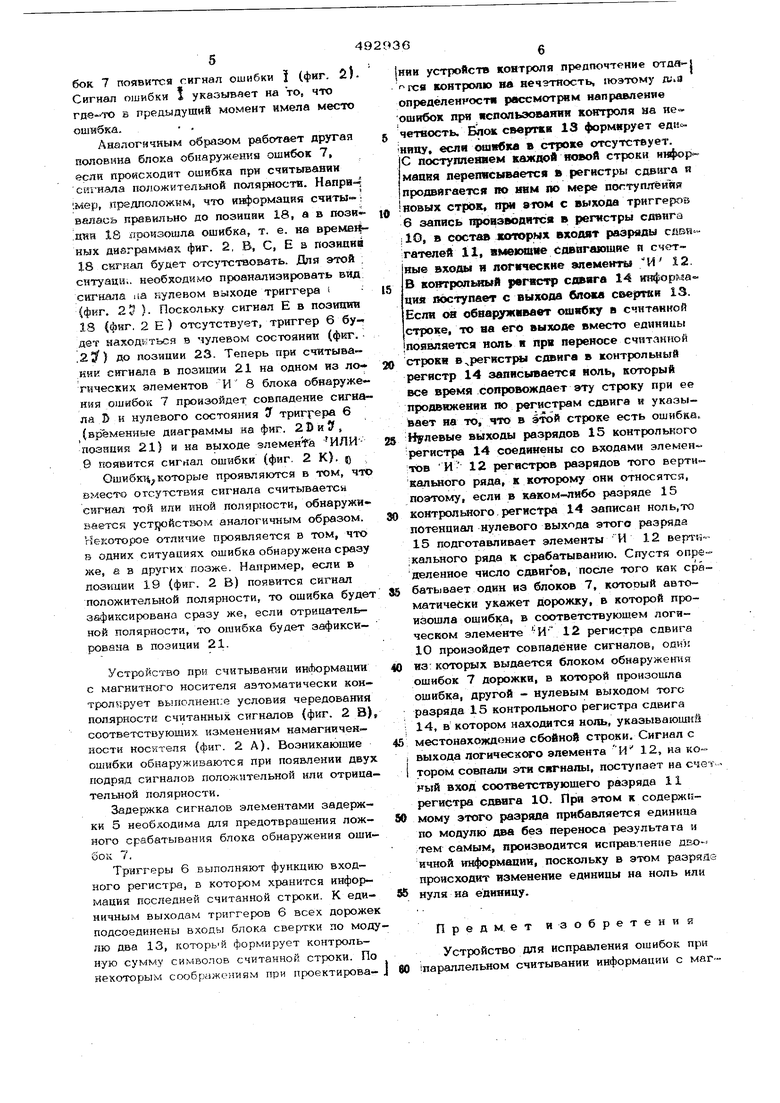

Не фиг. 1 приведена блок-схема П ед- ложенного устройства; йа ФЕТ. 2 - вр диаграммы, нллюстрйруюише проц сс обнаружения: ошибок устройст-эом.)

Устройство содержит блок воспрон; ве- дення 1, и который входят считьгааюш te головкк 2 и усилители воспроизведена t 3,; блоки 4, декодкровання построенные н i элементах задержки 5 к триггерах 6f обнаружения ошибок 7, постровяньг на логических элементах И 8 и ИЛИ 9, регистры сдвига 10,: содержащие разр$ пы ; , сдзкгателей 11 а логические элек4ент1 :

И 12, блок свертки по модулю два ) о , . cTj.Ke 13, контрольный регистр сдвкг i . ; 14, содержащий разряды сдвигателей 5. Счйтываюшне головки 2 соединены со хо дами усл4пктелей вослроиаведеяйя 3, а раздельные выходы усилителей соединены го i входами элементоз задержки S и со вз - дами логических элементов И 8. Вы: о- . йы логических алеменэчэв ИЛИ 9 бло ;ов обнаружения ошибок 7 соединены с ynj. 1БЛя юшими входами логических элементов И 12 регистров сдвига 1О, а выходы тр г геров шгформацйонными входами т р Bbis разрядов И регистрсв сйвкга и ci входами блоха свертг-ки по модулю два ,3( BbikoA ко1-орого соединен со вжодом перг го разряда 13 контрольного регистра с юига 14.

Устройство работает следующим обр зом. Информация считывается с магнит ого носителя считывающими головками 2 в i виде сигналов положительной н отрнцат иь-. ной полярности поступает на вход усиля г«-, ля воспроизведения 3. С его выходов ci г калы поступают на блоки 4 и 7. Устрой ство обнаруживает и исправляет ошибки (гезазисймо от того, как кодируется инф р-; м-ацйЕ при записи на магнитный носител: Для определенности на фиг. 2 иллюстри{ f е-гса обнаружение ошибок при записи информации модифнцнрованным методом бес возвращения к нулю, в Которюм единице двоичной информации соответствует изме . кекле состояния намагниченности HocHTej я, а нулю - отсутстБне изменения. На фнг.; . J

Л приведена двоичная последо.вательнсють в соответствующее ей состоякяе намагян ченностн поверхности носителя. Исходным состоянием при счнтыванигз яшхается ссс«гояние ) носителя, триггер 6 находнГ ся в нулевом состояшик (незаштрихованная половина) на его единичном выходе потенциал, соответствугоший нулю фиг,).

При перемещении иосйгели счнтыьаюшив 14 ловки 2 фиксируют изменение немагнкчея-. ностн носителя и вырабатывало сЕГналы показанные на фиг. 2 В, амплитуда котор.«х пропорциональна скорости изменения нвмаг вйченности носителя, в знак - направлении изменения. Считанные сигналы поступают на усилитель 3, который усиливает а распределяет сигналы таким образом, чЮ на одном выходе усилителя BocnpoHSBejseHHfi сигналы пoявляютcяf тогда, когда на его входе присутствует с,йгнал положительной поляршостЕ, а на другом выходе - когда на входе сигнал отрицательной полярности. Это иллюстрируют Диаграммы фш. 2 В, С и и . Сигналы С в S задерживаются элемвнТами задержки 5 блока 4 на времк, ве меньшее длительности сигнала, формируемого усилителями воспроязведения. Задержжа необходима для правильной работы устройства, когда ошибки отсутствуют. Задержанные сигналы Е и F (фиг. 2 Е, F ) поступа от на раг1ельные входы триггера 6, Е на единичный вход, F - на нулевой. Триггер 6 преобразует информацию из импульсной формы в потенциальную. На фиг. 2 G приведена форма сигнала не единичном выходе триггера 6, кото рая соответствует изменениям состояния намагничешш сти носителя, сдвинутым во времени при отсутствим ошибок при считывании информации,

Рассмотрим процесс обнаружения ошибок устрюйством. На фиг. 2 отдельные временные позиции обозначены чкслаш 16-24. Прегположим, что в позиции 17 (фиг. 2 A,B ) вместо единицы считан ноль. Это означает, что в позиции 17 на временных диаграммах (фиг. 2 В, D/ F) сигнал будет отсутствовать {заштрихованные импульсы), Форма сигнала на едиггачном выходе триггера 6, соответствующая этой сятуацин, показана на фиг. 2 Н. При поступлении чередного считанного сигнала, и данном случае он появится в позкиин 18 (фкг. 2 В, С, Е) и в одном из логических элемен тов И 8 блока обнаружения ошибок 7, роизойдет совпадение сигнала С усилитея воспроизведения 3 и единичного состоя-. ия Н триггера 6 (временные диаграммы иг. 2 с н н, позиция 18) и на выходе лемента ИЛИ 9 блока обнаружения оши- бок 7 появится сигнал ошибки 1 (фиг. 2) Сигнал ошибки I указывает на то, что гпе-«лч5 в предыдущий момент имела место ошг«бка. . Аналогичным образом работает другая половина блока обнаружения ошибок 7, если происходит ошибка при считывании СЕ гнала положительной полярности. НаприЧ .мер, предположим, что информация считы- правильно до позиции 18, а в пози лКя 18 йроизошла ошибка, т. е. на времай ных диаграммах фиг. 2, В, С, Е а позиций 18 сигнал будет отсутствовать. Для этой снтуаци,. необходимо проанализировать вид сигнала аа кулевом выходе триггера i (фиг. 23 ). Поскольку сигнал Е в позиции 18 4Ф8Г. 2 Е ) отсутствует, триггер 6 бу- дет находиться в чулевом состоянии (фкг. .2tf) до позиции 23. Теперь при считыва кик стг-нела в позиции 21 на одном из логических элементов И 8 блока обнаружения ошибок 7 произойдет совпадение сигна ла В и нулевого состояния триггера 6 (временные диаграммы на фиг. 2ЪкУ , ПОЗИЦИЙ 21) и на выходе элемен1%1 ИЛИ9 появится сигнал ошибки (фиг. 2 К). 5) Oшмбкн которые проявляютсй в том, что вместо отсутствия сигнала считываетсн сигнал той ипи иной полярности, обнаружи веется уст1}ойстзом аналогичным образом. Некоторое отличие проявляется в том, что Б ОДНИХ ситуациях ошибка обнаружена сразу же, а в других позже. Например, если в ПО31ШИИ 19 (фиг. 2 В) появится сигнал положительной полярности, то ошибка будет зафиксирована сразу же, если отрицательной полярности, то ошибка будет зафикси- рована в позиции 21. Устройство при считыват и информации с магнитного носителя автоматически контролкрует выполнение условия чередоват1Я полярности считанных сигналов (фиг, 2 В) соответствующих изменениям намагничен- ности носителя (фиг. 2 А). Возникающие ошибки обнаруживаются при появлении двух подряд сигналов положительной или отрица- тельной полярности. Задержка сигналов элементами задержки 5 необ.к.одима для предотвращения ложного срабатывания блока обнаружения ошибок 7. Триггеры 6 выполняют фупкцию входного регистра, в котором хранится информация последней считанной строки. К едияичным выходам триггеров 6 всех дорожек подсоединены входы блока сверугки по моду лю два 13, которьй формирует контрольную сумму символов считанной строки. По „„...j. - некоторым ссюбраженийм при проектирова:нии устройств контроля предпочтение отаа-i гся контролю на нечэтность, 1юэтому определенкостш реюсмотрим направление ошибок при яспольэоваяни контроля на не четность, Йпок свертки 13 формврует еди нину, если ошкбка в строке отсутствует. С постуллевием каждой новой строки иифор мапня лерепнсывается в регистры сдвига я продвигается по ннм ло мере погтупяёияй новых строк, при этом с выхода триггеров 6 запись процзводится в регистры сдвига 10, в состав которых входят разряды сяви гатепей 11, в юхяине сдвигающие п счетные входы и логкческне алемеиты И 12. В контропы1ый {мгвстр сдвага 14 ция поступает с выхода блока сверггки 13. Если ш обнаруживает ошибку в считанной строке, то аа его выходе вместо единицы появляется ноль в при переносе считанной строке в регистры сдвига в контрольный регистр 14 запнсывается ноль, который все время сопровождает эту строку при ее продвиженнн по регистрам сдвига к указывает на то, что в этой строке есть ошибка, Hjrлевые выходы разрядов 15 контрольного регистра 14 соединены со входами элементОв И 12 регистров разрядов того верти кального ряда, к которому они относятся, поэтому, если в каком-либо разряде 15 контролыюго. регистра 14 записан ноль,то потенциал нулевого выхода этого разряда 15 подготавливает элементы И 12 BepTti-;кального ряда к срабатыванию. Спустя onpie- неленное число сдвигов, после того как срабатывает один из блоков 7, который автоматически укажет дорожку, в которой произошла ошибка, в соответствующем логическом элементе -И 12 регистра сдвига 10 произойдет совпадение сигналов, опик нз: которых выдается блоком обнаружения ошибок 7 дорожки, в которой произошла ошибка, другой - нулевым выходом того разряда 15 контрольного регистра сдвига 14, в котором нахохштся ноль, указываюшнй местонахождение сбойной строки. Сигнал с выхода логическсяО элемента H 12, на котором совпали этн сигналы, поступает на сгеткый вход соответствующего разряда 11 регистра сдвига 1О. При этом к содержимому этого разряда прибавляется единица по модулю два без переноса результата и тем самым, производится исправление ДЕО- ичной информации, поскольку в этом разряае происходит изменение единицы на ноль или нуля на еднннцу. Предмет изобретения Устройство для исправления ошибок при ..,. параллельном считывании информации с маг.йгных носителей, содержащее блок в юпройэведения со счит .юаюшими головкам i и роответсткуюшимн усилителями асспр Hv aejjej e, блок сверткч по модулю два п( стро/ее, «{рдключенный к регистрам сдвига о т л и чающееся тем, что, с целью повышекгая корректирующей способное т и устройства, оио содержит блоки обнаружь яия ошибок и блоки декодированЕя по колк считывающих головок, входы котор IX подключены к раздельным выходам со Tsefсттвуюших усилителей воспроизведения к ршим входам блоков обнаружения |оши «ж. другие входы которых соединены с выходами блоков декодирования, а выходы всех блоков обнаружения ошибок, крс е послед него, подклю ены к упраалкюшкм вуодам соответствующих регистров сдвига информационные входы которых соедпнены с одними на выходов блоков декодирования, г ояк;1ючениыми КС входам блока свертки ло модулю два по строке, выход которого соединен со входом дололквтельно1 введенного в устройство кoнтpoлыioгo регистра сдвиг-а, выходы которого подключены ко входам оответч твуюших регкстровсдвига.

Фиг. I

Фиг,2

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Устройство приема тональных сигналов | 1991 |

|

SU1793560A1 |

| СПОСОБ И УСТРОЙСТВО ИЗМЕРЕНИЯ АЗИМУТА РАДИОЛОКАЦИОННЫХ ЦЕЛЕЙ | 2006 |

|

RU2319980C2 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК | 1996 |

|

RU2109405C1 |

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Логический анализатор | 1980 |

|

SU890396A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

Авторы

Даты

1975-11-25—Публикация

1974-04-01—Подача