(5t) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАГИСТРАЛЕЙ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с общей магистралью вычислительной системы | 1982 |

|

SU1100614A1 |

| Устройство для контроля магистралей ЭВМ | 1980 |

|

SU945868A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1180912A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных устройствах, построенных по принципу общей магистрали.

Известно устройство для контроля ЭВМ, включающее в себя объединенные общей информационно-адресной магистралью центральный процессор памяти и контролеры ввода-вывода. Устройство подключено к магистрали и содержит соединенные между собой интерфейсный блок, таймер, счетчИк адреса, блоки посылки и проверки тестовых сигналов 1 .

В процессе работы ЭВМ Устройство периодически проверяет ее работоспособность и, если это возможно, локализует и логически изолирует отказавший блок. При этом время между появлением отказа и его обнаружением может оказаться достаточно большим (равным времени между проверками), что в ряде сяучаев недопустимо.

с другой стороны, увеличение частоты проверок снижает производительность ЭВМ, так как все большая часть машинного времени расходуется на выполнение контрольных, а не полезных операций.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для контроля магистрали ЭВМ, содержа1цее блоки обнаружения ошибок, соединенные посредством группы однонаправленных и двунаправленных адресных, информационных и управляю1чих связей с функциональными блоками ЭВМ. Блок обнаружения ошибок выполнен в виде после: довательно соединенных блока сравнения, триггера ошибки и инвертора, первая группа входов блока сравнения является группой информационных входов этого блока и подключена к группе двунаправленных адресных и информационных связей, вторая группа входов блока сравнения объединена и является эталонным входом блока сравнения, выход инвертора является выходом блока обнарумения ошибки 2 .

Принцип работы этого устройства состоит в следующем.

При работе ЭВМ в автоматическом режиме информационно-адресная магистраль периодически освобождается от передачи полезных сигналов на более или менее продолжительные интервалы времени, которые и используются для проверки магистрали. В эти промежутки времени сигналы на магистрали сравниваются с эталонными сигналами. Если сигналы совпадают, то магистраль считается исправной, если нет, то устройство формирует сигнал на выходе триггера ошибки. Этот сигнал служит, например, дл отключения отказавшейся ЭВМ и подключения другой.,,,,|Срезервной) ЭВМ к системе, работающей в реальном времени.

Устройство обеспечивает быструю реакцию на отказ магистрали, так как частота проверок равна частоте освобождения магистрали, и характеризуется простотой и полным отсутствием каких-либо требований к программному обеспечению(контроль производится аппаратным путем).

Недостатком этого устройства являются низкие функциональные возможности из-за отсутствия средств обеспечения коррекции обнаруженных ошибок.

Цель изобретения - расширение фун циональных возможностей устройства за счет обеспечения возможности корректировки однократных неисправностей магистрали.

Поставленная цель достигается тем, что в устройство для контроля магистралей ЭВМ, содержащее блоки обнаружения ошибки, причем информационные входы и выходы каждого блока обнаружения ошибки соединены с соответствующей группой информационных шин соответствующей контролируемой магистрали, управляющий вход каждого блока обнаружения ошибки соединен с управляющей шиной контролируемой магистрали, выход блока обнаружения ошибки соединен с шиной контрольного разряда соответствую1цей группы шин контролируемой магистрали, введена группа блоков коррекции, каждый из. которых содержит два коммутатора, причем первая группа входов и выходо

первого и второго коммутаторов соединена с соответствующей группой шин .контролируемой магистрали, вторая группа входов первого и второго коммутаторов является группой входов устройства, вторые группы выходов каждого коммутатора являются группой выходов устройства, управляю1цие входы первого и второго коммутатора являются управляющим входом блока коррекции и соединены с управляющей шиной магистрали.

Коммутатор содержит первый и второй инверторы, регистр , первую и

5 вторую группу сумматоров по модулю два, группу элементов И, мажоритарный элемент, узел контроля по четности и элемент И, причем группа информационных входов коммутатора соединена с первыми входами соответствующих сумматоров по модулю два первой и второй групп и с информационными входами узла контроля по четности , вход контрольного разряда группы информационных входов коммутатора соединен с дополнительным входом узла контроля по четностии через первый инвертор - с первым входом элемента И, выход которого является управляющим входом регистра, выходы сумматоров по модулю два первой группы соединены с информационными входами регистра, информационные выходы , которого соединены с первыми входами соответствующего i элемента И группы, выход каждого элемента И группы соединен с вторыми входами соответствующего сумматора по модулю два второй группы, выходы которых и вход первого инвертора образуют группу информационных выходов коммутатора, выход узла контроля по четности соединен через второй инвертор с вторыми входами элементов И группы, первый , второй и третий входы мажоритарного элемента соединены с тремя информационными входами группы входов коммутатора, выход коммутатора соединен с вторыми входами сумматоров по модулю два первой группу, управляющий вход коммутатора с вторым входом элемента И.

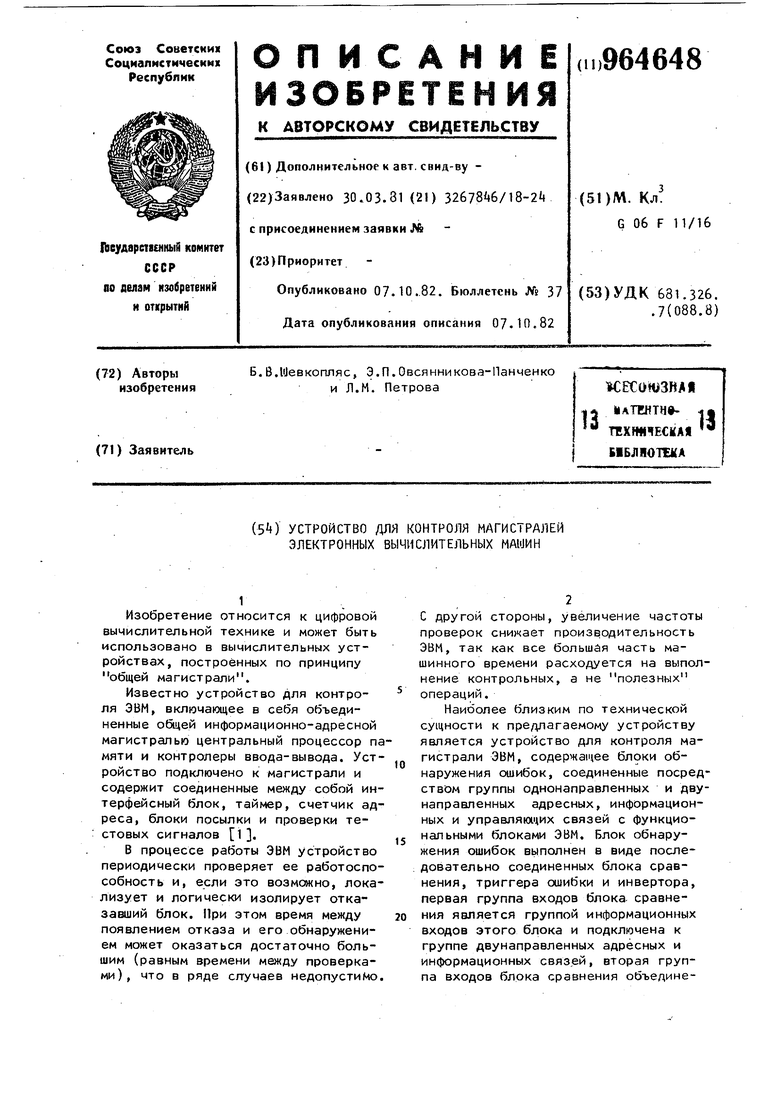

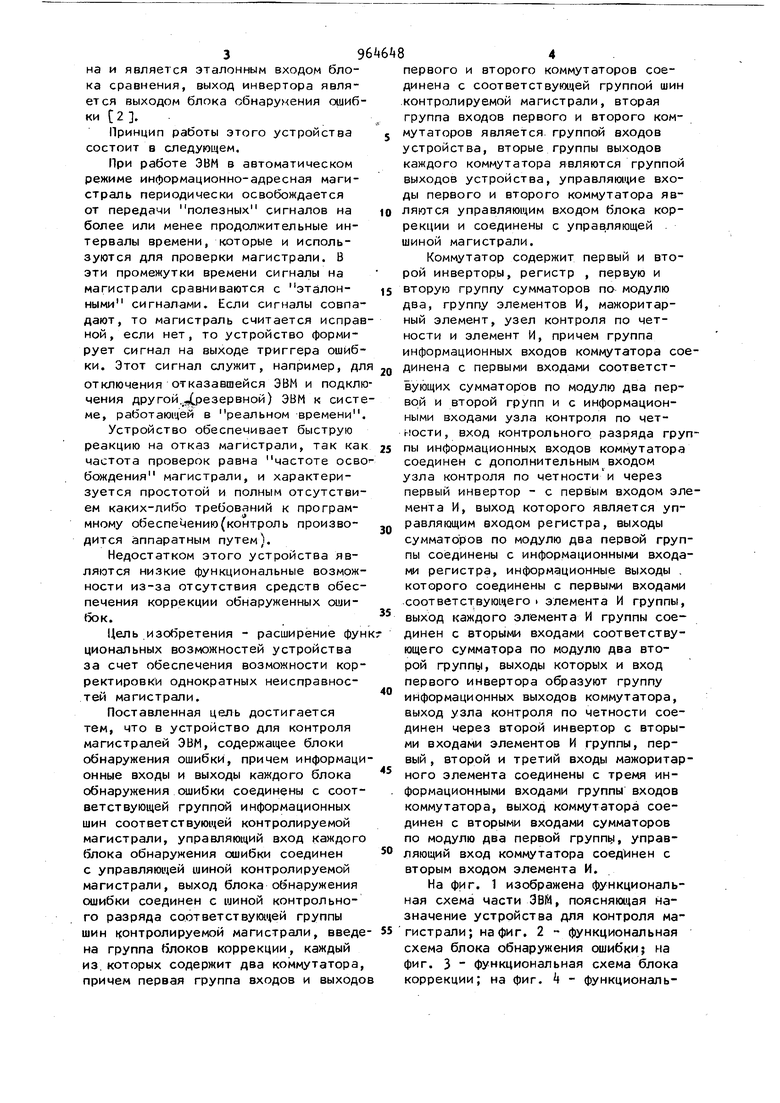

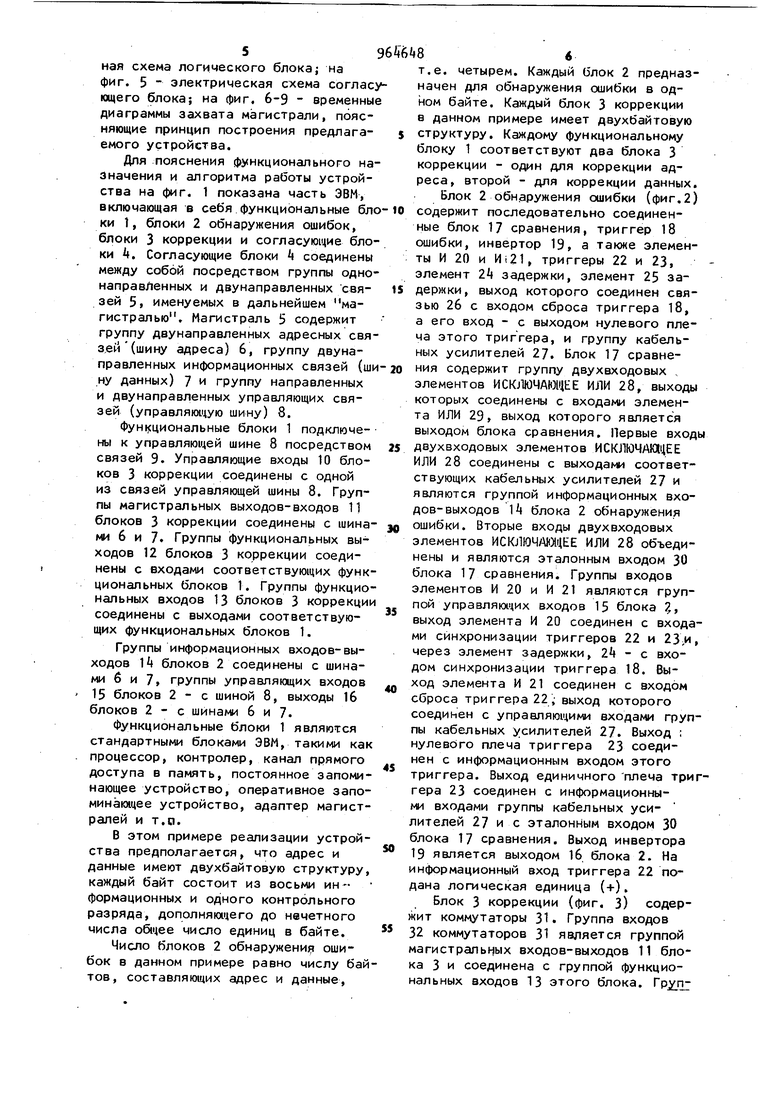

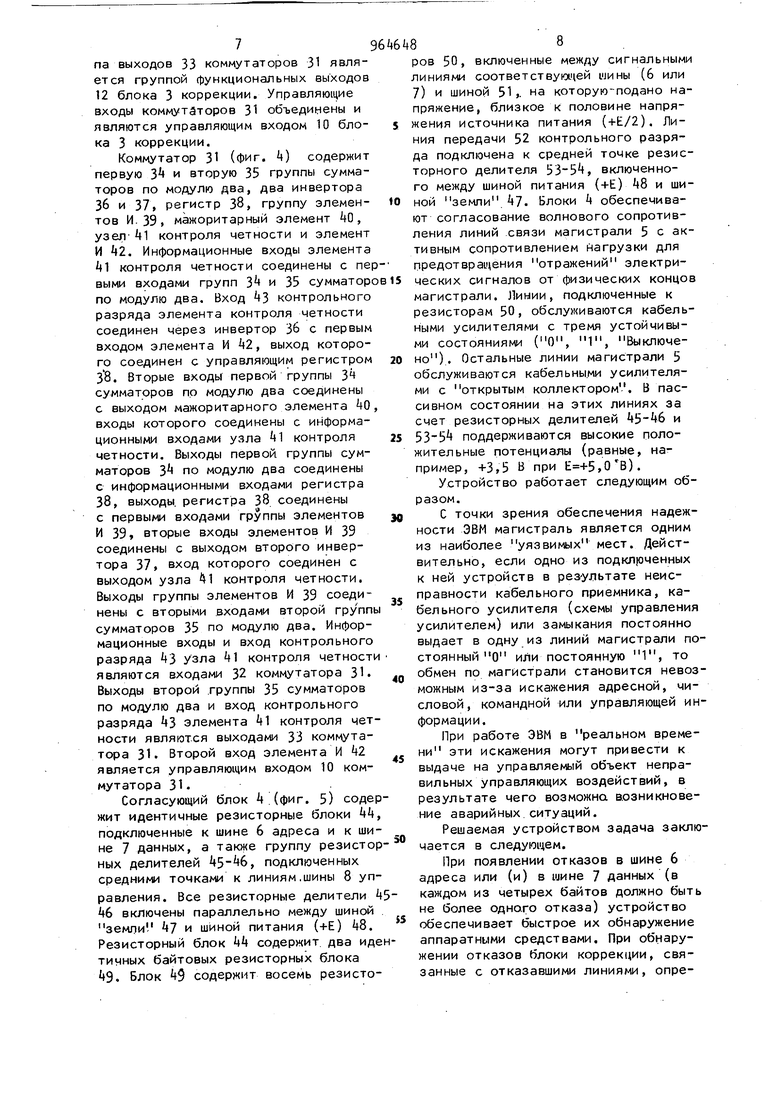

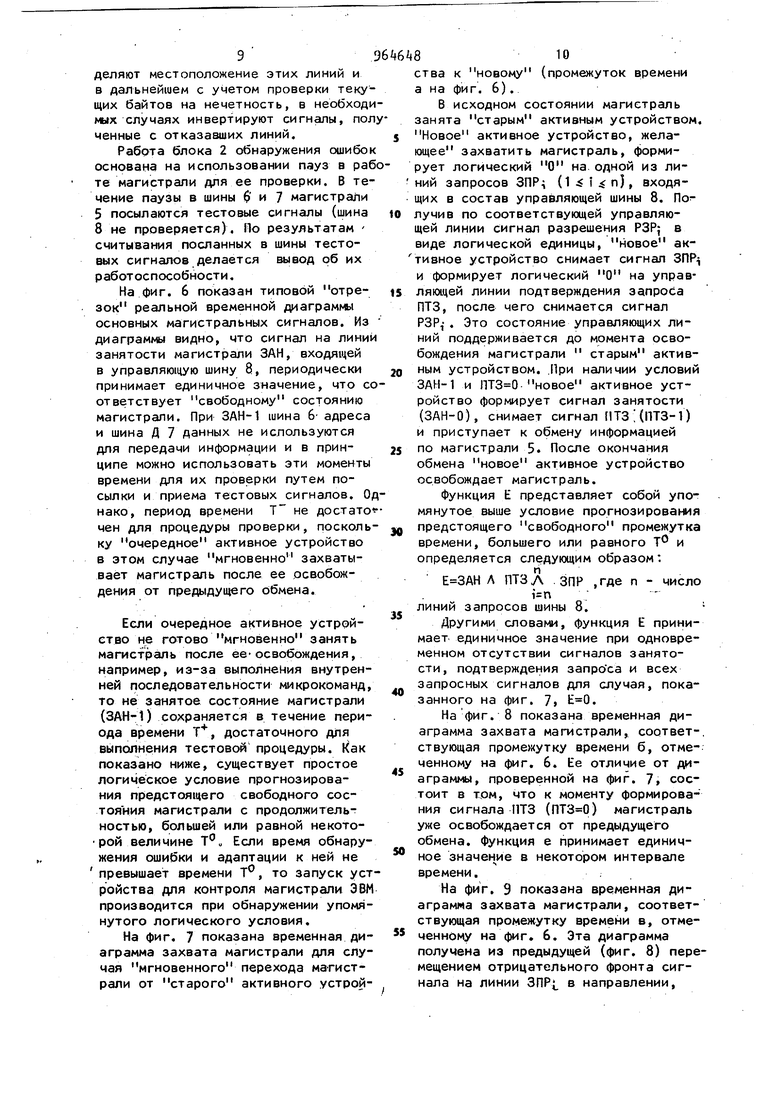

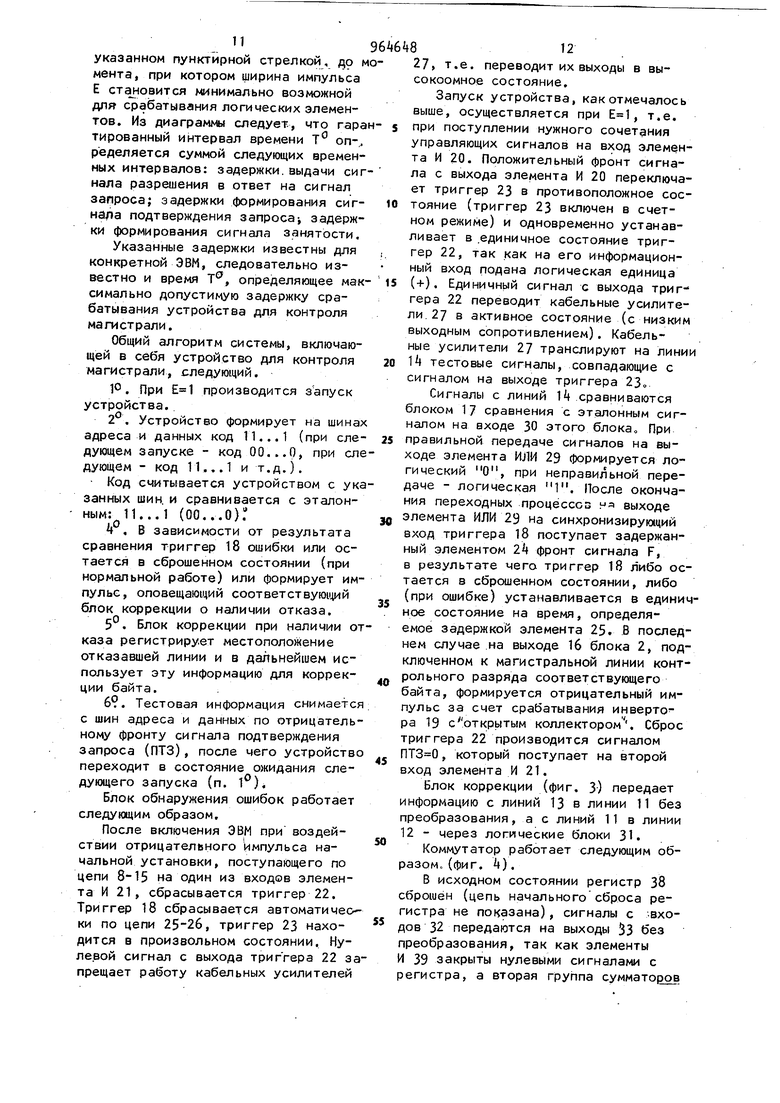

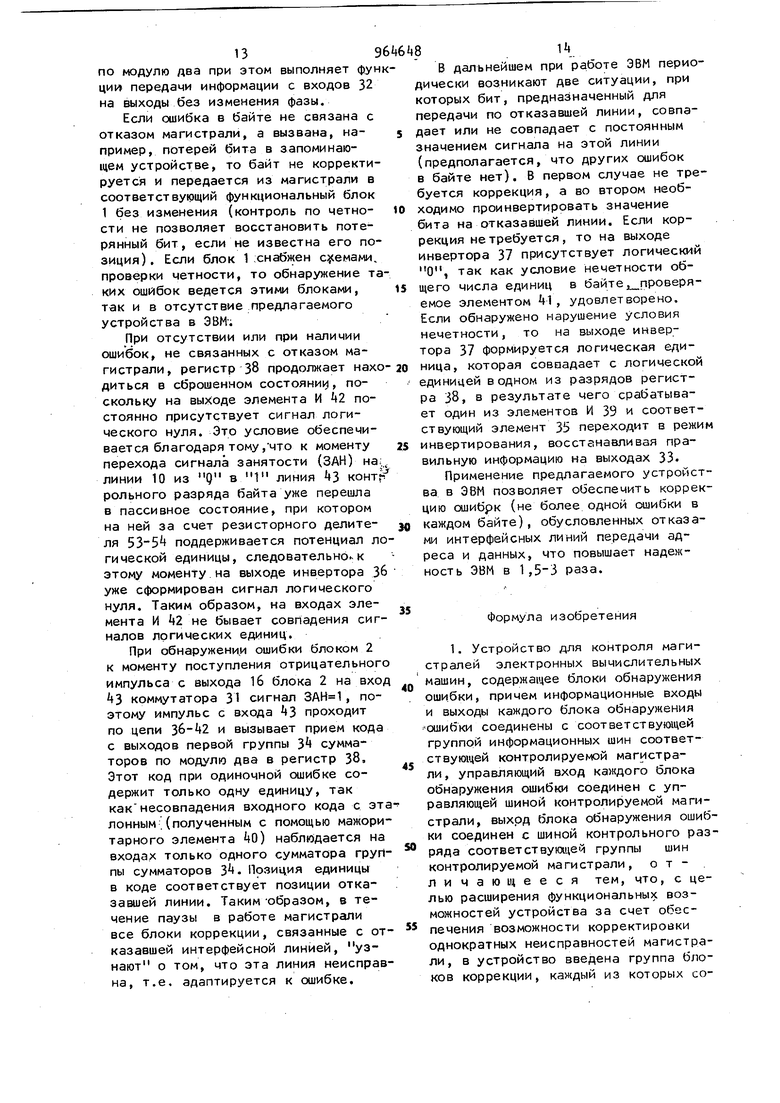

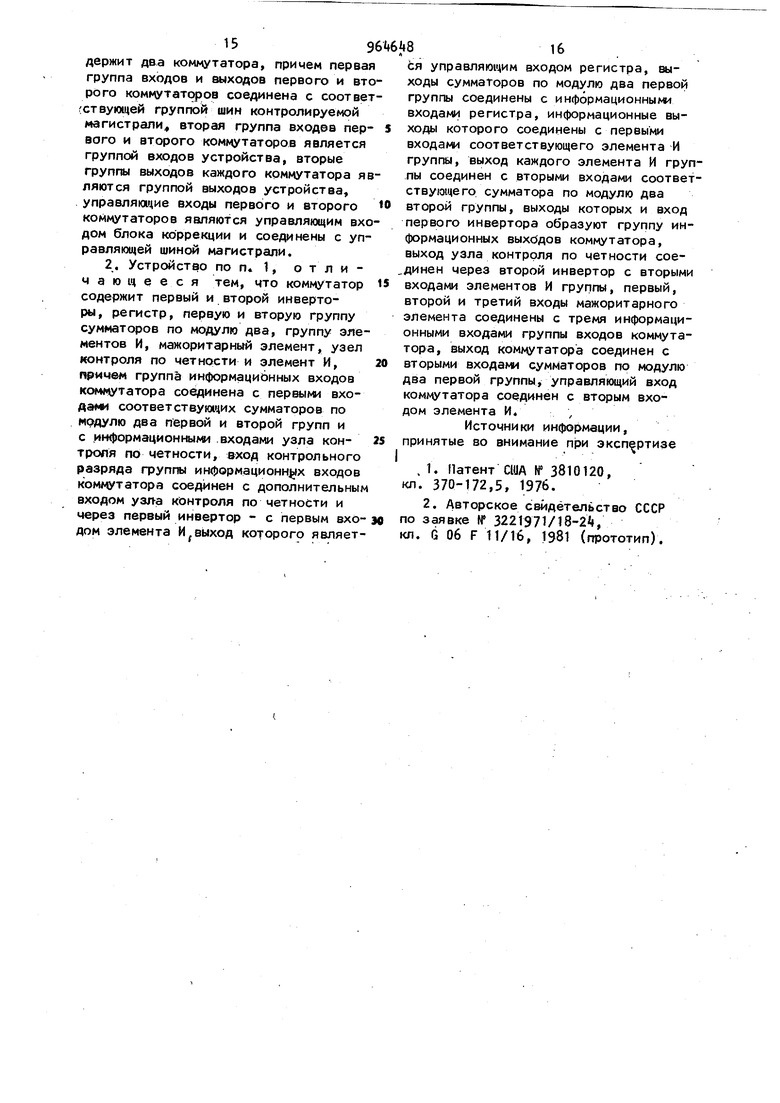

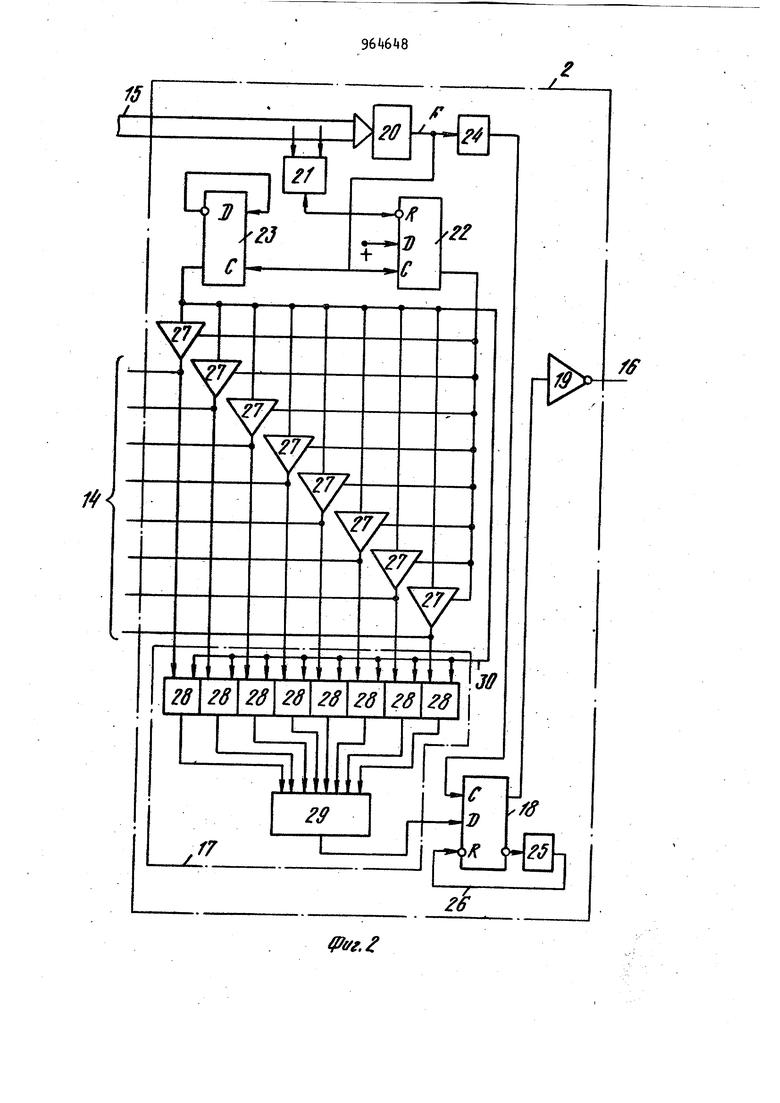

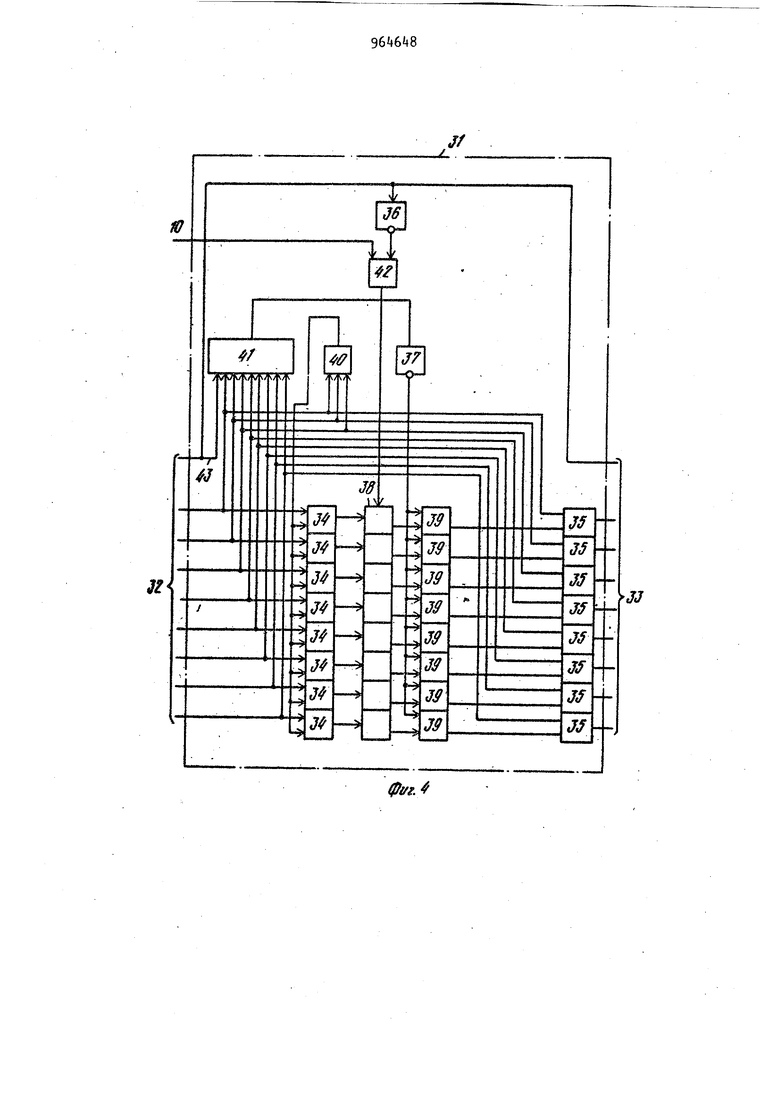

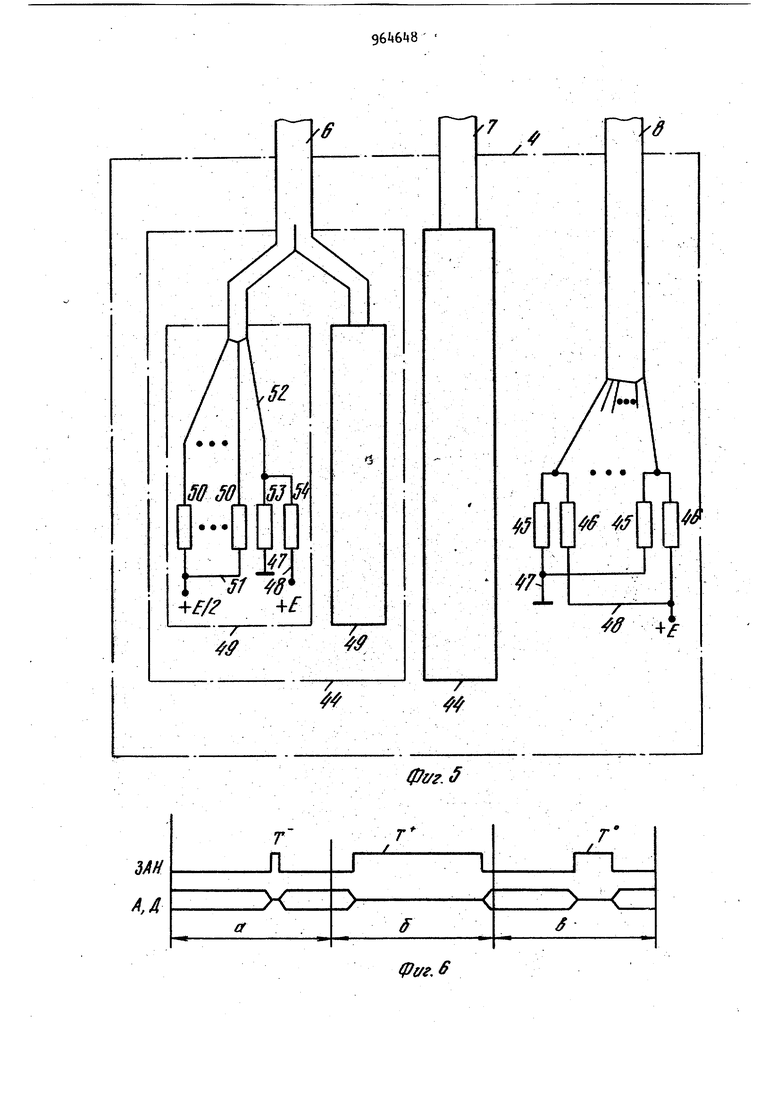

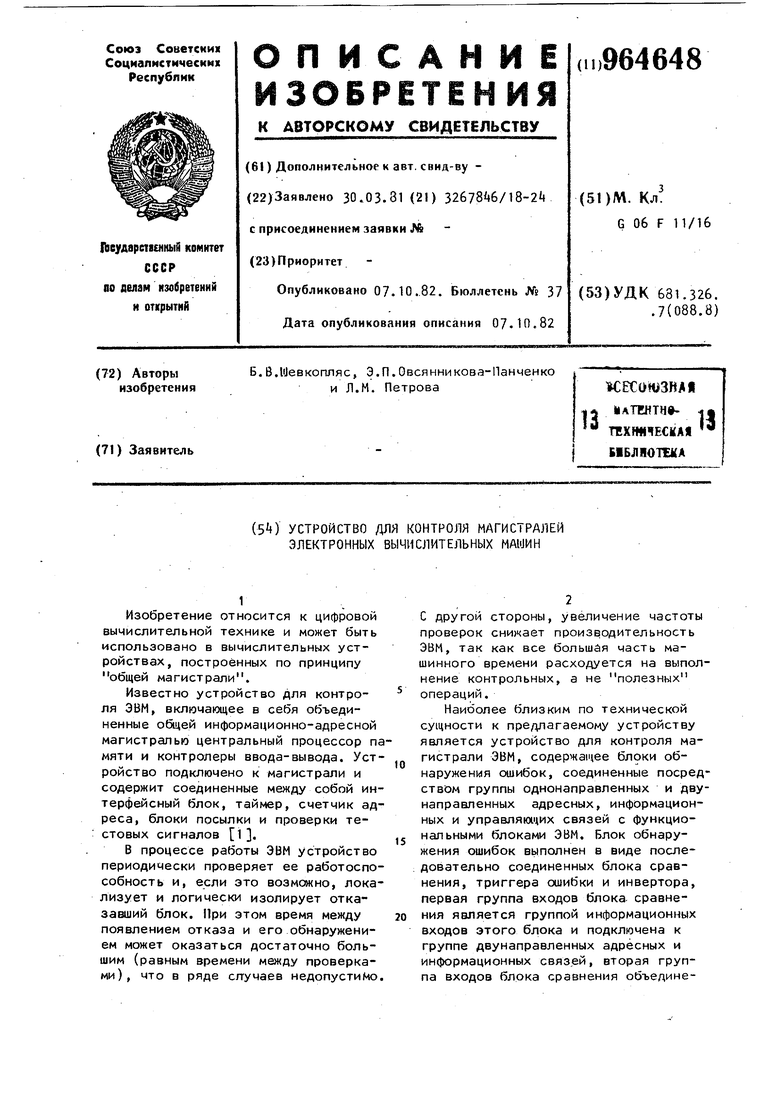

На фиг. 1 изображена функциональная схема части ЭВЙ, поясняюсцая назначение устройства для контроля ма5 гистрали; на фиг. 2 функциональная схема блока обнаружения ошибки; на фиг. 3 функциональная схема блока коррекции; на фиг. k - функциональная схема логического блокаj на фиг. 5 - электрическая схема согласу ющего блока; на фиг. 6-9 - временные диаграммы захвата магистрали, поясняющие принцип построения предлагаемого устройства. Для пояснения функционального на значения и алгоритма работы устройства на фиг. 1 показана часть ЭВМ, включающая в себя функциональные бло ки 1, блоки 2 обнаружения ошибок, блоки 3 коррекции и согласующие бло ки . Согласующие блоки k соединены между собой посредством группы одно направленных и двунаправленных связей 5 именуемых в дальнейшем магистралью. Магистраль 5 содержит группу двунаправленных адресных свя з.ей (шину адреса) 6, группу двунаправленных информационных связей (ш ну данных) 7 и группу направленных и двунаправленных управляющих связей (управляю1цую шину) 8. Фун1 :циональные блоки 1 подключены к управляющей шине 8 посредством связей 9. Управляющие входы 10 блоков 3 коррекции соединены с одной из связей управляющей шины 8. Группы магистральных выходов-входов 11 блоков 3 коррекции соединены с шина Nfti 6 и 7. Группы функциональных выходов 12 блоков 3 коррекции соединены с входами соответствующих функ циональных блоков 1. Группы функцио нальных входов 13 блоков 3 коррекци соединены с выходами соответствующих функциональных блоков 1. Группы информационных входов-выходов 1 блоков 2 соединены с шинами б и 7, группы управляющих входов 15 блоков 2-е шиной 8, выходы 16 блоков 2-е шинами 6 и 7. Функциональные блоки 1 являются стандартными блоками ЭВМ, такими как процессор, контролер, канал прямого доступа в память, постоянное запоминающее устройство, оперативное запоминающее устройство, адаптер магистралей и т.п. В этом примере реализации устройства предполагается, что адрес и данные имеют двухбайтовую структуру каждый байт состоит из восьми информационных и одного контрольного разряда, дополняю1чего до нечетного числа обсцее число единиц в байте. Число блоков 2 обнаружения ошибок в данном примере равно числу бай тов, составляющих адрес и данные. s 4 т.е. четырем. Каждый блок 2 предназначен для обнаружения ошибки в одном байте. Каждый блок 3 коррекции в данном примере имеет двухбайтовую структуру. Каждому функциональному блоку 1 соответствуют два блока 3 коррекции - один для коррекции адреса, второй - для коррекции данных. Блок 2 обнаружения ошибки (фиг.2) содержит последовательно соединенные блок 17 сравнения, триггер 18 ошибки, инвертор 19, а также элементы И 20 и Hi21, триггеры 22 и 23, элемент 2k задержки, элемент 25 задержки, выход которого соединен связью 26 с входом сброса триггера 18, а его вход - с выходом нулевого плеча этого триггера, и группу кабельных усилителей 27. Влок 17 сравнения содержит группу двухвходовых элементов ИСЮ1ЮЧАОДЕЕ ИЛИ 28, выходы которых соединены с входами элемента ИЛИ 29, выход которого является выходом блока сравнения. Первые входы двухвходовых элементов ИСКЛЮЧАЩЕЕ ИЛИ 28 соединены с выходами соответствующих кабельных усилителей 27 и являются группой информационных входов-выходов И блока 2 обнаружения ошибки. Вторые входы даухвходовых элементов ИСКЛЮЧАИ)1||ЕЕ ИЛИ 28 объединены и являются эталонным входом 30 блока 17 сравнения. Группы входов элементов И 20 и И 21 являются группой у правляюсцих входов 15 блока , выход элемента И 20 соединен с входами синхронизации триггеров 22 и 23;И, через элемент задержки, 2 - с входом синхронизации триггера 18. Выход элемента И 21 соединен с входом сброса триггера 22 j выход которого соединен с управляющими входами группы кабельных усилителей 27. Выход : нулевого плеча триггера 23 соединен с информационным входом этого триггера. Выход единичного плеча триггера 23 соединен с информационными входами группы кабельных усилителей 27 и с эталонным входом 30 блока 17 сравнения. Выход инвертора 19 является выходом 16 блока 2. На информационный вход триггера 22 подана логическая единица (+). Блок 3 коррекции (фиг. 3) содержит коммутаторы 31 Группа входов 32 коммутаторов 31 является группой магистральных входов-выходов 11 блока 3 и соединена с группой функциональных входов 13 этого блока. па выходов 33 коммутаторов 31 является группой функциональных выходов 12 блока 3 коррекции. Управляющие входы коммутаторов 31 объединены и являются управляющим входом 10 блока 3 коррекции. Коммутатор 31 (фиг. k) содержит первую 3 и вторую 35 группы сумматоров по модулю два, два инвертора 36 и 37, регистр ЗВ, группу элементов И.39, мажоритарный элемент kO, узел- контроля четности и элемент И k2. Информационные входы элемента 41 контроля четности соединены с пе вы1 входами групп 3 и 35 сумматор по модулю два. Вход +3 контрольного разряда элемента контроля четности соединен через инвертор Зб с первым входом элемента И 42, выход которого соединен с управляющим регистром 38. Вторые входы первой группы 3 сумматоров по модулю два соединены с выходом мажоритарного элемента 40 входы которого соединены с информационными входами узла 41 контроля четности. Выходы первой группы сумматоров 34 по модулю два соединены с информационными входами регистра 38, выходы, регистра 38 соединены с первыми входами группы элементов И 39, вторые входы элементов И 39 соединены с выходом второго инвертора 37, вход которого соединен с выходом узла 41 контроля четности. Выходы группы элементов И 39 соединены с вторыми .входами второй групп сумматоров 35 по модулю два. Информационные входы и вход контрольного разряда 43 узла 41 контроля четности являются входами 32 коммутатора 31. Выходы второй .группы 35 сумматоров по модулю два и вход контрольного разряда 43 элемента 41 контроля чет ности являются выходами 33 коммутатора 31. Второй вход элемента И 42 является управляющим входом 10 коммутатора 31. Согласующий блок 4. (фиг. 5) соде жит идентичные резисторные блоки 44 подключенные к шине 6 адреса и к ши не 7 данных, а также группу резисто ных делителей 43-46, подключенных средними точками к линиям,шины 8 управления. Все резисторные делители 4 46 включены параллельно между шиной земли- 47 и шиной питания (+Е) 48. Резисторный блок 44 содержит, два иде тичных байтовых резисторных блока 49. Блок 49 содержит восемь резисторов 50, вюпюченные между сигнальными линиями соответствукхией шины (6 или 7) и шиной 51,. на которую-подано напряжение, близкое к половине напряжения источника питания (+Е/2). Линия передачи 52 контрольного разряда подключена к средней точке резисторного делителя , включенного между шиной питания {+Е) 48 и шиной земли kj. Блоки k обеспечивают согласование волнового сопротивления линий связи магистрали 5 с активным сопротивлением Нагрузки для предотвращения отражений электрических сигналов от физических концов магистрали. Линии, подключенные к резисторам 50, обслуживаются кабельными усилителями с тремя устойчивыми состояниями (О, 1, Выключено). Остальные линии магистрали 5 обслуживаются кабельны.ми усилителями с открытым коллектором. В пассивном состоянии на этих линиях за счет резисторных делителей 45-46 и поддерживаются высокие положительные потенциалы (равные, например, +3,5 В при ,0В). Устройство работает следующим образом. С точки зрения обеспечения надежности ЭВМ магистраль является одним из наиболее уязвимых мест. Действительно, если одно из подключенных к ней устройств в результате неисправности кабельного приемника, кабельного усилителя (схемы управления усилителем) или замыкания постоянно выдает в одну из линий магистрали постоянный О или постоянную 1, то обмен по магистрали становится невозможным из-за искажения адресной, числовой, командной или управляющей информации. При работе ЭВМ в реальном времени эти искажения могут привести к выдаче на управляемый объект неправильных управляющих воздействий, в результате чего возможна возникновение аварийных.ситуаций. Решаемая устройством задача заключается в следующем. При появлении отказов в шине 6 адреса или (и) в шине 7 данных (а каждом из четырех байтов должно быть не более одного отказа) устройство обеспечивает быстрое их обнаружение аппаратными средствами. При обнаружении отказов блоки коррекции, связанные с отказавшими линиями, определяют местоположение этих линий и в дальнейшем с учетом проверки текущих байтов на нечетность, в необходи мых случаях инвертируют сигналы, пол ченные с отказавших линий. Работа блока 2 обнаружения ошибок основана на использовании пауз в раб те магистрали для ее проверки. В течение паузы в шины $ и 7 магистрали 5 посылаются тестовые сигналы (шина 8 не проверяется). По результатам считывания посланных в шины тестовых сигналов делается вывод об их работоспособности. На фиг. 6 показан типовой отрезок реальной временной диаграммы основных магистральных сигналов. Из диаграммы видно, что сигнал на линии занятости магистрали ЗАН, входящей в управляющую шину 8, периодически принимает единичное значение, что со ответствует свободному состоянию магистрали. При ЗАН-1 шина 6- адреса и шина Д 7 данных не ислользуются для передачи информации и в принципе можно использовать эти моменты времени для их проверки путем посылки и приема тестовых сигналов. О нако, период времени Т не достато чен для процедуры проверки, посколь ку очередное активное устройство в этом случае мгновенно захватывает магистраль после ее освобождения от предыдущего обмена. Если очередное активное устройство не готово мгновенно занять магистраль после ее-освобождения, например, из-за выполнения внутренней последовательности микрокоманд, то не занятое состояние магистрали (ЗАН-1) сохраняется в течение периода времени Т, достаточного для выполнения тестовой процедуры. Как показано ниже, существует простое логическое условие прогнозирования предстоящего свободного состояния магистрали с продолжительностью, большей или равной некоторой величине Если время обнаружения ошибки и адаптации к ней не превышает времени Т, то запуск уст ройства для контроля магистрали ЭВМ производится при обнаружении упомянутого логического условия. На фиг. 7 показана временная диаграмма захвата магистрали для случая мгновенного перехода магистрали от старого активного устройства к новому (промежуток времени а на фиг. 6). В исходном состоянии магистраль занята старым активным устройством. Новое активное устройство, желающее захватить магистраль, формирует логический О на одной из лиНИИ запросов SnPi (1 i i п), входящих в состав управляющей шины 8. По лучив по соответствующей управляющей линии сигнал разрешения РЗР| в виде логической единицы, йовое активное устройство снимает сигнал ЗПР и формирует логический О на управляющей линии подтверждения запроса ПТЗ, после чего снимается сигнал РЗР,-. Это состояние управляющих линий поддерживается до момента освобождения магистрали старым активным устройством. .При наличии условий ЗАН-1 и новое активное устройство формирует сигнал занятости (ЗАН-0), снимает сигнал ПТЗ(ПТЗ-1) и приступает к обмену информацией по магистрали 5. После окончания обмена новое активное устройство освобождает магистраль. Функция Е представляет собой упомянутое выше условие прогнозирования предстоящего свободного промежутка времени, большего или равного Т и определяется следующим образом . п Л ПТЗА . ЗПР ,где п - число линий запросов шины 8. Другими словами, функция Е принимает единичное значение при одновременном отсутствии сигналов занятости, подтверждения запроса и всех запросных сигналов для случая, показанного на фиг. 7, . На фиг. 8 показана временная диаграмма захвата магистрали, соответ-. ствующая промежутку времени б, отмеченному на фиг. 6. Ее отличие от диаграммы, проверенной на фиг. 7, состоит в TjDM, что к моменту формирования сигнала I1T3 () магистраль уже освобождается от предыдущего обмена. Функция е принимает единичное значение в некотором интервале времени., На фиг, 9 показана временная диаграмма захвата магистрали, соответствующая промежутку времени в, отмеченному на фиг. 6. Эта диаграмма получена из предыдущей (фиг. 8) перемещением отрицательного фронта сигнала на линии ЗПР| в направлении. указанном пунктирной стрелкой, до м мента, при котором ширина импульса Е становится минимально возможной для срабатывания логических элементов. Из диaгpaм fc( следует, что гара тированный интервал времени т оп-,, редеяяется суммой следующих временных интервалов: задержки.выдачи сиг нала разрешения в ответ на сигнал запроса; задержки формирования сигна 1а подтверждения запроса задержки формирования сигнала занятости. Указанные задержки известны для конкретной ЭВМ, следовательно известно и время Т, определяющее мак симально допустимую задержку срабатывания устройства для контроля магистрали. Общий алгоритм системы, включающей в себя устройство для контроля магистрали, следующий. 1°. При производится запуск устройства. 2°, Устройство формирует на шина адреса и данных код ll... (при сле дующем запуске - код 00...О, при сл дующем - код 11... 1 и т.д.). Код считывается устройством с ук занных шин. и сравнивается с эталонным: 11... 1 (00...0). k, В зависимости от результата сравнения триггер 18 ошибки или остается в сброшенном состоянии (при нормальной работе) или формирует им пульс, оповещающий соответствую1ций блок коррекции о наличии отказа. S. Блок коррекции при наличии о каза регистрирует местоположение отказавшей линии и в дальнейшем ис пользует эту информацию для коррекции байта. 69. Тестовая информация снимаетс с шин адреса и данных по отрицатель ному фронту сигнала подтверждения запроса (ПТЗ), после чего устройств переходит в состояние ожидания следующего запуска (п. 1). Блок обнаружения ошибок работает следующим образом. После включения ЭВМ при воздействии отрицательного импульса начальной установки, поступающего по цепи 8-15 на один из входов элемента И 21, сбрасывается триггер 22. Триггер 18 сбрасывается автоматичес ки по цепи 25-26, триггер 23 находится в произвольном состоянии. Нулевой сигнал с выхода триггера 22 з прещает работу кабельных усилителей 27, т.е. переводит их выходы в высокоомное состояние. Запуск устройства, как отмечалось выше, осуществляется при , т.е. при поступлении нужного сочетания управляющих сигналов на вход элемента И 20. Положительный фронт сигнала с выхода элемента И 20 переключает триггер 23 в противоположное состояние (триггер 23 включен в счетном режиме) и одновременно устанавливает в .единичное состояние триггер 22, так как на его информационный вход подана логическая единица (+). Единичный сигнал с выхода триг гера 22 переводит кабельные усилители. 27 в активное состояние (с низким выходным сопротивлением). Кабельные усилители 27 транслируют на линии 1 тестовые сигналы, совпадающие с сигналом на выходе триггера 23 Сигналы с линий 14 сравниваются блоком 17 сравнения с эталонным сигналом на входе 30 этого блока При правильной передаче сигналов на выходе элемента ИЛИ 29 формируется логический О, при неправильной передаче - логическая 1. После окончания переходных процёссоз ня выходе элемента ИЛИ 29 на синхронизируюсций вход триггера 18 поступает задержанный элементом 2k фронт сигнала F, в результате чего триггер 18 либо остается в сброшенном состоянии, либо (при ошибке) устанавливается в единичное состояние на время, определяемое задержкой элемента 25. В последнем случае на выходе 16 блока 2, подключенном к магистральной линии контрольного разряда соответствующего байта, формируется отрицательный импульс за счет срабатывания инвертора 19 соткрь1тым коллектором . Сброс триггера 22 производится сигналом , который поступает на второй вход элемента И 21. Блок коррекции (фиг. З) передает информацию с линий 13 в линии 11 без преобразования, а с линий 11 в линии 12 - через логические блоки 31. Коммутатор работает следующим образом, (фиг. А). В исходном состоянии регистр 38 сброшен (цепь начального сброса регистра не показана), сигналы с входов 32 передаются на выходы ЗЗ без преобразования, так как элементы И 39 закрыты нулевыми сигналами с регистра, а вторая группа сумматоров по модулю два при этом выполняет фун ции передачи информации с входов 32 на выходы без изменения фазы. Если ошибка в байте не связана с отказом магистрали, а вызвана, например, потерей бита в запоминающем устройстве, то байт не корректируется и передается из магистрали в соответствующий функциональный блок 1 без изменения (контроль по четности не позволяет восстановить потерянный бит, если не известна его позиция). Если блок 1 .снабжен с;(емами. проверки четности, то обнаружение та ких ошибок ведется этими блоками, так и в отсутствие предлагаемого устройства в ЭВМ; При отсутствии или при наличии ошибок, не связанных с отказом магистрали, регистр 38 продолжает нахо диться в сброшенном состояни, поскольку на выходе элемента И Д2 постоянно присутствует сигнал логического нуля. Это условие обеспечивается благодаря тому ,что к моменту перехода сигнала занятости (ЗАН) на; линии 10 из Q в 1 линия 3 контг рольного разряда байта уже перешла в пассивное состояние, при котором на ней за счет резисторного делителя поддерживается потенциал ло гической единицы, следовательно к этому моменту на выходе инвертора 36 уже сформирован сигнал логического нуля. Таким образом, на входах элемента И 2 не бывает совпадения сигналов логических единиц. При обнаружении ошибки блоком 2 к моменту поступления отрицательного импульса с выхода 16 блока 2 на вход 3 коммутатора 31 сигнал , поэтому импульс с входа проходит по цепи и вызывает прием кода с выходов первой группы 3 сумматоров по модулю два в регистр 38. Этот код при одиночной ошибке содержит только одну единицу, так какнесовпадения входного кода с эта лонным . (полученным с помощью мажоритарного элемента kO) наблюдается на входах только одного сумматора rpyriпы сумматоров 3. Позиция единицы в коде соответствует позиции отказавшей линии. ТакимОбразом, в течение паузы в работе магистрали все блоки коррекции, связанные с от казавшей интерфейсной линией, узнают о том, что эта линия неисправна, т.е. адаптируется к ошибке. В дальнейшем при работе ЭВМ периодически возникают две ситуации, при которых бит, предназначенный для передачи по отказавшей линии, совпадает или не совпадает с постоянным значением сигнала на этой линии (предполагается, что других ошибок в байте нет). В первом случае не требуется коррекция, а во втором необходимо проинвертировать значение бита на отказавшей линии. Если коррекция не требуется, то на выходе инвертора 37 присутствует логический О, так как условие Нечетности общего числа единиц в байте проверяемое элементом 41, удовлетворено. Если обнаружено нарушение условия нечетности, то на выходе инвертора 37 формируется логическая единица, которая совпадает с логической единицей водном из разрядов регистра 38, в результате чего срабатывает один из элементов И 39 и соответствующий элемент 35 переходит в режим инвертирования, восстанавливая правильную информацию на выходах 33. Применение предлагаемого устройства в ЭВМ позволяет обеспечить коррекцию ошибрк (не более одной ошибки в каждом байте), обусловленных отказами интерфейсных линий передачи адреса и данных, что повышает надежность ЭВМ в 1 , раза. Формула изобретения 1. Устройство для контроля магистралей электронных вычислительных машин, содержащее блоки обнаружения ошибки, причем информационные входы и выходы каждого блока обнаружения ошибки соединены с соответствующей группой информационных шин соответствую1чей контролируемой магистрали, управляющий вход каждого блока обнаружения ошибки соединен с управляющей шиной контролируемой магистрали, выхрд блока обнаружения ошибки соединен с шиной контрольного разряда соответствующей группы шин контролируемой магистрали, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности корректировки однократных неисправностей магистрали, в устройство введена группа блоков коррекции, каждый из которых содержит два коммутатора, причем первая группа входов и выходов первого и второго комг татороа соединена с соответ(ствуихцей группой шин контролируемой магистрали, вторая группа входов первого и второго коммутаторов является группой входов устройства, вторые группы выходов каждого коммутатора являются группой выходов устройства, управлякяцие входы первого и второго коммутаторов являются управляющим входом блока коррекции и соединены с управляющей шиной магистрали.

группа информациЬнных входов коммутатора соединена с первыми вхоAafiM соответствуюсцих сумматоров по модулю два первой и второй групп и с информационными .входами узла контроля по четности, вход контрольного разряда группы инфopмaциoннJ x входов коммутатора соединен с дополнительным входом узла контроля по четности и через первый инвертор - с первым входом элемента Невыход которого является управляющим входом регистра, выходы сумматоров по модулю два первой группы соединены с информационными входами регистра, информационные выходы которого соединены с первыми входами соответствующего элемента И группы, выход каждого элемента И группы соединен с вторыми входами соответствующего сумматора по модулю два второй группы, выходы которых и вход первого инвертора образуют группу информационных выходов коммутатора, выход узла контроля по четности соеинен через второй инвертор с вторыми входами элементов И группы, первый, второй и третий входы мажоритарного элемента соединены с тремя информационными входами группы входов коммутатора, выход коммутатора соединен с вторыми входами сумматоров по модулю два первой группы, управляющий вход коммутатора соединен с вторым входом элемента И,,

Источники информации, принятые во внимание п(эи экспертизе

1,Патент США If 3810120, кл. 370-172,5, 1976.

л. G Об F 11/16, 1981 (прототип).

ф1/г f

/7

/./

/.fi

1

10

32

35

/

Я

//

f/

зг

jj

j

//jФиг.З

Д

JJ

/

Т

JL

х:

ф1/г.

г

г

Фиг,

Авторы

Даты

1982-10-07—Публикация

1981-03-30—Подача