ел to ел vj

li

4

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств.

Цель, изобретения - повышение достоверности хранимой информации.

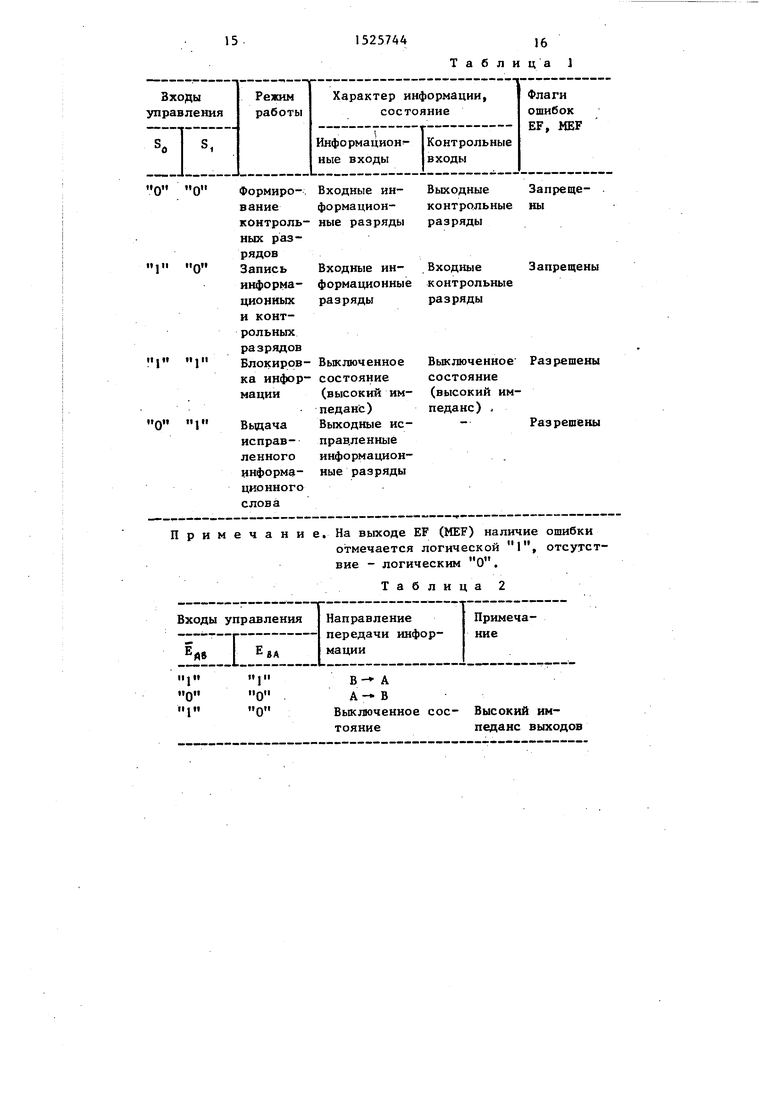

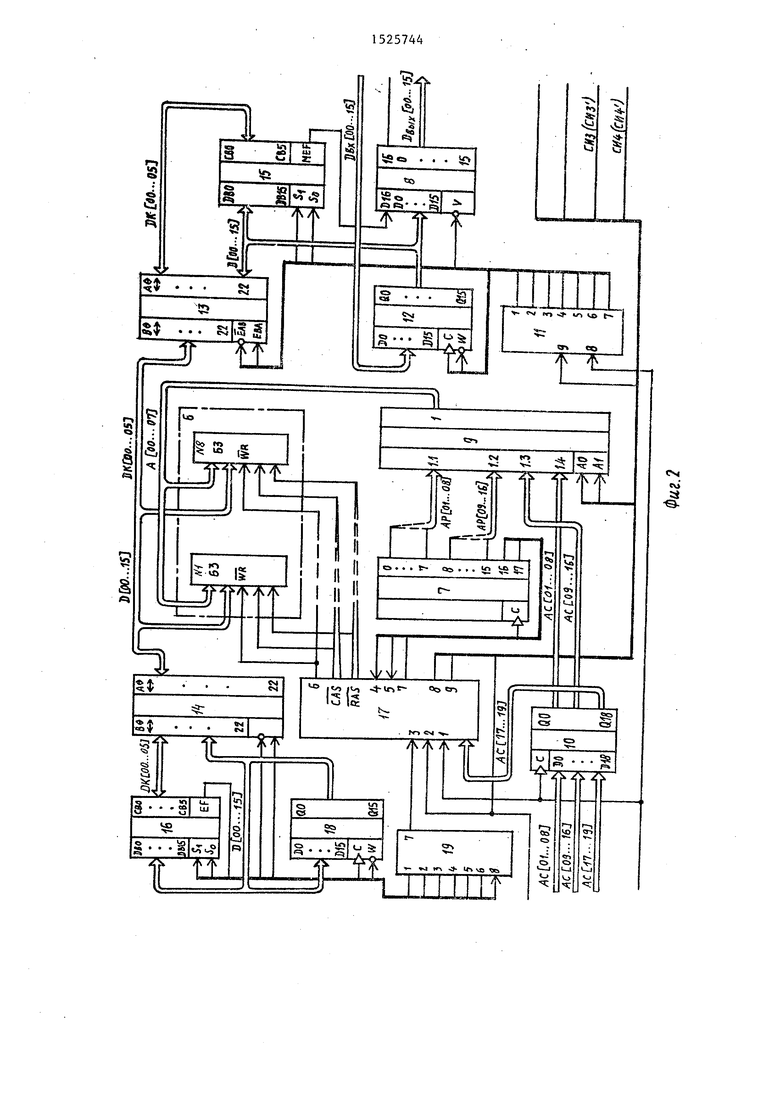

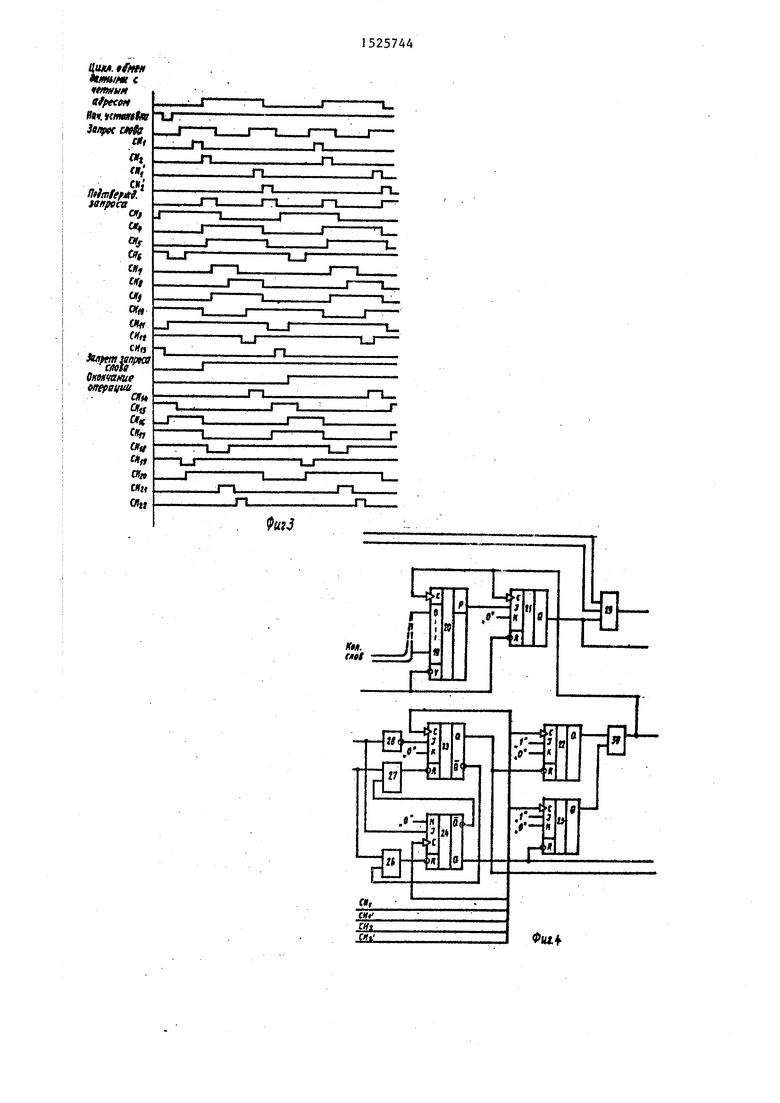

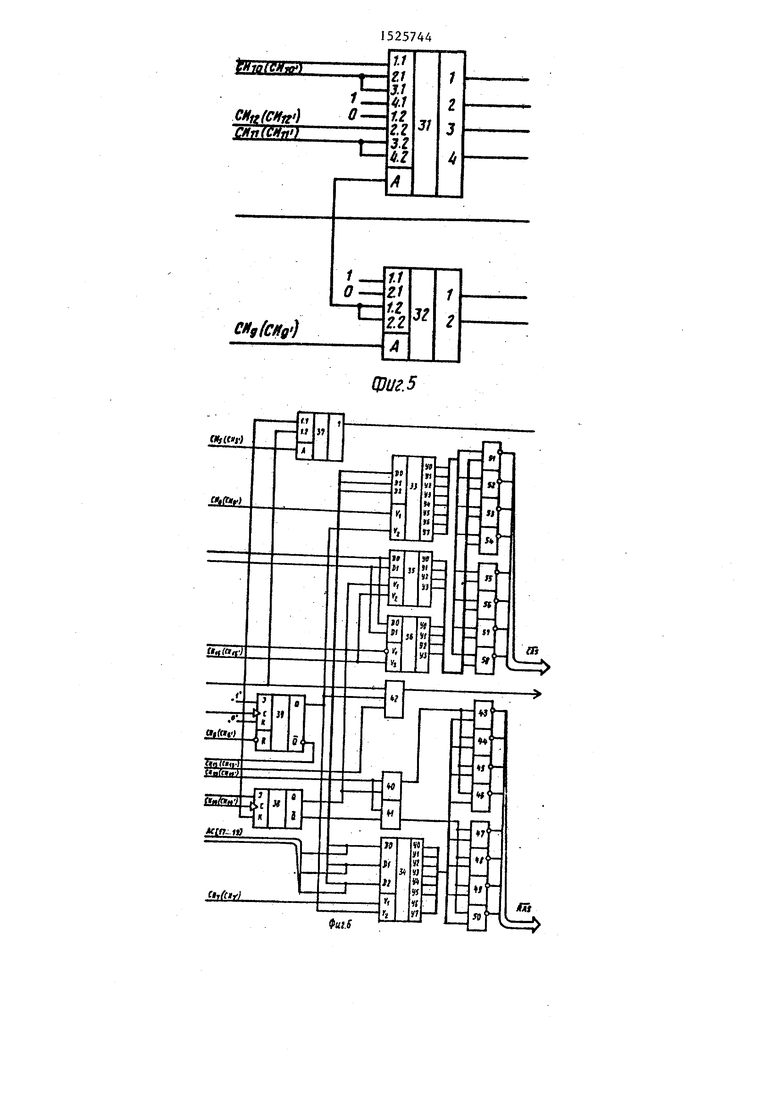

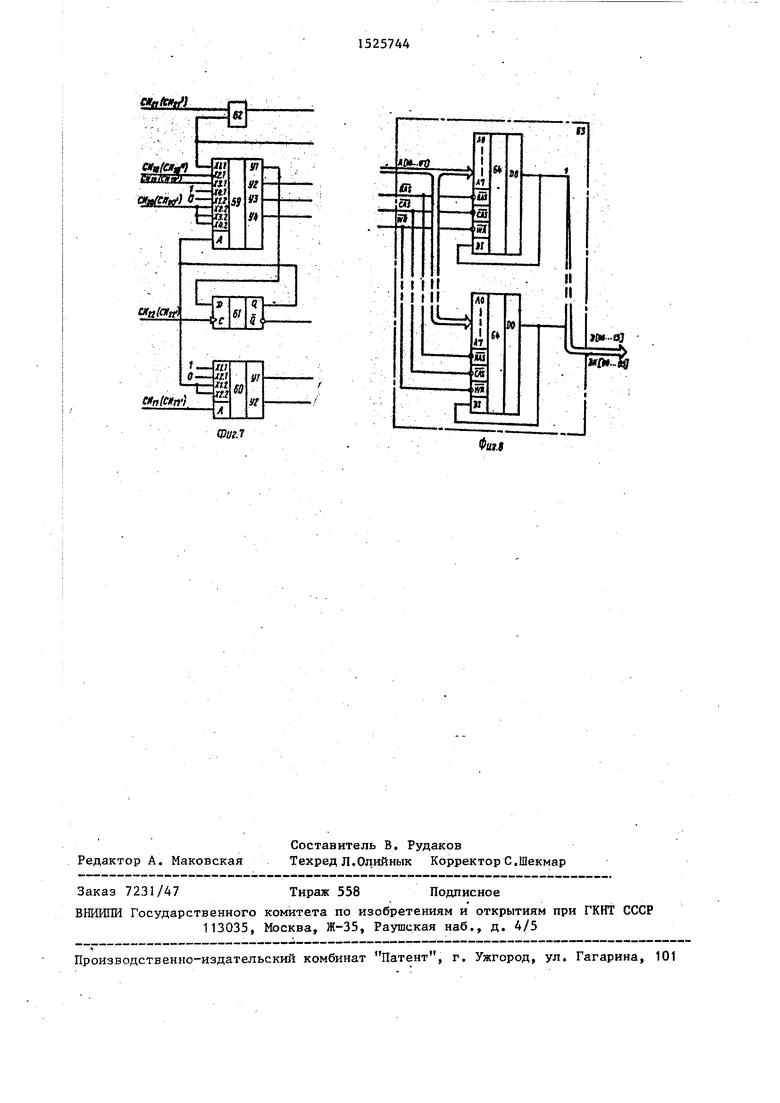

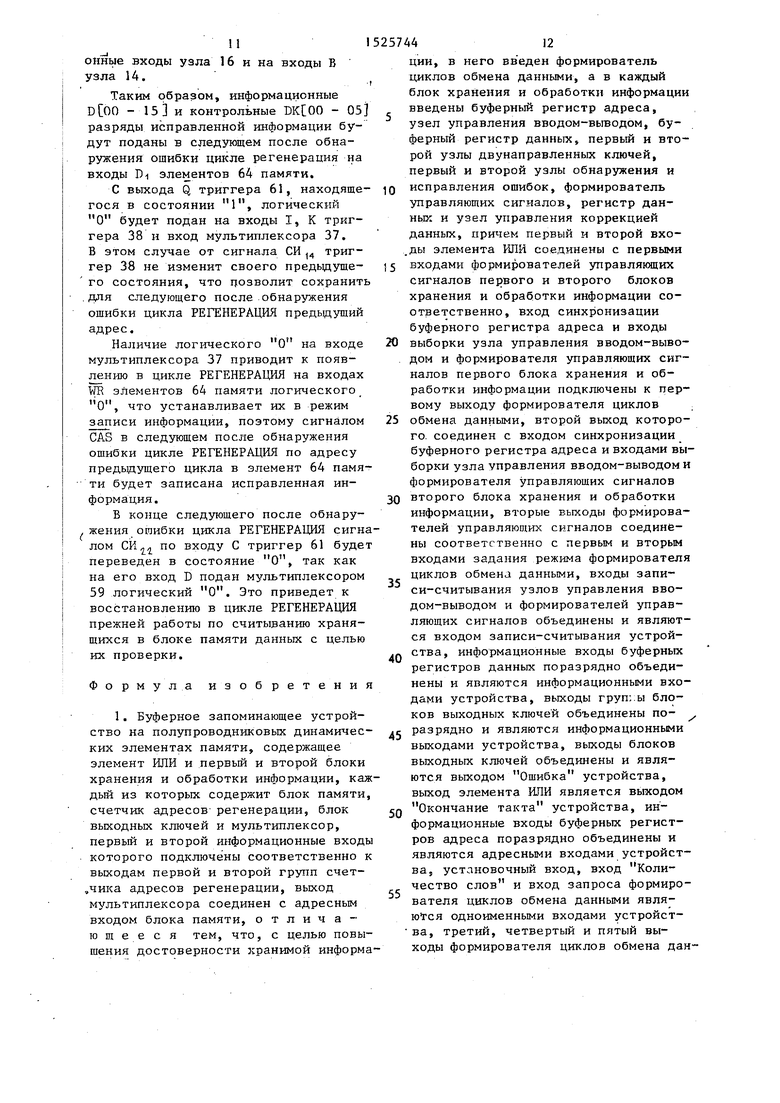

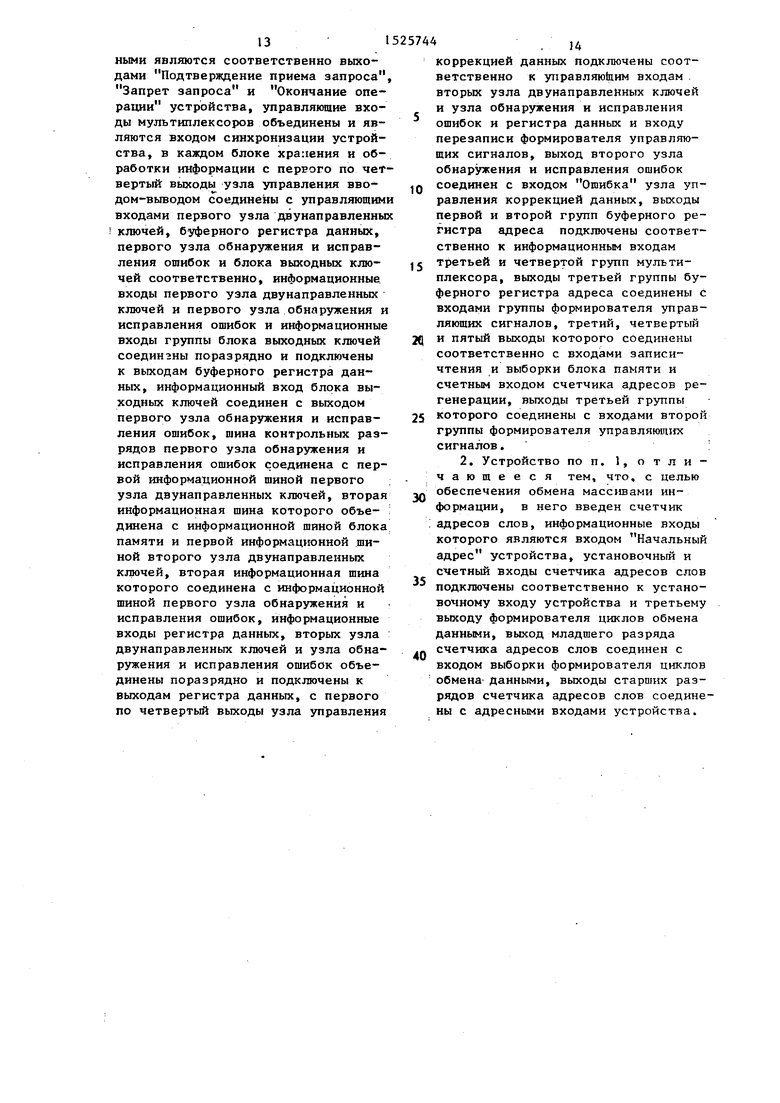

На фиг. 1 изображена структурная схема буферного запоминающего устройства на полупроводниковых динамических элементах памяти; на фиг. 2 - структурная схема каждого из блоков хранения и обработки информации; на фиг. 3 - временные диаграммы работы устройства; на фиг. 4 изображена структурная схема формирователя циклов обмена данными; на фиг. 5 - то же, узла управления вводом/выводом; на фиг. 6 - то же, формирователя управляющих сигналов; на фиг. 7 - то же, узла шравления коррекцией данных; на фиг. 8 - то же, и модуля памяти (фиг. 8).

Буферное запоминающее устройство на полупроводниковых динамических элементах памяти (фиг. 1) содержит элемент ИЛИ 1, регистр 2 адреса Слов, формирователь 3 циклов обмена данными, первый блок А хранения и обработки информапии, имеющей четный адрес, и блок 5 хранения и обработки информации, имеющей нечетный адрес. Каждый из блоков 4 и 5 (фиг. 2) содержит блок 6 памяти, счетчик 7 адресов регенерации, блок 8 выходных ключей, мультиплексор 9, буферный регистр 10 адреса, узел 11 управления вводом/выводом, буферный регистр 12 данных, первый 13 и второй 14 узлы двунаправленных- ключей, первый 15 и второй 16 узлы Обнаружения и исправления ошибок, формирователь 17 управляющих сигналов, регистр 18 данных и узел 19 управления коррекцией данных.

Формирователь 3 циклов обмена данными (фиг. 4) содержит счетчик 20, пять 1К-триггеров 21-25, два элемента 2И 26 и 27, элемент НЕ 28, элемент ЗИ 29 и элемент 2ИЛИ 30.

Узел 11 управления вводом/вьшо- дом (фиг. 5) содержит два мультиплексора 31 и 32.

Формирователь 17 (фиг. 6) содер- жит четыре депгафратора 33-36, муль- типлексор 37, два 1К-триггера 38 и 39, два элемента 2И 40 и 41, элемент ЗИ 42 и шестнадцать элементов 2Ш1И-НЕ 43-58.

0

5

0

5

0

5

0

5

0

5

Узел 19 управления коррекцией данных (фиг, 7) содержит два мультиплексора 59 и 60, D-триггер 61 и элемент 2И 62.

Блок 6 (фиг. 8) содержит модули 63 памяти, состоящие из динамических элементов 64 памяти.

Синхроимпульсы, поступающие на входы элементов устройства, деляется на две группы:

синхроимпульсы для обработки данных с четным адресом СИ

синхроимпульсы для обработки данных с нечетным адресом СИ ,- СИ

Устройство имеет два цикла: ОБМЕН ДАННЫМИ и РЕГЕНЕРАЦИЯ. Для каждого из блоков 4, 5 эти циклы следуют один за другим. При этом если в одном из блоков 4, 5 установлен цикл ОБМЕН ДАННЫМИ, то в другом блоке в это время установлен цикл РЕГЕНЕРАЦИЯ и наоборот.

В цикле ОБМЕН ДАННЫМИ происходит запись информации в. блок памяти или ее считьшание из него. Информация, записьгеаемая в блок памяти, предварительно кодируется с применением модифицированного кода Хэмминга с шестнадцатью информационными и шестью контрольными разрядами.

Регенерация информации осущест вляется по строкам. В каждом цикле РЕГЕНЕРАЦИЯ для установленного ад- реса строки регенерируется только половина емкости одного блока 6, что, с одной стороны, позволяет уложиться в максимально допустимый период регенерации, заданными элементами 64 памяти, а с другой, - уменьшить общее потребление по питанию.

Кроме того, в каждом цикле РЕГЕНЕРАЦИЯ вьmoJ Iняeтcя проверка по коду Хэмминга очередного слова, хранящегося в блоке 6 1 амяти. При обнаружении ошибки в следующем цикле РЕГЕНЕРАЦИЯ для этого блока памяти искаженное слово исправляется.

Блок 6 памяти каждого из блоков 4, 5 состоит из полупроводниковых динамических элементов 64 памяти емкостью 64 К. Элемент 64 памяти имеет 8 адресных входов. Для выбора любой из ячеек элемента 64 памяти сначала необходимо подать восьмиразрядный код адреса строки, фиксируемый сигналом RAF, а затем восьмиразрядный код адреса столбца, фиксируемый

сигналом , В режиме считывания (на входе WB - логическая 1) выход элемента 64 памяти переходит из состояния с высоким импедансом в активное состояние под управлением сигнала CAS,

Для обмена информацией с запоминающим устройством (ЗУ) необходимо предварительно записать в регистр 2 начальный адрес, а в счётчик 20 - количество в обратном коде слов, подлежащих обменуо Запись осуществляется путем кратковременной подачи логического уровня О на вход Начальная установка. Кроме того на входе Зарись/Считывание устанавливается логический О, если информация будет записываться в ЗУ, логическая , если необходимо вывести информацию из ЗУ.

Обмен информацией инициируется сигналом логическая 1 на входе Запрос слова устройства. Пока запроса слова нет, триггеры 23, 24 (фиг. А) удерживаются в состоянии О по входам R, При появлении логической 1 на входе Запрос слова на входах R этих триггеров устанавливается логическая 1 и один из них, имеющий на своем входе I логическую 1, будет переведен синхроимпульсом (си) по входу С в состояние 1, Поскольку младший разряд адреса слова подключается в входу I одного из этих триггеров непосредственно, а другого - через элемент НЕ,при четном начальном адресе слова в состояние 1 будет переведен сигналом СИ 1 (фиг, 3) триггер 23, В этом случае вся последующая работа по обмену запрошенного слова будет выполняться узлами и элементами, относящимися к блоку 4 с четным адресом.

Логическая 1 с выхода Q триггера 23:

запишет по входу С в буферный регистр 10 адреса (фиг, 2) началь- ньй адрес слова;

. в режиме, записи запишет по входу С в буферньй регистр 12 данных код данных, подлежащий записи в блок памяти;

переведет триггер 39-(фиг, 6) по входу С в состояние

будет подана на вход R триггера Й2,

1

525744, 6

В результате сигнал СИ переведет по входу С в СОСТОЯНИЕ . I триггер 22, С выхода Q триггера 22 логическая 1 поступит на входы С счетчика 20 и регистра 2 адреса слова и изменит их состояние на единицу. Этот же сигнал будет подан на вьжод Подтверждение приема запроса устройства, разрешая тем самьм снять логическую 1 с выхода Запрос слова и затем установить запрос следующего слова.

Когда с выхода Запрос слова логическая 1 будет снята, триггеры 23 и 22 будут установлены по .входам R в состояние О сигналами логического О,

Уст.ановившийся в состояние 1 20 триггер 39 (фиг. 6) подает логичес10

15

0

5

кую 1 на входы разрешения дешифраторов 33, 34, На выходе этих дешифраторов под управлением сигналов СИ-,, СИ g будут сформированы сигналы 5 управления блоком 6 RAS, CAS для модуля 63 памяти, определенного старшими разрядами адреса слова АС 17 - 191.

Адреса строк и столбцов А ОО - 07} элементов 64 памяти формируют мультиплексором 9, управляемым сигналами СИ, СИ д. В цикле ОБМЕН ДАННЫМИ разряды адреса слова АС tOl -08 образуют адрес строки, а разряды АС 09 - 16 - адрес столбца.

Режим работы элементов 64 памяти ; (фиг, 8) по входу WR задается мультиплексором 37, управляемьи сигналом CHj, В цикле ОБМЕН ДАННЫМИ .на входы WR элементов 64 подается сигнал с входа Запись/Считывание, Если на этом входе логическая 1, то по сигналу CAS с выбранного моду- с ля 63 памяти из ячеек, определенных адресом строки и столбца, будет считана информация. Если же на входе . Запись/Считывание - логический О, то по сигналу CAS в выбранный модуль 63 памяти в ячейки, определенные адресом строки и столбца, будет записана информация.

При записи информации в блок 6 с выхода буферного регистра 12 данных код данных поступает на информационные входы узла 15 и входы узла 13 (фиг, 2), Алгоритмы их работы приведены в табл, 1 и 2 соответственно.

0

5

В режиме записи узел 15 по разрядам кода данных, поданного на его информационные входы, в период, определяемый сигналом СИ,,1, формирует контрольные разряды DK СрО - 053, ; которые, как и информационные, подаются на входы узла 13. Сигнал СИ поступает на входы управления S, S. узла 15 мультиплексор 31,

Узел 13 в цикле РЕГЕНЕРАЦИЯ закрыт, а в цикле ОБМЕН ДАННЬМИ открыт Направление передачи информации зависит от режимаJ В режиме записи узел 13 передает информацию от вы- водов А к выводам В, обеспечивая те самым подачу как информационных D 00 - 15, так и контрольных DK ОО - 05 разрядов на входы D элементов 64 памяти.

В случае считывания информации и блока памяти на управляющие входы Sp, S, узла 15 через мультиплексор 31 подаются, соответственно, сигналы СИ, CHj.. Поскольку на управляющие входы узла 13 в цикле ОБМЕН ДАННЬМИ подается в этом режиме с входа Запись/Считывание через мультиплексор 32 логическая 1, то он будет передавать информацию от выводов В к выводам А.

Информация - 15, - 05, считанная в цикле ОБМЕН ДАННЫМИ с модуля 63 через узел. 13, подается на информационные и контрольны входы узла 15. Последний в конце цила ОБМЕН ДАННЬМИ по сигналу СИ,, записывает поданную на его входы информацию.

По окончании цикла ОБМЕН ДАННЫМИ узел 13 закрывается, а узел 15 сигналом СИ переводится в режим выдачи исправленной информации, которая появляется на его информационных входах.

Исправленная информация через блок и постзшает на выходы устройства. Блок 8 управляется сигналом СИ, и открьшается на время выдачи узлом 15 исправленной информации.

Если узлом 15 будет обнаружена многократная неустранимая ошибка, то информация об этом также будет выведена через блок 8 на выход Ошибка устройства.

Выходные данные, считанные из блока 6, и информация о неустранимой многократной ошибке стробиру- ется сигналом, снимаемым с выхода

Q

15257448

элемента ЗИ 42 (фиг, 6). Стробиру- ющий сигнал формируется с помощью сигнала СИ 13 только в режиме счи- тьтания.

Сигналом СИ j триггер 39 переводится по входу R из состояния 1 О

в состояние

из состояния

что является окон0

5

0

0

5

0

5

чанием рабочего цикла, запушенного первым появлением логической 1 на входе Запрос слова устройства.

При запросе второго слова аналогично описанному выше будут рабо- . тать триггеры 24, 25 и блок 5. Обмен словами будет происходить попеременно с каждым из блоков 4, 5. Если запрос слова будет выставляться не позже, чем это показано на фиг. 3, обмен словами будет происходить в каждом цикле.

Синхросигналы СИ - назначенные для управления блоком 5 с нечетным адресом, на фиг. 3 не,показаны. Их структура полностью соответствует синхросигналам СИ 3 и СИ .2.

При запросе последнего слова, после перехода в состояние 1 триггера 22 (если последнее слово имеет четный адрес) или триггера 25 (если последнее слово имеет нечетный адрес), логическая 1 с выхода Q через элемент 21 ШИ 30 поступит на вход С триггера 21, Поскольку в этом случае на вход I этого триггера с выхода счетчика 20 (слов) подается логическая 1, то триггер 21 будет переведен в состояние 1. Появляющаяся при этом на выходе Запрет запроса слова логическая 1 запрещает запрос нового слова. После возвращения триггера 39 в состояние О на выходе Окончание операции появляется логическая 1, что свидетельствует об окончании обмена массивом информации.

Регенерация информации, хранящейся в элементах 64 памяти, осуществля- ется для каждого адреса строки сигналом RAS. Адреса строк формируются разрядами О - 7 счетчика 7 адресов регенерации. Разряды 8 - этого же счетчика формируют адреса столбцов, а разряды Ll6, 17} - адреса элементов 64 памяти.

Сигналы RAS, используемые для регенерации, формируются с помощью сигналов СИ,5 и триггера 38. При отсутствии ошибок в Словах на входы I и К этого триггера подана логическая 1 и он работает как обычный счетный триггер по входу С от сигналов СИ „ Когда на выходе Q триггера 38 логическая I, под воздействием сигнала СИ,j элементом 2И 40 будет сформирован сигнал RAS для модулей 63 памяти ffffl - 4. Если логическая 1 будет на выходе Q, сигнал RAS будет подан на модули 63 памяти №№ 5-8.

Счетчик 7 адресов регенерации управляется по входу С с выхода Q триггера 38. Смена адреса регенерации происходит при переходе триггера 38 из состояния О в состояние 1. Обратный переход триггера 38 н меняет адреса регенерации. Таким образом, для установленного счетчиком 7 адреса регенерации сначала формируется сигнал RAS для модулей 63 памяти №№ 1-4, а затем для модулей 63 № 5-8. .

В отличие от сигнала RAS сигнал

CAS, формируемый в цикле регенерация, подается одновременно только на один из модулей 63 памяти. Формируется сигнал CAS де шифраторами 35, 36, управляемыми триггером 38 и разрядами 16, 17J счетчика 7 адресов регенерации. Временный интервал CAS задается сигналом СИ, .

Пока нет ошибок в словах, хранимых в бло1се 6, в цикле РЕГЕНЕРАЦИЯ на входы WR элементов 64 памяти подается через мультиплексор 37 логи- ческая 1, поэтому с модуля 63 па- (Мяти, на который поступил сигнал CA считывается одно слово по адресу, определенному счетчиком-7 адресов регенерации. Так как последний последовательно перебирает все адреса блока 6, то в циклах РЕГЕНЕРАЦИЯ все слова периодически считываются с целью их проверки.

Проверка слов по коду Хэмминга осуществляется узлом 16. Считанные с модуля 63 памяти данные вСОО-151 и контрольные разряды DK 00-05 подаются на входы узла 16 через узел 14,. Последний в цикле ОВМЕН ДАННЫМИ закрыт сигналами, поступающими на его управляющие входы с мультиплексора 60. В цикле РЕГЕНЕРАЦИЯ узел 14 открыт, а направление передачи информации зависит от наличия ошибки в слове, проверенном в предьдущем цикле РЕГЕНЕРАЦИЯ. Если ошибки не

было, то узел 14 передает кнформацик от входов А к входам В;

На управляннцие входы S,, S, узла 16 при отсутствии ошибки в предыдущем слове подаются мультиплексором 59 соответственно сигналы СИ и СИ,. Сигнал СИ,з в конце цикла РЕГЕНЕРАЦИЯ переводит узел 16 в режим

Q записи информации, имеющейся на его входах. По окончании записи на выходе этого узла появляется информация о наличии или отсутствии огаибки в проверяемом слове.

5 Если ошибки нет,-то логический о с выхода узла 16 через мультиплексор 59 будет подан на вход D . триггера 61. Сигнал СИ поступающий на вход С этого триггера, оставит

0 его в прежнем положении, что не изменит последующую работу блока 4 или 5.

При обнаружении ошибки на выходе 5 узла 16 появится логическая 1, ко- .торая разрешит сигналу СИ, через элемент 2И 62 записать в регистр 18 по входу С исправленную во втором узле 16 информацию. Исправленная ин- 0 формация появляется на информационных выходах узла 16 при его переводе сигналом СИ{ в соответствующий режим.

На входе D триггера 61 в этом (. случае будет логическая 1, поэтому сигналом СИ.17 триггер 61 будет переведен в состояние 1. В результате:

узел 14 в следующем цикле РЕГЕНЕ- Q РАЦИЯ за счет появления, на кго управляющих входах.логической 1 будет передавать информацию от входов В к входам А;

к входу W регистра 18 и управля- 5 «пим входам В, о, узла 16 будет подключен сигнал СИ2д;

на вход-D триггера 61 будет подан логический О.

Сигнал СИю в следующем после об- Q наружения ошибки цикле РЕГЕНЕРАЦИЯ установит узел 16 в режим вьщачи контрольных разрядов - 05 Этот же сигнал, воздействуя на вход . W регистра 18, переведет его выход из состояния с высоким импедансом

5

в активное состояние, что приведет к появлению на его выходе записанной ранее исправленной информации Она будет подана на информаци 11

иные входы узла 16 и на входы В зла 14.

Таким образом, информационные - 15 и контрольные - 05 разряды исправленной информации будут поданы в следующем после обнаружения ошибки цшсле регенерация на входы Di элементов 64 памяти,

С выхода Q триггера 61, находящегося в состоянии 1, логический О будет подан на входы I, К триггера 38 и вход мультиплексора 37. В этом случае от сигнала СИ триггер 38 не изменит своего предьздуше- го состояния, что дозволит сохранить для следующего после обнаружения ошибки цикла РЕГЕНЕРАЦИЯ предьщущий адрес.

Наличие логического О на входе мультиплексора 37 приводит к появлению в цикле РЕГЕНЕРАЦИЯ на входах WE элементов 64 памяти логического О, что устанавливает их в режим записи информации, поэтому сигналом CAS в следующем после обнаружения ощибки цикле РЕГЕНЕРАЦИЯ по адресу предьщущего цикла в элемент 64 памяти будет записана исправленная информация.

Б конце следующего после обнару- жения ошибки цикла РЕГЕНЕРАЦИЯ сигна лом СИ по входу С триггер 61 будет переведен в состояние О, так как на его вход D подан мультиплексором 59 логический О. Это приведет к восстановлению в цикле РЕГЕНЕРАЦИЯ прежней работы по считыванию хранящихся в блоке памяти данных с целью их проверки.

Формула изобретения

1. Буферное запоминающее устройство на ползтроводниковых динамических элементах памяти, содержащее элемент ИЛИ и первый и второй блоки хранения и обработки информации, каждый из которых содержит блок памяти, счетчик адресов регенерации, блок выходных ключей и мультиплексор, первый и второй информационные входы которого подключены соответственно к выходам первой и второй групп счет- чика адресов регенерации, выход мультиплексора соединен с адресным входом блока памяти, о т л и ч а - ю щ е е с я тем, что, с целью повышения достоверности хранимой информа2574412

ции, в него вв еден формирователь циклов обмена данными, а в каждый блок хранения и обработки информации введены буферньй регистр адреса, узел управления вводом-вьгеодом, буферный регистр данных, первый и второй узлы двунаправленных ключей, первый и второй узлы обнаружения и

Q исправления ошибок, формирователь управляющих сигналов, регистр данных и узел управления коррекцией данных, причем первый и второй вхо- .ды элемента ИЛИ соединены с первыми

15 входами формирователей управляющих сигналов первого и второго блоков хранения и обработки информации соответственно, вход синхронизации буферного регистра адреса и входы

20 выборки узла управления вводом-выводом и формирователя управляющих сигналов первого блока хранения и обработки информации подключены к первому выходу формирователя циклов .

25 обмена данными, второй выход которого, соединен с входом синхронизации буферного регистра адреса и входами выборки узла управления вводом-выводом и формирователя управляющих сигналов

30 второго блока хранения и обработки информации, вторые выходы формирователей управляющих сигналов соединены соответственно с первым и вторым входами задания режима формирователя циклов обмена данными, входы записи-считывания узлов управления вводом-выводом и формирователей управляющих сигналов объединены и являются входом записи-считывания устрой.Q ства, информационные входы буферных регистров данных поразрядно объединены и являются информационными входами устройства, выходы груп;:ы блоков выходных ключей объединены по-

с разрядно и являются информационными выходами устройства, выходы блоков вьгходных ключей объединены и являются выходом Ошибка устройства, выход элемента ИЛИ является выходом

CQ Окончание такта устройства, информационные входы буферных регистров адреса поразрядно объединены и являются адресными входами устройства, установочный вход, вход Количество слов и вход запроса формирователя циклов обмена данными являются одноименными входами устройст- ва, третий, четвертый и пятый выходы формирователя циклов обмена дан35

55

ными являются соответственно выходами Подтверждение приема запроса Запрет запроса и Окончание операции устройства, управляющие входы мультиплексоров объединены и являются входом синхронизации устройства, в каждом блоке храаения и обработки информации с первого по четвертый выходы узла управления вводом-выводом соединены с управляющнми входами первого узла двунаправленных ключей, буферного регистра данных, первого узла обнаружения и исправления ошибок и блока выходных ключей соответственно, информационные входы первого узла двунаправленных ключей и первого узла обнаружения и исправления ошибок и информационные входы группы блока выходных ключей соединзны поразрядно и подключены к выходам буферного регистра данных, информационный вход блока выходных ключей соединен с выходом первого узла обнаружения и исправления ошибок, шина контрольных разрядов первого узла обнаружения и исправления ошибок соединена с первой информационной шиной первого узла двунаправленных ключей, вторая информационная шина которого объе- динена с информационной шиной блока памяти и первой информационной шиной второго узла двунаправленных ключей, вторая информационная шина которого соединена с информационной шиной первого узла обнаружения и исправления ошибок, информационные входы регистра данных, вторых узла двунаправленных ключей и узла обнаружения и исправления ошибок объединены поразрядно и подключены к выходам регистра данных, с первого по четвертый выходы узла управления

5

4

5

0

5

0

коррекцией данных подключены соответственно к управляюЬим входам вторьк узла двунаправленных ключей и узла обнаружения и исправления ошибок и регистра данных и входу перезаписи формирователя управляющих сигналов, выход второго узла обнаружения и исправления ошибок соединен с входом Ошибка узла управления коррекцией данных, выходы первой и второй групп буферного регистра адреса подключены соответственно к информационным входам третьей и четвертой групп мультиплексора, выходы третьей группы буферного регистра адреса соединены с входами группы формирователя управляющих сигналов, третий, четвертый и пятый выходы которого соединены соответственно с входами записи- чтения и выборки блока памяти и счетным входом счетчика адресов регенерации, выходы третьей группы которого соединены с входами второй группы формирователя управляюингх сигналов.:

2, Устройство по п. 1, отличающееся тем, что, с целью обеспечения обмена массивами информации, в него введен счетчик адресов слов, информационные входы которого являются входом Начальный адрес устройства, установочный и счетный входы счетчика гщресов слов подключены соответственно к установочному входу устройства и третьему выходу формирователя циклов обмена данными, выход младшего разряда счетчика адресов слов соединен с входом выборки формирователя циклов обмена- даиными, выходы старших разрядов счетчика адресов слов соединены с адресными входами устройства.

15

152574415

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств. Цель изобретения - повышение достоверности хранимой информации. Устройство содержит элемент ИЛИ 1, регистр 2 адреса слова, формирователь 3 циклов обмена данными, блок 4 хранения и обработки информации с четным адресом, блок 5 ханения и обработки информации с нечетным адресом. Каждый из блоков 4, 5 содержит блок памяти, счетчик адресов регенерации, блок выходных ключей, мультиплексор, буферный регистр адреса, узел управления вводом - выводом, буферный регистр данных, два узла двунаправленных ключей, узлы обнаружения и исправления ошибок, формирователь управляющих сигналов, регистр данных и узел управления коррекцией данных. 1 з.п. ф-лы, 8 ил., 2 табл.

Примечание,На выходе EF (МЕР) наличие ошибки

отмечается логической 1, отсутствие - логическим О.

Таблица2

IIIII

О О

В- А

А- В

Выключенное состояние

Высокий импеданс выходов

Фиг. 5

cnutentf}

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 4106108, кп | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1989-11-30—Публикация

1987-06-30—Подача