(54) УСТРОЙСТВО МНОГОКАНАЛЬНОГО ВВОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для обмена данными | 1974 |

|

SU506847A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

Изобретение относится к вычислитель ной технике и может быть использовано |при разработке вычислительных машин и j систем.

I Известны устройства многоканального ; ввода, содержащие селектор буферов кан |лов, блок сопряжения, связанный с входами устройства и буферами каналов, чающими блоки приема. Цель изобретения расширение функциональных возможностей I устройства, что; позволит осуществить приj ем информации по каналам с различными скоростями передачи данных, независимую от процессора компановку данных, повышение ско рости обмена с оперативной памятью проиессора, сокращение оборудования блоков приема.

Для осуществления цели предлагаемое устройство многоканального ввода содержит в селекторе буферов каналов шифратор адреса, буферный регистр, блок рассогласования, коммутатор состояш1я каналов, блок : занесения и блок управления, причем первый выход каждого блока приема соединен с соответствующим входом шифратора адреса и блока рассогласования, второй выход каждого блока приема соединен с соответствуй щим входом шифратора адреса и коммут тора состояния каналов, первый выход шн ipaTopa адреса соединен с установочным входом буферного регистра, управляющий , вход которого соединен спервым выходом I блока управления, второй выход которого : соединен с первым выходом устройства, а j третий выход - с первым входом блока зв несенчя, второй вход которого соединен со; вторым выходом устройства и первым вы-, уходом буферного регистра, а выход - с ci : ответствующими входами блоков приема, второй выход шифратора адреса соединен с соответствуюшшм входом коммутатора состояния каналов, выход которого соединен с соответствующим входом буферного регистра, второй вход которого соедииен .. ; с третьим выходом устройства, соответствующий вход которого соединен с первым входом блока управления, второй вход которого соединен с выходом блока рассогласования, а блок сопряжения связан с вхо-, 1дами коммутатора состояния каналов.

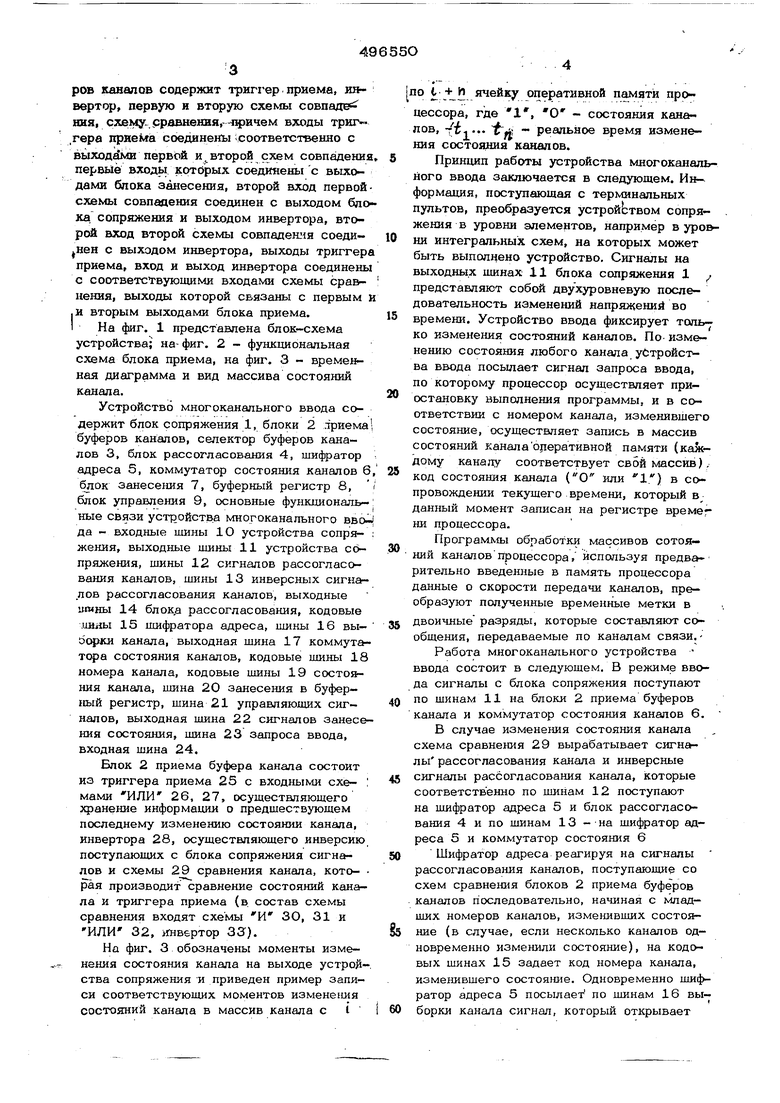

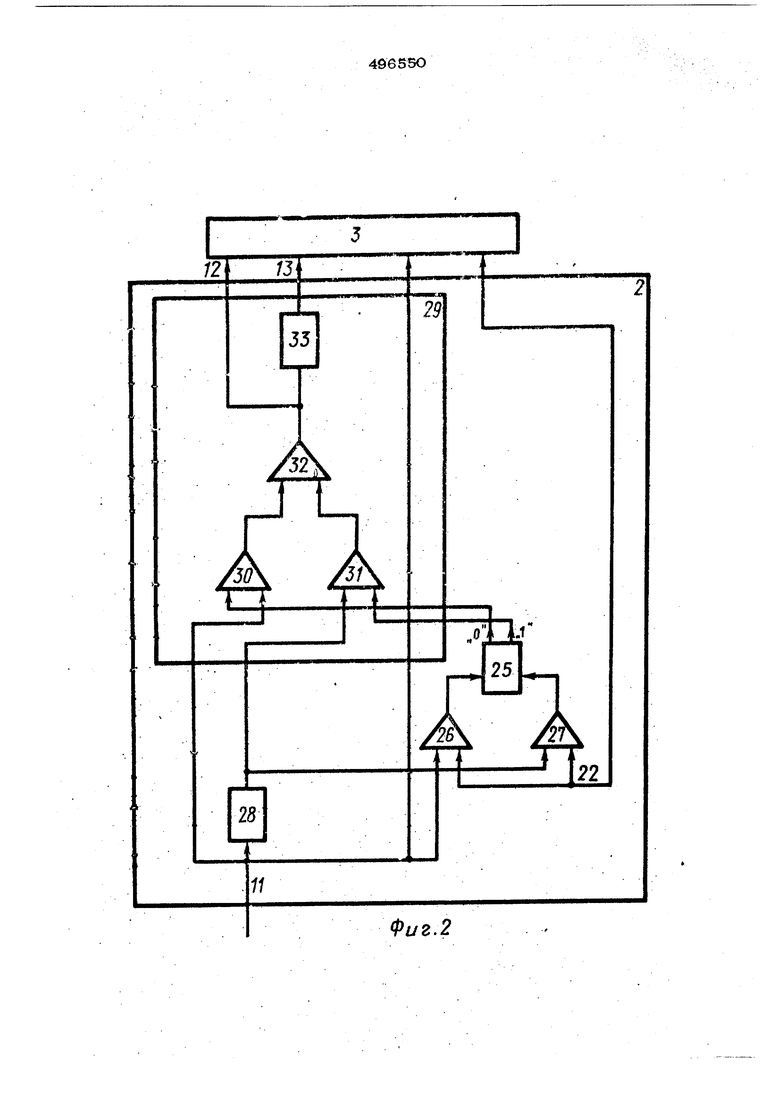

Кроме того, каждый блок приема буферов каналов содержит триггер приема, и вертор, первую и вторую схемы совпадар ния, схему., уравнения,--лричем входы триг ,гера приеК а соединены соответственно с выходами первой и второй схем совпадени первые входы которых соединены с выходами блока занесения, второй вход первой схемы совпадения соединен с выходом бло ка, сопряжения и выходом инвертора, второй вход второй схемы совпадения соедн нен с выходом инвертора, выходы триггер приема, вход и выход инвертора соединены с соответствующими входами схемы сравнения, выходы которой связаны с первым |И вторым выходами блока приема. I На фиг. 1 представлена блок-схема устройства; на- фиг. 2 - функциональная схема блока приема, на фиг. 3 - временная диаграмма и вид массива состояний канала. Устройство многоканального ввода содержит блок сопряжения 1, блоки 2 лриема буферов каналов, селектор буферов каналов 3, блок рассогласования 4, шифратор адреса 5, коммутатор состояния каналов 6 блок Занесения 7, буферный регистр 8, блок управления 9, основные функциональ- ные связи устройства многоканального вво да - входные шины Ю устройства сопряжения, выходные шины 11 устройства сопряжения, шины 12 сигналов рассогласования каналов, шины 13 инверсных сигналов рассогласования каналов, выходные uwHbi 14 блок.а рассогласования, кодовые дилы 15 шифратора адреса, шины 16 вы- борки канала, выходная шина 17 коммут& состояния каналов, кодовые шины 18 номера канала, кодовые ишны 19 состояния канала, шина 20 занесения в буферный регистр, шина 21 управляющих сигналов, выходная шина 22 сигналов занесе ния состояния, щина 23 запроса ввода, входная шина 24. Блок 2 приема буфера канала состоит из триггера приема 25 с входными схемами ИЛИ 26, 27, осуществляющего хранение информации о предшествующем последнему изменению состоянии канала, инвертора 28, осуществляющего инверсию поступающих с блока сопряжения сигналов и схемы 29 сравнения канала, которая производит сравнение состояний канала и триггера приема (в. состав схемы сравнения входят схемы И ЗО, 31 и ИЛИ 32, iiHBepTop 33). На фиг. 3 обозначены моменты изменения состояния канала на выходе устрой ства сопряжения и приведен пример записи соответствующих моментов изменешя состояний канала в массив канала с I о , ячейку оперативной памяти процессора, где , О - состояния каналов, rf ч ... .fc - реальное время изменения состояния каналов. Принцип работы устройства многоканального ввода заключается в следующем. Информация, поступающая с терминальных пультов, преобразуется устройством сопряжения в уровни элементов, например в уро&ни интегральных схем, на которых может быть выполнено устройство. Сигналы на выходных щинах 11 блока сопряжения 1 представляют собой двухуровневую последовательность изменений напряжений во времени. Устройство ввода фиксирует только изменения состо5ший каналов. По изменению состояния любого канала уСтройст ва ввода посылает сигнал запроса ввода, по которому процессор осуществляет приостановку выполнения программы, и в соответствии с номером канала, изменившего состояние, осуществляет запись в массив состояний канал аоперативной памяти (каждому каналу соответствует свой массив), код состояния канала (О или 1.) в сопровождении текущего времени, который в данный момент записан на регистре времег ни процессора. Программы обработки массивов сотоя.НИИ каналовПроцессора, используя предварительно введенные в память процессора данные о скорости передачи каналов, преобразуют полученные временные метки в двоичные разряды, которые составляют сообщения, передаваемые по каналам связи.Работа многоканального устройства ввода состоит в следующем. В режиме ввода сигналы с блока сопряжения поступают по шинам 11 на блоки 2 приема буферов канала и коммутатор состояния каналов 6. В случае изменения состояния канала схема сравнения 29 вырабатывает сигналы рассогласования канала и инверсные сигналы рассогласования канала, которые соответственно по шиНам 12 поступают на шифратор адреса 5 и блок рассогласования 4 и по шинам 13 - на шифратор адреса 5 и коммутатор состояния 6 Шифратор адреса реагируя на сигналы рассогласования каналов, поступающие со схем сравнения блоков 2 приема буферов каналов последовательно, начиная с младших номеров каналов, изменивших состояние (в случае, если несколько каналов одновременно изменили состояние), на кодовых шинах 15 задает код номера канала, изменившего состояШ1е. Одновременно шифратор адреса 5 посылает по шинам 16 выборки канала сигнал, который открывает соответствующую коду выбранного канала входную сборку коммутатора состояний канала 6, вследствие этого на выходной шине 17 коммутатора состояний каналов 6 устанавливается код изменившего сост яние канала (О или 1). Кодовые шины 15 шифратора адреса 5 соединены с единичными входами триггеров буферного регистра, осуществляющих хранение кода номера канала; выходная шина 17 коммутатора состояний каналов соединена с еди ничным входом триггера, Осуществляющег , хранение кода состояния канала. В это же время по сигналам рассогла : сования каналов блок рассогласования 4 посылает сигнал, который по шине 14 по ступает на блок управления 9. По этому сигналу блок управления осуществляет вы работку двух тактирующих сигналов, сдви . нутых друг относительно друга во времен Первый сигнал поступает по шине 20 на единичные входы всех триггеров буфер ного регистра и осуществляет запись в буферный регистр кгда номера и сс тояния каналс1, изменившего состояние. Выходы триггеров буферного регистра, в которых записан код номера канала, соединены кодовыми шинами 18 номера канала с.устройством управления процессора и блоком занесе1шя 7. Выходы триггера буферного регистра, в котором записан код состояния канала, соединены кодовыми шинами 1, с устройством управления процессора. Второй тактирующий сигнал поступает по шине 21 управляющих сигналов на блок занесения 7, который в соответствии с кодом канала, записанным в буферном регистре 8, коммутирует поступивший иМпуЛьс на соответствующую выходную шину 22 сигналов занесения состояния, по которому в триггер приема 25 выбранного блока 2 приема буфера канала заносится код состояния канала. После этого блок управления 9 вырабатывает сигнал, который по шине 23 запроса ввода поступает в устройство управ ления процессора. Процессор приостанавливает программу обработки и по номе- . ру канала, который записан в буферном регистре 8, в соответствии с вышеописанным, осуществляет запись в массив состояний канала оперативной памяти состояния канала в сопровождении временной метки. После этого по сигналу процессора, поступающему по шине 24, блок управления 9 прекращает выработку потенциала запро са ввода, процессор возобновляет програь му обработки принятой информации. Цикл : ввода повторяется только при следующем изменении состояния в каналах, зафиксированным устройством многоканального ввода. Предмет изобретения 1. Устройство многоканального ввода, содержащее селектор буферов Каналов, блок сопряжения, связанный с входами устройства и буферами каналов, включающими блоки ; приема, отличающееся, тем, I что, с целью расширения функциональных возможностей устройства, оно содержит в селекторе буферов каналов шифратор адре- са, буферный регистр, блок рассогласования, комкутатор состояния каналов, блок занесения и блок управления, причем первый выход каждого блока приема соединен с соответствующими входами ши4чэатора адре-. са и блока рассогласова1шя, второй выход 1 каждого блока приема соединен ссоответ ствующим входом шифратора адреса и коммутатора состоя1шя каналов, первый выход шифратора адреса соединен с ycтaнoвoчны 4 входом буферного регистра, управляющий , ; вход которого соединен с первым выходом яблока управления, второй выход которого соединен с первым выходом устройства, а третий выход - с первым входом блока за-1 несения, второй вход которог-о соединен со вторым выходом устройства и первым выходом буферного регистра, а выход - с соответствующими входами блоков приема, второй выход ши(|ратора адреса соединен С соответствующим входом коммутатора состояния каналов, выход которого соединен с соответствующим входом буферного регистра, второй выход которого соединен с третьим выходом устройства, соответст вующий вход которого соединен с первым входом блока управления, второй, вход коTOporo соединен с выходом блока рассоглэсования, а блок сопряжения связан с вхо- . дамк коммутатора состояния каналов.I 2, Устройство поп. 1, отличающееся тем, что, с целью сокращения оборудования в нем каждый блок приема буферов каналов содержит триггер приема, инвертор, первую и вторую схемы совпадения, схему сравнеьшя, причем входы триггера приема соединены соответственно с выходами первой и второй схем совпадения, первые входы которых соединены с выходом блока занесения, второй вход первой схемы совпадения соединен с выходом блока сопряжения и входом инвертора, второй вход второй схемы совпадения соединен с выходом инвертора, выходы триггеpa приема, вход н выход инвертора соеди- i .тны соответствующими входами сравнения, выходы которой связаны с пер4 вым и вторым выходами блока приема.

Фиг. 2 г гп I вННММИНМА П Г t, t

Фиг л Я ВМНМЯШНВМИННЩМНМНМ1 I ч ° гп 1 гл. « 5 t, ., .

Авторы

Даты

1975-12-25—Публикация

1972-09-08—Подача