1

Изобретение относится к вычислительной технике, в частности к автоматически функционирующим системам регистрации и обработки данных с -выводом информации на внешние устройства вычислительной 1машины и может быть использовано для регистрации различного вида статистической и периодической информации.

Известно устройство для регистрации информации, содержащее блок управления, соединенный с входным блоком, с регистром опроса и приемным регистром адресного блока, с блоком выбора чисел, арифметическим блоком, распределителем и узлом обнаружения ошибок выходного блока, нричем приемный регистр адресного блока подключен ко входному блоку и блоку .выбора чисел, соединенному с блоком памяти, выходы которого цодключены к арифметическому блоку, связанному со входами блока памяти и к приемному регистру выходного блока, который связан с распределителем и через элемент ИЛИ - с узлом обнаружения ощибок и выходным регистром.

Основным -недостатком известных устройств регистрации является постоянный опрос всех элементов памяти приемного регистра без учета известного временного распределения поступления статической информации по каналйм, отсутствие регистрации числа ошибок и фор.мирования кода ошибки при передаче данных на внещние устройства.

С целью повышения точ ности и достоверности регистрации в состав предлагаемого устройства введены последовательно соединенные другой распределитель, подключенный к блоку управления, и триггеры, выходы которых соединены с адресным блоком, а входы- с входным блоком, подключенным к узлу обнаруп1ения ошибок.

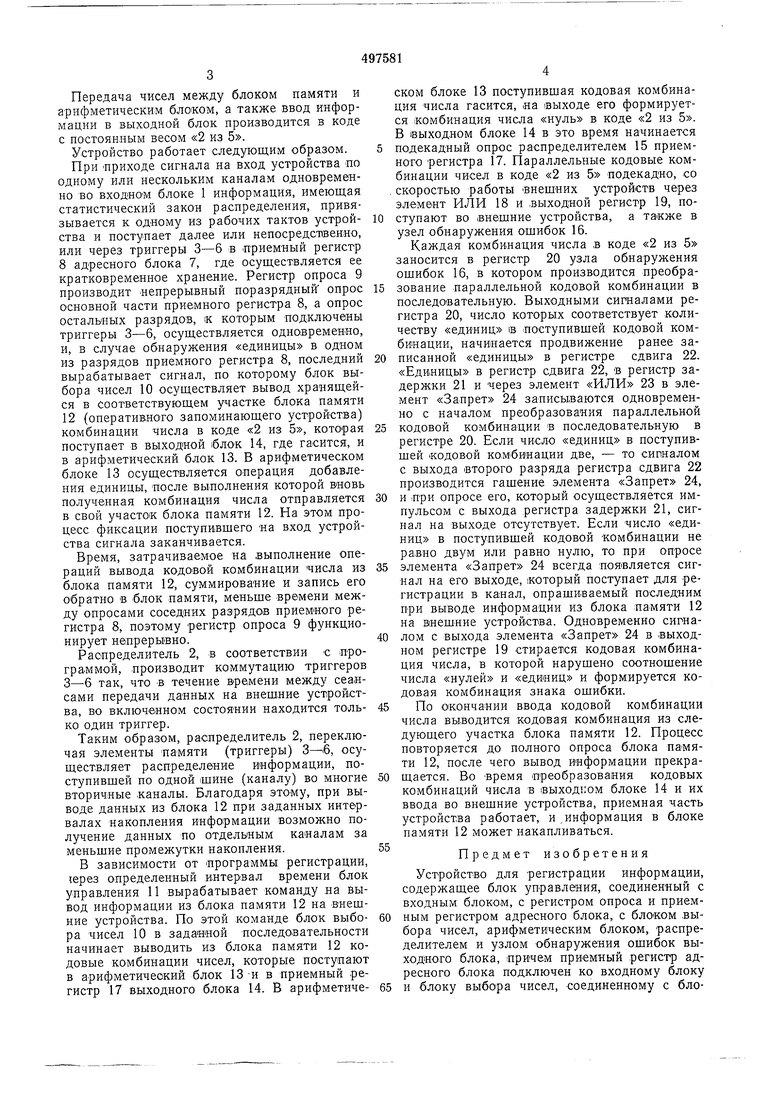

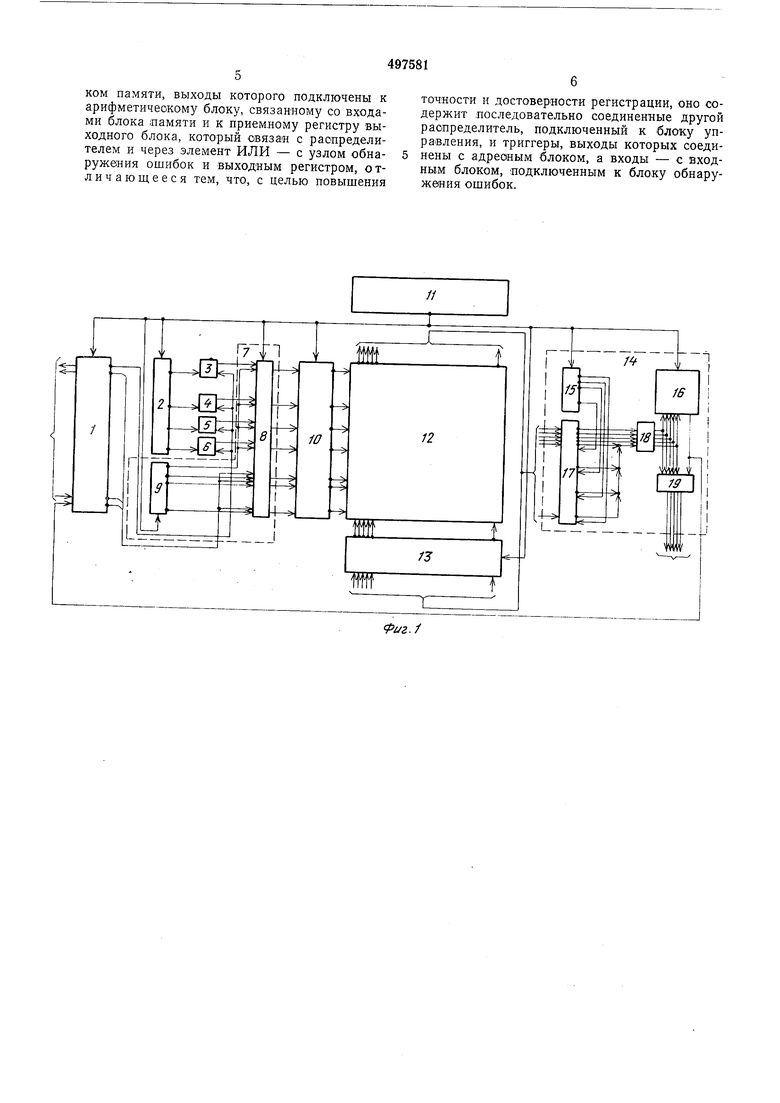

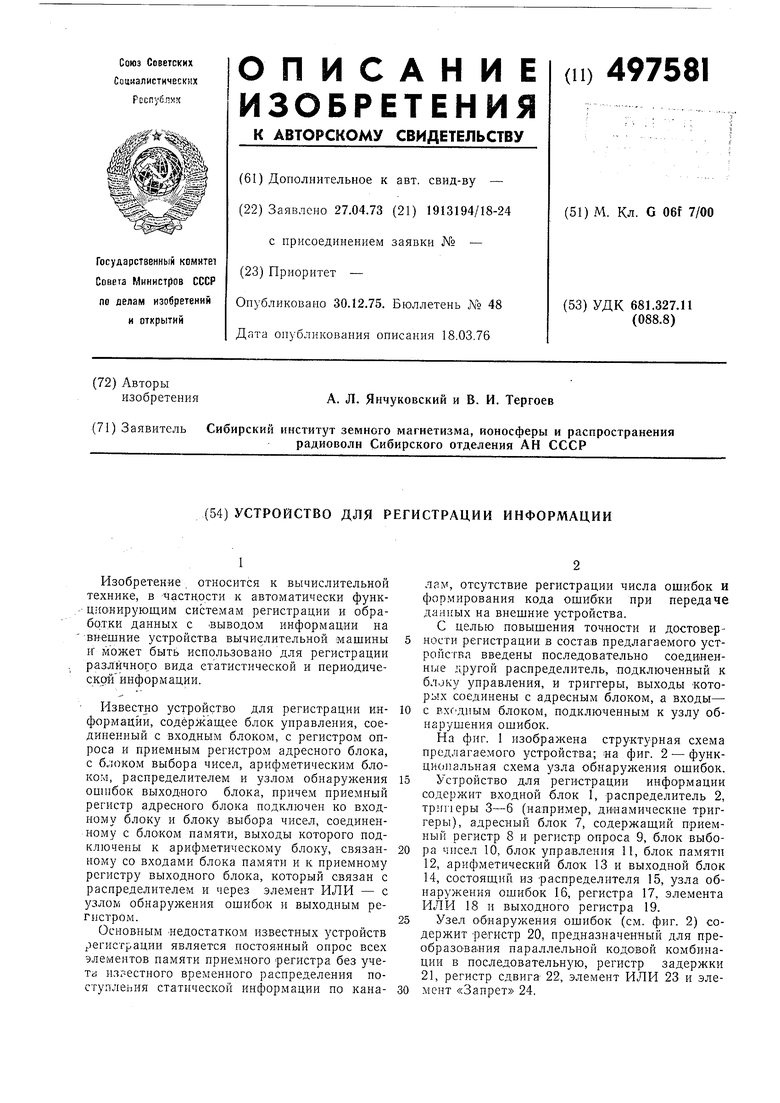

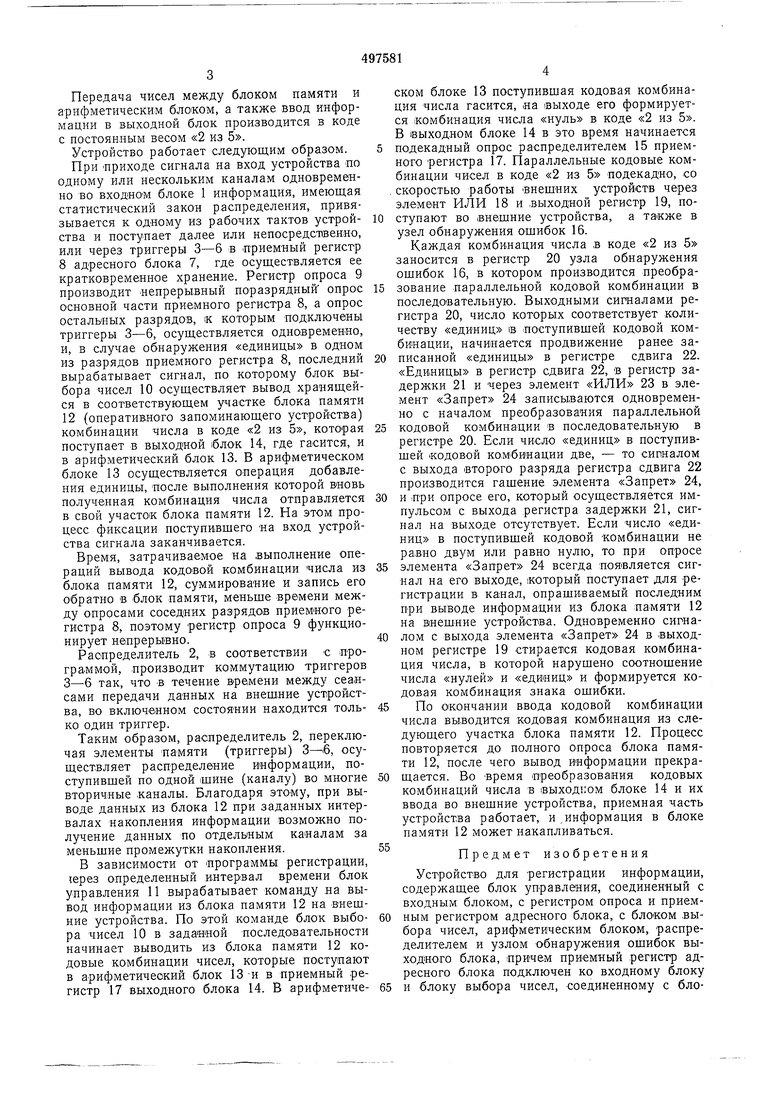

На фиг. 1 изображена структурная схема предлагаемого устройства; «а фиг. 2 - функциональная схема узла обнаружения ошибок.

Устройство для регистрации информации содержит входной блок 1, распределитель 2, трип еры 3-6 (например, динамические триггеры), адресный блок 7, содержащий приемный регистр 8 и регистр опроса 9, блок выбора чисел 10, блок упра-вления 11, блок памяти 12, арифметический блок 13 и выходной блок 14, состоящий из -распределителя 15, узла обнаружения ошибок 16, регистра 17, элемента ИЛИ 18 и выходного регистра 19.

Узел обнаружения ошибок (см. фиг. 2) содержит регистр 20, предназначенный для преобразования параллельной кодовой комбинации в последовательную, регистр задержки 21, регистр сдвига 22, элемент ИЛИ 23 и элемент «Запрет 24.

Передача чисел между блоком памяти и арифметическим блоком, а также ввод информации в выходной блок производится в коде с постоянным весом «2 из 5.

Устройство работает следующим образом.

При Приходе сигнала на вход устройства по одному или нескольким каналам одновременно во входном блоке 1 информация, имеющая статистический закон распределения, привязывается к одному из рабочих тактов устройства и поступает далее или непосредсивенио, или через триггеры 3-6 в «приемный регистр 8 адресного блока 7, где осуществляется ее кратковременное хранение. Регистр опроса 9 производит «непрерывный поразрядный опрос основной части приемного регистра 8, а опрос остальных разрядов, к которым подключены триггеры 3-6, осуществляется одновременно, и, в случае обнаружения «единицы в одном из разрядов приемного регистра 8, последний вырабатывает сигнал, по которому блок выбора чисел 10 осуществляет вывод хранящейся в Соответствующем участке блока памяти 12 (оперативного запоминающего устройства) комбинации числа в коде «2 из 5, которая поступает в выходной блок 14, где гасится, и в арифметический блок 13. В арифметическом блоке 13 осуществляется операция добавления единицы, после выполнения которой вновь полученная комбинация числа отправляется в свой участок блока памяти 12. На этом процесс фиксации поступивщего на вход устройства сигнала заканчивается.

Время, затрачиваемое на выполнение операций вывода кодовой комбинации числа из блока памяти 12, суммирование и запись его обратно в блок памяти, меньще времени между опросами соседних разрядов приемного регистра 8, поэтому регистр опроса 9 функционирует непрерывно.

Распределитель 2, в соответствии с программой, производит коммутацию триггеров 3-6 так, что в течение Времени между сеансами передачи данных на внещние устройства, во включенном состоянии находится только один триггер.

Таким образом, распределитель 2, переключая элементы памяти (триггеры) 3-б, осуществляет распределение информации, поступивщей по одной шине (каналу) во многие вторичные каналы. Благодаря этому, при выводе данных из блока 12 при заданных интервалах накопления информации возможно получение данных по отдельным каналам за меньшие промежутки накопления.

В зависимости от программы регистрации, ерез определенный интервал времени блок управления 11 вырабатывает команду на вывод информации из блока памяти 12 на внешние устройства. По этой команде блок выбора чисел 10 в заданной последовательности начинает выводить из блока памяти 12 кодовые комбинации чисел, которые поступают в арифметический блок 13 -и в приемный регистр 17 выходного блока 14. В арифметическом блоке 13 поступившая кодовая комбинация числа гасится, на выходе его формируется комбинация числа «нуль в коде «2 из 5. В выходном блоке 14 в это время начинается подекадный опрос распределителем 15 приемного регистра 17. Параллельные кодовые комбинации чисел в коде «2 из 5 подекадно, со скоростью работы «внешних устройств через элемент ИЛИ 18 и выходной регистр 19, поступают во внешние устройства, а та«кже в узел обнаружения ошибок 16.

Каждая комбинация числа в коде «2 из 5 заносится в регистр 20 узла обнаружения ошибок 16, в котором производится преобразование параллельной кодовой комбинации в последовательную. Выходными сигналами регистра 20, число которых соответствует количеству «единиц IB поступившей кодовой комбинации, начинается продвижение ранее записанной «единицы в регистре сдвига 22. «Единицы в регистр сдвига 22, в регистр задержки 21 и через элемент «ИЛИ 23 в элемент «Запрет 24 записываются одновременно с началом преобразования параллельной кодовой комбинации в последовательную в регистре 20. Если число «единиц в поступившей КОДОВОЙ комбинации две, - то сигналом с выхода «второго разряда регистра сдвига 22 производится гашение элемента «Запрет 24, и при опросе его, который осуществляется импульсом с выхода регистра задержки 21, сигнал на выходе отсутствует. Если число «единиц в поступившей кодовой -комбинации не равно двум или равно нулю, то при опросе элемента «Запрет 24 всегда появляется сигнал на его выходе, который поступает для регистрации в канал, опрашиваемый последним при выводе информации из блока памяти 12 на внешние устройства. Одновременно сигналом с выхода элемента «Запрет 24 в выходном регистре 19 стирается кодовая комбинация числа, в которой нарушено соотношение числа «нулей и «единиц и формируется кодовая комбинация знака ошибки.

По окончании ввода кодовой комбинации числа выводится кодовая комбинация из следующего участка блока памяти 12. Процесс повторяется до полного опроса блока па«мяти 12, после чего вывод информации прекращается. Во время «преобразования кодовых комбинаций числа в выходном блоке 14 и их ввода во внещние устройства, приемная часть устройства работает, и ,информация в блоке памяти 12 может накапливаться.

Предмет изобретения

Устройство для регистрации информации, содержащее блок управления, соединенный с входным блоком, с регистром опроса и приемным регистром адресного блока, с блоком выбора чисел, арифметическим блоком, распределителем и узлом обнаружения ощибок выходного блока, причем приемный регистр адресного блока подключен ко входному блоку и блоку выбора чисел, соединенному с блоком памяти, выходы которого подключены к арифметическому блоку, связанному со входами блока памяти и к приемному регистру выходного блока, который овязаи с распределителем и через элемент ИЛИ - с узлом обнаружения ошибок и выходным регистром, о тличающееся тем, что, с целью повышения

точности и достоверности регистрации, оно содержит .последовательно соединенные другой распределитель, подключенный к блоку управления, и триггеры, выходы которых соединены с адресным блоком, а входы - с входным блоком, подключенным к блоку обнаружения ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1972 |

|

SU342183A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Устройство для передачи телеметрической информации | 1975 |

|

SU558292A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство формирования строки | 1977 |

|

SU816792A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Система телемеханики для циклического опроса рассредоточенных объектов | 1977 |

|

SU691912A1 |

Авторы

Даты

1975-12-30—Публикация

1973-04-17—Подача