сл

fO

Изобретение относится к вычислительной технике и может быть использовано для выполнения арифметических действий.

Известно устройство для умножения чисел, содержащее регистры множимого и множителя, первый и второй блоки множительных устройств блок накопления частотных произведений.

Недостатком устройства является его низкая производительность.

Известно устройство для умножения двоичных чисел, содержащее первый и второй триггеры, регистры множимого и множителя, первую группу элементов И и блок сложения, причем информационный вход первого триггера соединен с входом мно.- жителя устройства, вход множимого которого соединен с информационным входом регистра множимого, разрядные выходы которого соединены с первыми входами соответствующих элементов И группы, выходы которых соединены с соответствующими информационными входами блока сложения, выход которого соединен с выходом результата устройства, информационный вход регистра множителя соединен с выходом первого триггера, счетный вход второго триггера, соединен с тактовым входом устройства и синхровходом блока сложения, вход сброса которого соединен с входами сброса устройства, регистров множимого и множителя/первого и второго триггеров, вход сдвига регистра множителя соединен с инверсным выходом второго триггера, прямой выход которого соединен с еинхров-, ходом первого триггера, входом сдвига .регистра множимого и тактовым выходом устройства, разрядные выходы регистра множителя соединены с вторыми входами соответствующих элементов И группы.

Недостатком устройства является его низкая производительность.

Цель изобретения - повышение производительности устройства.

Указанная цель достигается тем, что в устройство для умножения двоичных чисел, содержащее первый и второй триггеры, регистры множимого и множителя, первую группу элементов И и блок сложения, причем тактовый вход устройства подключен к счетному входу второго триггера и синхровходу блока сложения, вход сброса устройства соединен с входами сброса первого и второго триггеров, входами сброса регистров множимого и множителя и входом сброса блока сложения, входы множимого и множителя устройства подключены к информационным входам соответственно регистра множимого и первого триггера, выход которого соединен с информационным входом регистра множителя, а синхров- ход объединен с входом сдвига регистра множимого, является тактовым выходом устройства и подключен к прямому выходу

второго триггера, инверсный выход которого соединен с входом сдвига регистра множителя, разрядные выходы регистров множимого и множителя подключены соответственно к первым и вторым входам

0 .соответствующих элементов И первой группы,, выход блока сложения является выходом устройства, введены блок управления и вторая группа элементов И, первые входы которых подключены к выходам со5 ответствующих элементов И первой группы, вторые входы соединены с соответствующими выходами блока управления, а выходы подключены к соответствующим входам блока сложения, синхровходи вход сброса

0 которого объединены соответственно с синхровходом и входом сброса блока управления.

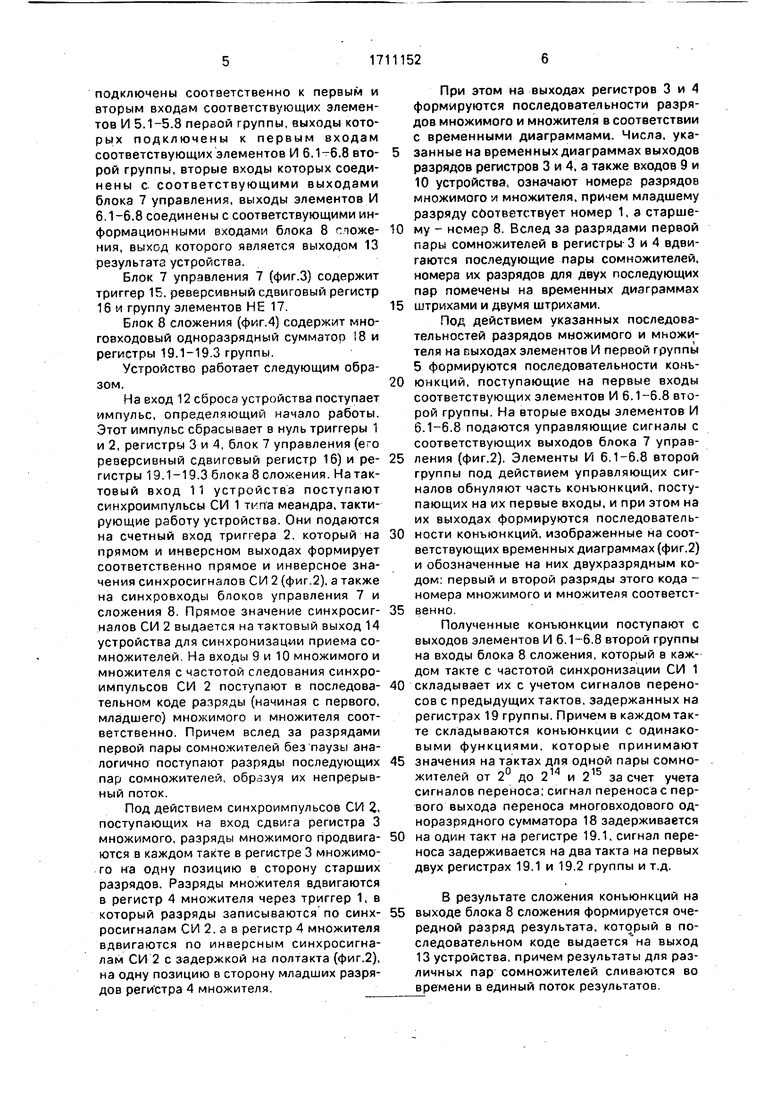

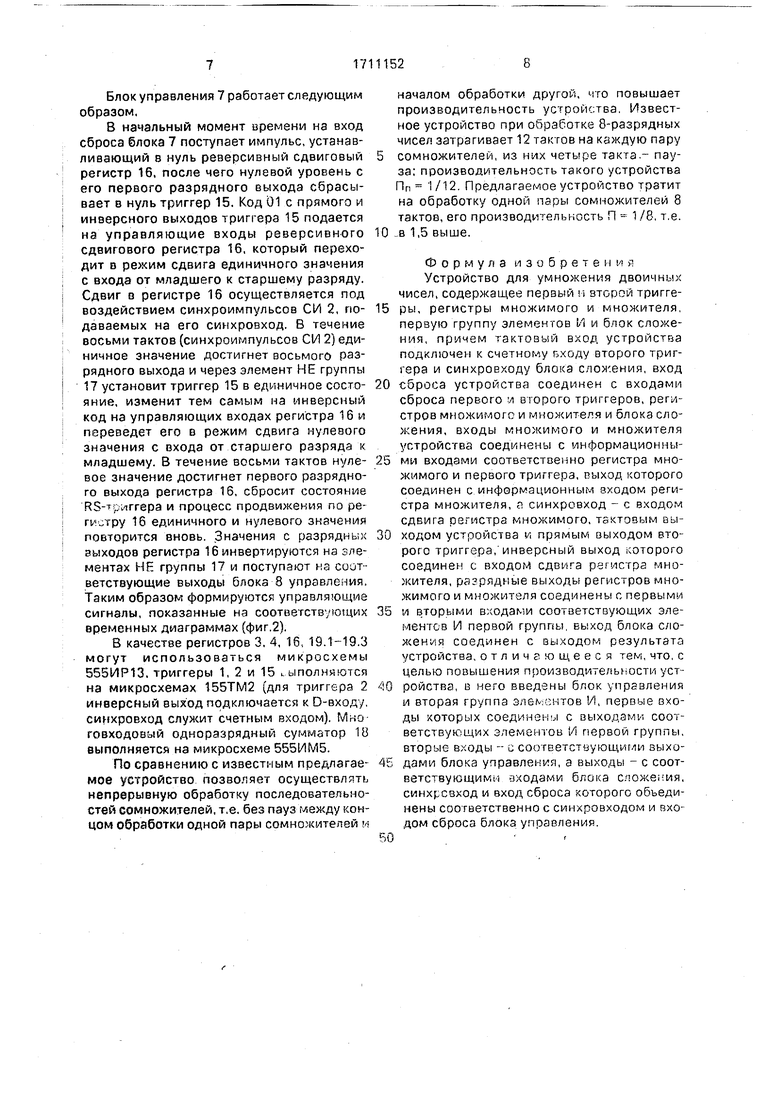

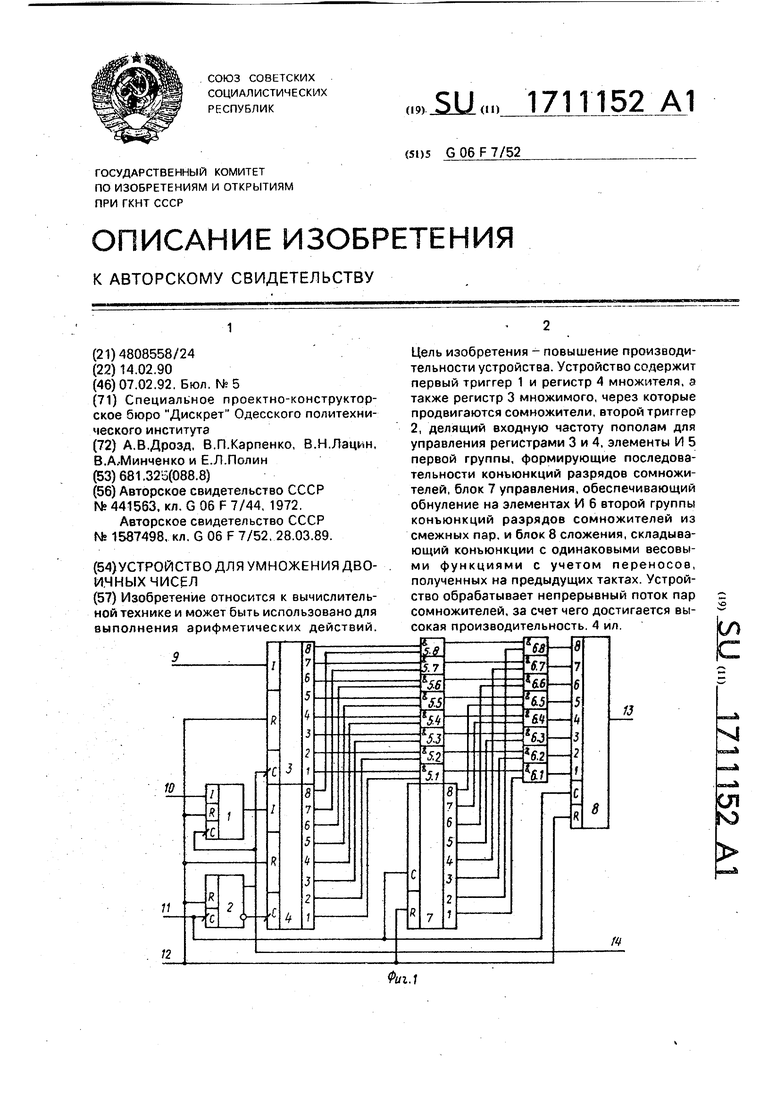

На фиг.1 показана схема устройства; на фиг.2 - временные диаграммы, иллюстриру5 ющие функционирование устройства при умножении восьмиразрядных двоичных чисел, поступающих на входы устройства в последовательном коде непрерывным потоком; на фиг.З - схема блока управления; на

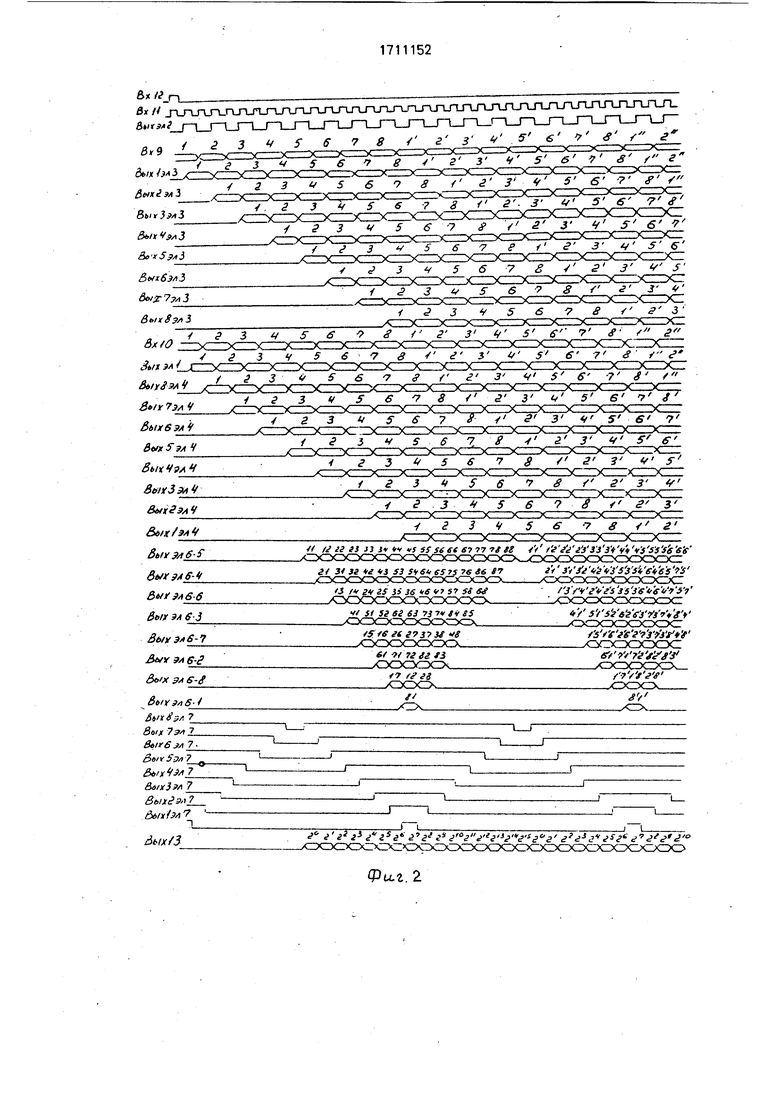

0 фиг.4-схема блока сложения.

Устройство содержит первый 1 и второй 2 триггеры, perncfpbi множимого 3 и множителя 4, элементы И 5.1, 5.2, .... 5.8 первой группы и элементы 6.1, 6.2, ..., 6.8 второй

5 группы, блок 7 управления, блок 8 сложения, входы множимого 9 и множителя 10 устройства/тактовый вход 11 устройства, вход 12 сброса устройства, выход 13 ре-.

зультата устройства и тактовый выход 14

0 устройства, причем тактовый вход 11 устройства подключен к счетному входу второго триггера 2, синхровходу блока 7 управления-и синхровходу блока 8 сложения, вход 12 сброса устройства соединен с

5 входами сброса первого 1 и второго 2 триггеров, регистров множимого, 3 и множителя 4, входом сброса блока 7 управления и входом сброса блока 8 сложения, входы множимого 9 и множителя 10 устройства

0 подключены к информационным входам регистра 3 множимого и первого триггера 1, выход которого соединен с информационным входом регистра 4 множителя, а синхровход объединен с входом сдвига ре5 гистра 3 Множимого, является тактовым выходом 14 устройства и подключен к прямому выходу второго триггера 2, инверсный выход которого соединен с входом сдвига регистра 4 множителя разрядные выходы регистров множимого 3 и множителя 4

подключены соответственно к первым л вторым входам соответствующих элементов И 5.1-5.8 первой группы, выходы которых подключены к первым входам соответствующих элементов И 6.1-6,8 второй группы, вторые входы которых соединены с соответствующими выходами блока 7 управления, выходы элементов И 6.1-6.8 соединены с соответствующими информационными входами блока 8 сложения, выход которого является выходом 13 результата устройства.

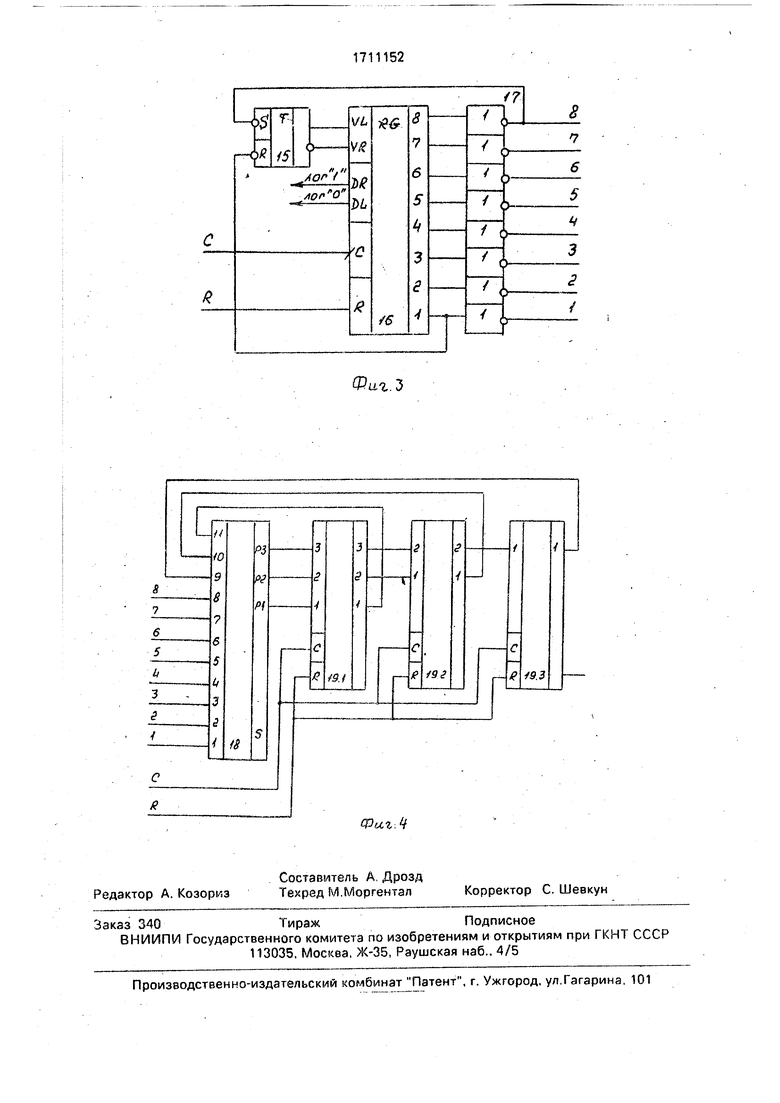

Блок 7 управления 7 (фиг.З) содержит триггер 15, реверсивный сдвиговый регистр 16 и группу элементов НЕ 17.

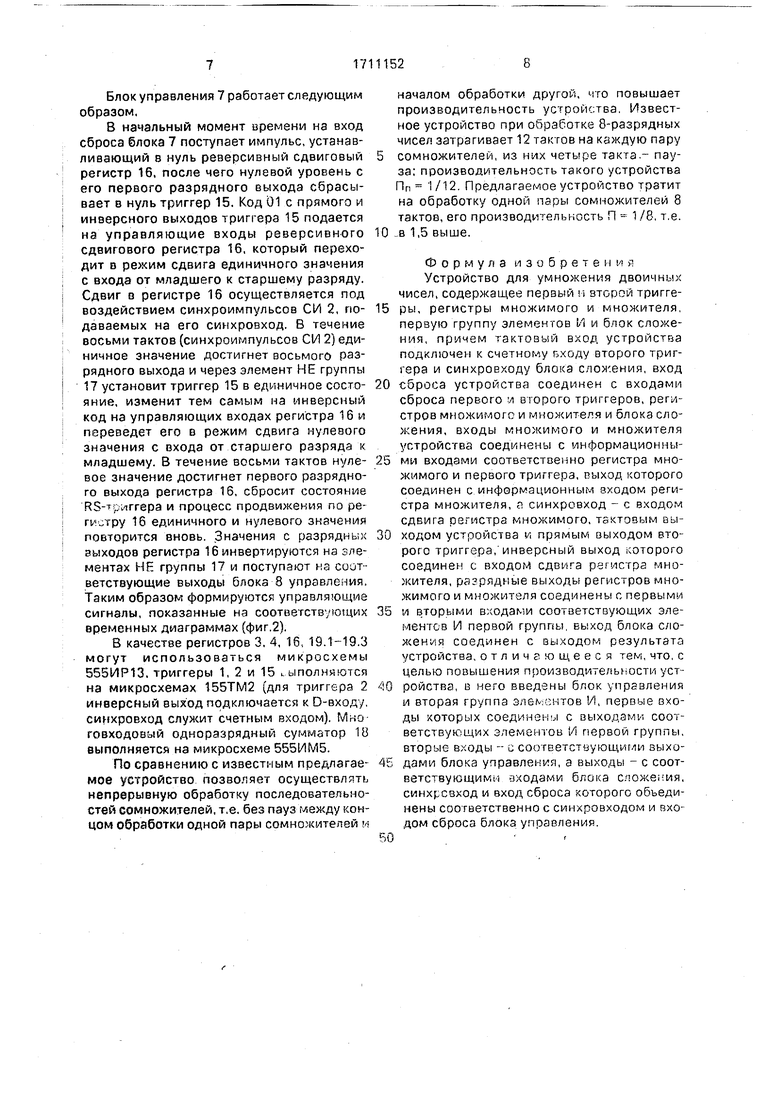

Блок 8 сложения (фиг.4) содержит мно- Г08ХОД08ЫЙ одноразрядный сумматор 18 и регистры 19.1-19.3 группы.

Устройство работает следующим образом.

На вход 1.2 сброса устройства поступает импульс, определяющий начало работы. Этот импульс сбрасывает в нуль триггеры 1 и 2, регистры 3 и 4, блок 7 управления (его реверсивный сдвиговый регистр 16) и регистры 19.1-19.3 блока 8 сложения. Натак- товый вход 11 устройства поступают синхроимпульсы СИ 1 тип а меандра, тактирующие работу устройства. Они подаются на счетный вход триггера 2. который на прямом и инверсном выходах формирует соответственно прямое и инверсное значения синхросигналов СИ 2 (фиг.2), а также на синхровходы блоков управления 7 и сложения 8. Прямое значение синхросиг- налов СИ 2 выдается на тактовый выход 14 устройства для синхронизации приема сомножителей. На входы 9 и 10 множимого и множителя с частотой следования синхроимпульсов СИ 2 поступают в последовательном коде разряды (начиная с первого, младшего) множимого и множителя соответственно. Причем вслед за разрядами первой пары сомножителей без паузы аналогично поступают разряды последующих пар сомножителей, образуя их непрерывный поток.

Под действием синхрЬимпульсов СИ 2, поступающих на вход сдвига регистра 3 множимого, разряды множимого продвигаются в каждом такте в регистре 3 множимого ка одну позицию в сторону старших разрядов. Разряды множителя вдвигаются в регистр 4 множителя через триггер 1, в который разряды записываются по синхросигналам СИ 2. а в регистр 4 множителя вдвигаются по инверсным синхросигналам СИ 2 с задержкой на полтакта (фиг.2), на одну позицию в сторону младших разрядов регистра 4 множителя.

При этом на выходах регистров 3 и 4 формируются последовательности разрядов множимого и множителя в соответствии с временными диаграммами.. Числа, ука- 5 занные на временных диаграммах выходов разрядов регистров 3 и 4, а также входов 9 и 10 устройства, означают номера разрядов множимого и множителя, причем младшему разряду сбответствует номер 1, а старше0 му - номер 8. Вслед за разрядами первой пары сомножителей в регистры- 3 и 4 вдвигаются последующие пары сомножителей, номера их разрядов для двух последующих пар помечены на временных диаграммах

5 штрихами и двумя штрихами.

Под действием указанных последовательностей разрядов множимого и множителя на выходах элементов И первой группы 5 формируются последовательности конь0 юнкций, поступающие на первые входы соответствующих элементов И 6.1-6.8 второй группы. На вторые входы элементов И 6.1-6.8 подаются управляющие сигналы с соответствующих выходов блока 7 управ5 ления (фиг.2). Элементы И 6.1-6.8 второй группы под действием управляющих сигналов обнуляют часть конъюнкций, поступающих на их первые входы, и при этом на их выходах формируются последователь0 ности конъюнкций, изображенные на соответствующих временных диаграммах (фиг.2) и обозначенные на них двухразрядным кодом: первый и второй разряды этого кода - номера множимого и множителя соответст5 венно.

Полученные конъюнкции поступают с выходов элементов И 6.1-6.8 второй группы на входы блока 8 сложения, который в каждом такте с частотой синхронизации СИ 1

0 складывает их с учетом сигналов переносов с предыдущих тактов, задержанных на регистрах 19 группы. Причем в каждом такте складываются конъюнкции с одинаковыми функциями, которые принимают

5 значения на тактах для одной пары сомножителей от 2° до 214 и 215 за счет учета сигналов переноса; сигнал переноса с первого выхода переноса многовходового одноразрядного сумматора 18 задерживается

0 на один такт на регистре 19.1. сигнал переноса задерживается на два такта на первых двух регистрах 19.1 и 19.2 группы и т.д.

В результате сложения конъюнкций на 5 выходе блока 8 сложения формируется очередной разряд результата, который в последовательном коде выдается на выход 13 устройства, причем результаты для различных пар сомножителей сливаются во времени в единый поток результатов.

Блок управления 7 работает следующим образом.

В начальный момент времени на вход сброса блока 7 поступает импульс, устанавливающий в нуль реверсивный сдвиговый регистр 16, после чего нулевой уровень с его первого разрядного выхода сбрасывает в нуль триггер 15, Код 01 с прямого и инверсного выходов триггера 15 подается на управляющие входы реверсивного сдвигового регистра 16, который переходит в режим сдвига единичного значения с входа от младшего к старшему разряду. Сдвиг в регистре 16 осуществляется под воздействием синхроимпульсов СИ 2, подаваемых на его синхровход. В течение восьми тактов (синхроимпульсов СИ 2) еди- ничное значение достигнет восьмого разрядного выхода и через элемент НЕ группы 17 установит триггер 15 в единичное состояние, изменит тем самым на инверсный код на управляющих входах регистра 16 и переведет его в режим сдвига нулевого значения с входа от старшего разряда к младшему. В течение восьми тактов нулевое значение достигнет первого разрядного выхода регистра 16, сбросит состояние RS-триггера и процесс продвижения по регистру 16 единичного и нулевого значения повторится вновь. Значения с разрядных выходов регистра 16 инвертируются на элементах НЕ группы 17 и поступают на соответствующие выходы блока 8 управления. Таким образом формируются управляющие сигналы, показанные на соответствующих временных диаграммах (фиг.2).

В качестве регистров 3, 4, 16, 19.1-19.3 могут использоваться микросхемы 555ИР13. триггеры 1. 2 и 15 выполняются на микросхемах 155ТМ2 (для триггера 2 инверсный выход подключается к D-входу. синхровход служит счетным входом). Мно- говходовый одноразрядный сумматор 18 выполняется на микросхеме 555ИМ5.

По сравнению с известным предлагаемое устройство позволяет осуществлять непрерывную обработку последовательностей сомножителей, т.е. без пауз между концом обработки одной пары сомножителей м

началом обработки другой, что повышает производительность устройства. Известное устройство при обработке 8-разрядных чисел затрагивает 12 тактов на каждую пару

сомножителей, из ни четыре такта.- пауза; производительность такого устройства Пп 1/12. Предлагаемое устройство тратит на обработку одной пары сомножителей 8 тактов, его производительность П 1 /8, т.е.

в 1,5 выше.

Формула изобретения Устройство для умножения двоичных чисел, содержащее первый и второй триггеры, регистры множимого и множителя, первую группу элементов И и блок сложения, причем тактовый вход устройства подключен к счетному входу второго триггера и синхровходу блока сложения, вход

сброса устройства соединен с входами сброса первого и второго триггеров, регистров множимого и множителя и блока сложения, входы множимого и множителя устройства соединены с информационными входами соответственно регистра множимого и первого триггера, выход которого соединен с, информационным входом регистра множителя, а синхровход - с входом сдвига регистра множимого, тактовым выходом устройства и прямым выходом второго триггера, инверсный выход которого соединен с входом сдвига регистра множителя, разрядные выходы регистров множимого и множителя соединены с первыми

и вторыми входами соответствующих элементов И первой группы, выход блока сложения соединен с выходом результата устройства, отличающееся тем, что, с целью повышения производительности устройства, в него введены блок управления и вторая группа элементов И, первые входы которых соединены с выходами соответствующих элементов И первой группы, вторые входы - с соответствующими выходами блока управления, а выходы - с соответствующими входами блока сложения, синхровход и вход сброса которого объединены соответственно с синхровходом и входом сброса блока управления.

г

ft t It H, /9 ХЭОООООО

fa tf t.s tf 91 f ff

f-Sre л/ф

Ь-9уеяпд

Ј-$re иод.

ng

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для умножения | 1986 |

|

SU1401454A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Устройство для умножения | 1987 |

|

SU1481744A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

Изобретение относится к вычислительной технике и может быть использовано для выполнения арифметических действий. Цель изобретения - повышение производительности устройства. Устройство содержит первый триггер 1 и регистр 4 множителя, а также регистр 3 множимого, через которые продвигаются сомножители, второй триггер 2, делящим входную частоту пополам для управления регистрами 3 и 4, элементы И 5 первой группы, формирующие последовательности конъюнкций разрядов сомножителей, блок 7 управления, обеспечивающий обнуление на элементах И 6 второй группы конъюнкций разрядов сомножителей из смежных пар, и блок 8 сложения, складывающий конъюнкции с одинаковыми весовыми функциями с учетом переносов, полученных на предыдущих тактах. Устройство обрабатывает непрерывный поток пар сомножителей, за счет чего достигается высокая производительность. 4 ил. . . сл С

MjAW.tf&At.&.VSf ,&t.999tf S9i, es tbMestt te

,,,3f,s.t,f.1,bf,t.i&,lp,f,t,// at it- n, 1.9 99 ssf s t tr te it г/ tt

T

ZQtllil

f-$vЈ xiig

/,ve/xi«g

D

Pj

Л PI

/s.y

Фи.г.Ъ

«

| Устройство для умножения | 1972 |

|

SU441563A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1990-02-14—Подача