1

Изобретение относится к вычислительной технике и может быть исиользоваио в управляющих системах и гибридных вычислительных устройствах.

Известно устройство умножения двоичных кодов на постоянный коэффициент (но величине, меньший единицы, что аналогично делению на целое число), содерлсащее входной счетчик, счетчик результата, узел ввода коэффициентов, генератор тактовых имнульсов, устройство управления и вентили кода. Однако это устройство имеет низкое быстродействие, обусловленное последовательным режимом обработки имнульсов, количество которых определяется величиной входного кода, большой объем оборздования, так как для обработки аналоговых сигналов оно содержит дополнительно аналого-цифровой преобразователь, и ограниченные функциональные возможности, поскольку в устройстве производится деление на постоянный коэффициент и отсутствует возможность деления двух переменных аналоговых величин. Известно также устройство для деления двух чисел, содержащее два регистра, сумматор и блоки элементов И. Для деления двух аналоговых величин используются два аналого-цифровых преобразователя, результаты преобразования которых поступают на регистры устройства деления, где и осуществляется операция деления

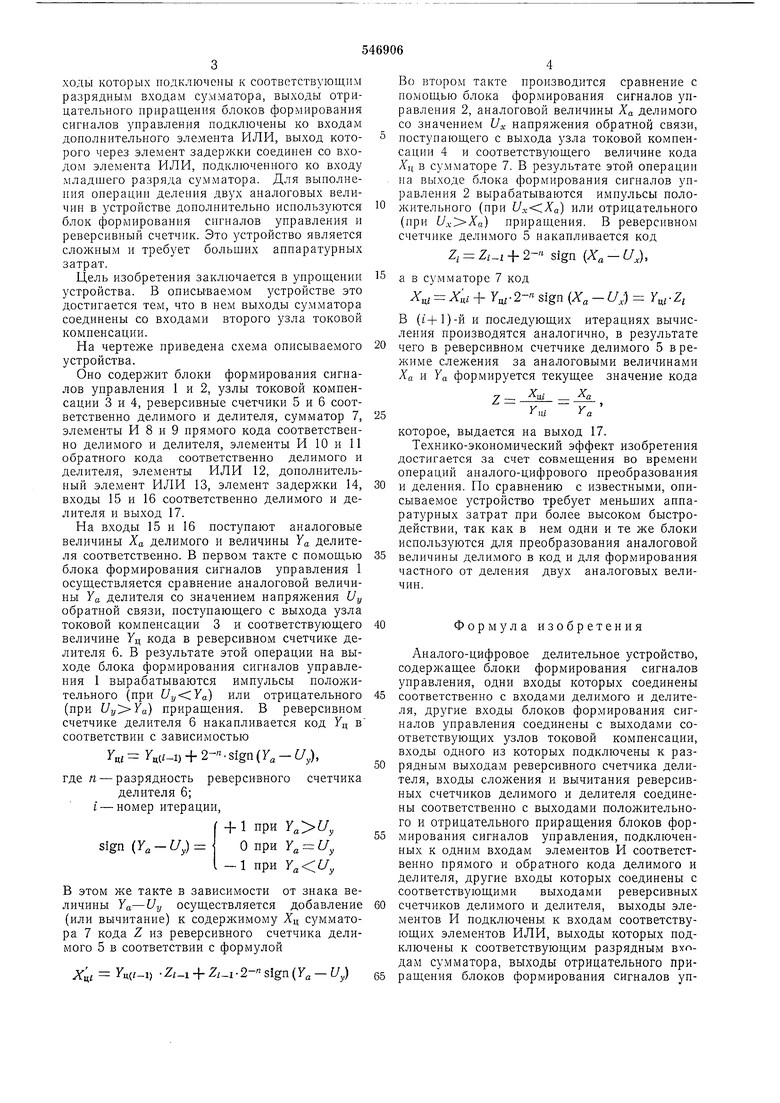

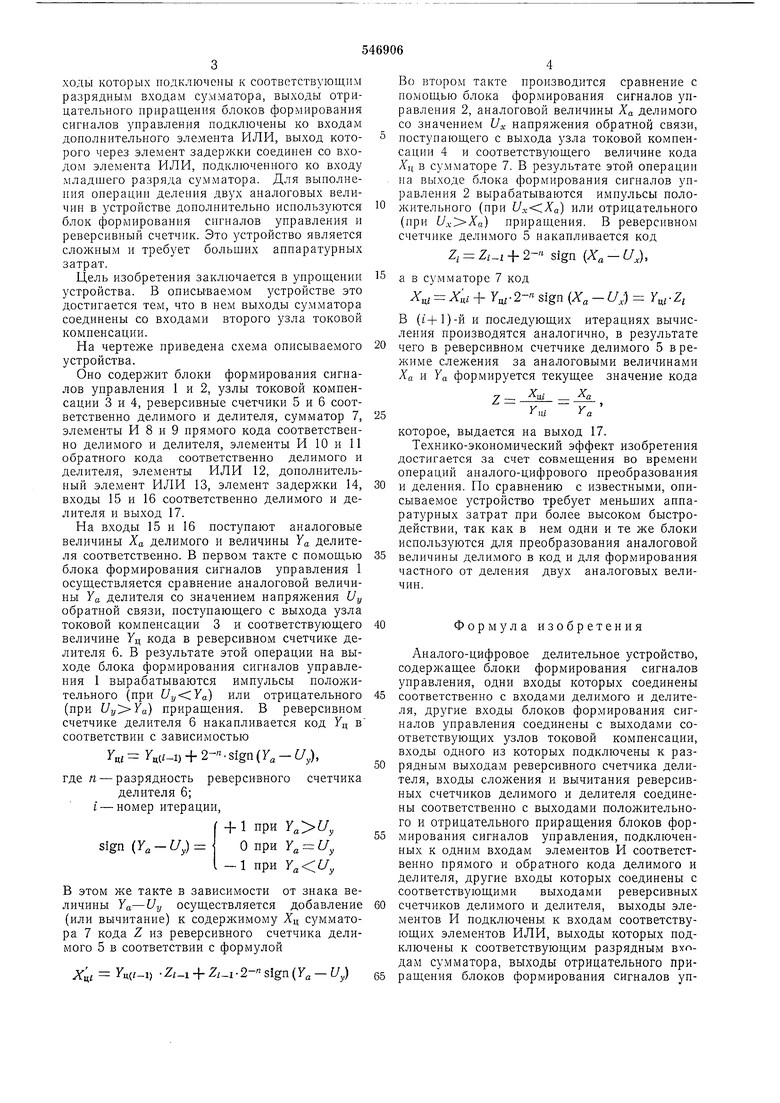

двух чисел. Оно характеризуется также низким быстродействием, так как, после преобразования аналоговых величин в коды, в нем затрачивается дополнительно п тактов для выполнення операцип деления двух цифровых кодов, и сложностью, обусловленной наличием двух аналого-цифровых преобразователей и собственно блока деления цифровых кодов. Наиболее близким к изобретению по технической сущности является аналого-цифровое делительное устройство, содержащее блоки формирования сигналов управления, одни входы которых соединены соответственно с входами делимого и делителя, другие входы блоков формирования сигналов управления соединены с выходами соответствующих узлов токовой компенсации, входы одного из которых подключены к разрядным выходам реверсивного счетчика делителя, входы сложения и вычитания реверсивных счетчиков делимого и делителя соединены соответственно с выходами положительного и отрицательного приращеиия блоков формирования сигналов управления, подключенных к одним входам элементов И соответственно прямого и обратного кода делимого и делителя, другие входы которых соединены с соответствующими выходами реверсивных счетчиков делимого и делителя, выходы элементов И подключены к входам соответствующих элементов ИЛИ, выходы которых подключены к соответствующим разрядным входам сумматора, выходы отрицательного приращения блоков формирования сигналов управления подключены ко входам дополнительного элемента ИЛИ, выход которого через элемент задержки соединен со входом элемента ИЛИ, подключенного ко входу младшего разряда сумматора. Для выиолнепия операции делеиия двух аналоговых величин в устройстве дополнительно исиользуются блок формирования сигиалов управления и реверсивный счетчик. Это устройство является сложиым и требует больщих аппаратурных затрат. Цель изобретения заключается в уирощении устройства. В описываемом устройстве это достигается тем, что в нем выходы сумматора соединены со входами второго узла токовой компенсации. На чертеже приведена схема описываемого устройства. Оно содержит блоки формирования сигналов управления 1 и 2, узлы токовой компенсации 3 и 4, реверсивные счетчики 5 и 6 соответственно делимого и делителя, сумматор 7, элементы И 8 и 9 ирямого кода соответственно делимого и делителя, элементы И 10 и II обратного кода соответственно делимого и делителя, элементы ИЛИ 12, дополнительный элемент ИЛИ 13, элемент задержки 14, входы 15 и 16 соответственно делимого и делителя и выход 17. На входы 15 и 16 поступают аналоговые величины Ха делимого и величины Уд делителя соответственно. В первом такте с помощью блока формирования сигналов управления 1 осуществляется сравнение аналоговой величины Ya делителя со значением напряжения Uy обратной связи, поступающего с выхода узла токовой компенсации 3 и соответствующего величине Уц кода в реверсивном счетчике делителя 6. В результате этой операции на выходе блока формирования сигналов управления 1 вырабатываются импульсы положительного (при ) или отрицательного (при ) приращения. В реверсивном счетчике делителя 6 накапливается код Уц в соответствии с зависимостью (-i) + 2-.sign(y,-,), где п - разрядность реверсивного счетчика делителя 6; I - номер итерации, f+1 при Y,Uy sign (Y,-U О при Y, Uy 1 при У«, В этом же такте в зависимости от знака величины Уа-Uy осуществляется добавление (или вычитание) к содержимому Xj сумматора 7 кода Z из реверсивного счетчика делимого 5 в соответствии с формулой X. У() 2/-1 + 2/-I 2- sign (У, - f/,) Во втором такте производится сравнение с помощью блока формирования сигналов управления 2, аналоговой величины Ха делимого со значением Ux напряжения обратной связи, поступающего с выхода узла токовой компенсации 4 и соответствующего величине кода Ац в сумматоре 7. В результате этой операции па выходе блока формирования сигналов управления 2 вырабатываются импульсы положительного (при ) или отрицательного (при ) приращения. В реверсивном счетчике делимого 5 накапливается код Z, Z,i + 2- sign (A«-t/J, а в сумматоре 7 код цг + Уцг 2-« sign (X, - и, . Уцг Z, В (1+1)-й и последующих итерациях вычисления производятся аналогично, в результате чего в реверсивном счетчике делимого 5 в режиме слежения за аналоговыми величинами Ха и Уа формируется текущее значение кода 7, ш а ij к к . V IUа которое, выдается на выход 17. Технико-экономический эффект изобретения достигается за счет совмещения во времени операций апалого-цифрового преобразования и деления. Но сравнению с известными, оиисываемое устройство требует меньщих аппаратурных затрат при более высоком быстродействии, так как в нем одни и те же блоки используются для преобразования аналоговой величины делимого в код и для формирования частного от деления двух аналоговых BevTHчин. Формула изобретения Аналого-цифровое делптельное устройство, содержащее блоки формирования сигналов управления, одни входы которых соединены соответственно с входами делимого и делителя, другие входы блоков формирования сигналов управления соединены с выходами соответствующих узлов токовой компенсации, входы одного из которых подключены к разрядным выходам реверсивного счетчика делителя, входы сложения и вычитания реверсивных счетчиков делимого и делителя соединены соответственно с выходами положительного и отрицательного приращения блоков формирования сигналов управления, подключенных к одним входам элементов И соответственно прямого и обратного кода делимого и делителя, другие входы которых соединены с соответствующими выходами реверсивных счетчиков делимого и делителя, выходы элементов И подключены к входам соответствующих элементов ИЛИ, выходы которых подключены к соответствующим разрядным вводам сумматора, выходы отрицательного приращения блоков формирования сигналов управления подключены ко входам дополнительного элемента ИЛИ, выход которого через элемент задержки соединен со входом элемента ИЛИ, нодключеииого ко входу младпгего разряда сумматора, отличающееся тем, что, с целью унрощения устройства, в нем выходы сумматора соединены со входами второго узла токовой компенсации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1974 |

|

SU499569A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Устройство для коррекции характеристик измерительных преобразователей | 1982 |

|

SU1100630A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ | 2000 |

|

RU2176090C1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

Авторы

Даты

1977-02-15—Публикация

1974-02-01—Подача