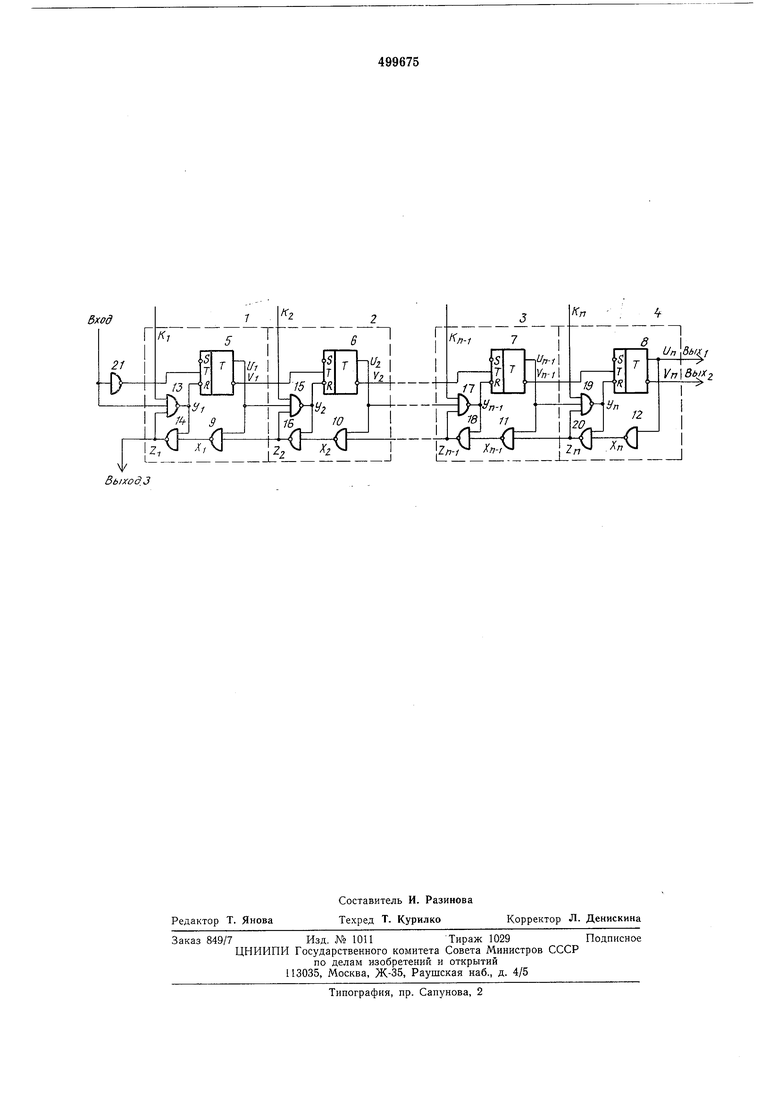

Изобретение относится к области радиоэлектроники, в часткости к делителям частоты следования импульсов с регулируемым коэффициентом деления, используемым в измерительных приборах, устройствах управления и автоматики. Известен делитель частоты,, содержащий последовательный счетчик со счетным триггером, триггером управления и схемой «И-НЕ в каждом разряде, причем единичный выход счетного триггера соединен с первым входом схемы «И-НЕ своего разряда и со входом установа в ноль триггера управления соседнего, старшего разряда. С целью повышения надежности и уменьшения числа связей в устройстве второй вход схемы «И-НЕ соединен с единичным выходом триггера управления соседнего, старшего, разряда, выход схемы «И-НЕ соединен с единичным входом триггера управления своего разряда, нулевой выход триггера управления соединен со сходом установа в единицу счетного триггера своего разряда, входы управления коэффициентом деления соединены с нулевыми входами триггеров управления, единичный выход триггера управления младшего разряда соединен с выходной шиной. На чертеже изображена функциональная схема предлагаемого делителя частоты. Делитель частоты состоит из идентичных азрядов 1-4, каждый из которых содержит четный триггер 5-8, логическую схему «И- НЕ 9-12 и управляющие триггеры 13-20. Парафазный входной сигнал делителя может быть получен любым из известных способов, например с помощью дополнительного инвертора 21. Отдельные разряды делителя частоты соединены последовательно один с другим таким образом, что счетные триггеры образуют счетчик входных импульсов, а логические схемы и управляющие триггеры - устройство управления. Делитель частоты работает следующим образом. В процессе счета входных импульсов последовательно заполняются (переход в единичное состояние) счетные триггеры делителя, начиная со старших разрядов. Переход триггера 8 /г-го разряда в единичное состояние происходит при переключение триггера 7 (п-)-го разряда в нулевое состояние, при этом , L/n-f 0- Сигнал Un l проходит через схему «И-НЕ 12, второй вход которой в старшем разряде не задействован, и действует на единичный вход управляющего триггера 19-20, при этом на его единичном выходе формируется сигнал

готовности , поступающий в (п-1)-й разряд на схему «И-НЕ И.

Если код управления 1, то на нулевом выходе управляющего триггера 19-20 формируется сигнал в момент времени, когда триггер 7 (п-1)-го разряда переходит в единичное состояние, сигнал нулевом входе управляющего триггера 19-20 принимает значение «1. Сигнал ,Уп 0 устанавливает триггера 8 в нулевое состояние, в результате чего управляющий триггер 19-20 хранит свое состояние до поступления сбрасывающего сигнала .

Таким образом, управляющий триггер в ячейке управления выполняет функцию запоминания сигнала готовности 2„ и сигнала установки УП на время выполнения установки счетного триггера данного разряда. Сигнал У„ 0 формируется управляющим триггером в момент паузы сигнала на счетном входе триггера данного разряда. Если в коде управления Kn Q, то сигнал УИ постоянно сохраняет значение «1, и установка счетного триггера не производится.

Сигнал Q на единичном входе управляющего триггера 17-18 (п-1)-го разряда формируется при условии наличия сигнала и при переходе счетного триггера 7 (п-1)-го разряда в единичное состояние ((). Формирование сигнала готовности Zn-i и сигнала установки Yn-i нроисходит так же, как и в п-ом разряде. Аналогичным образом происходит работа любого t-ro разряда делителя.

Предустановка счетного триггера t-ro разряда осуществляется сигналом Yf KiZiUi-i Q в момент времени, когда и 17г-1 1. Одновременно устройство управления формирует сигнал готовности предыдущего разряда

: Xi-l ZfUi-i 1.

Таким образом, сигнал предустановки i-ro разряда Yi 0 формируется одновременно с сигналом готовности предыдущего разряда.

Возврат управляющих триггеров устройства управления в исходное состояние происходит следующим образом.

Под действием сигнала предустаиовки Yi iO счетный триггер переключается в нулевое состояние, при этом сигнал с помощью логической схемы «И-НЕ отключает единичный вход управляющего триггера и устанавливает в исходное состояние ynpaiBляющий триггер последующего разряда (Zj+i 0). Одновременно формируется сигнал переноса , который поступает на счетный вход тригера последующего разряда и переключает его в противоположное состояние.

Если предустановка счетного тригера г-го разряда выключена сигналом , то возврат схемы в исходное осстояние происходит в момент переключения счетного триггера от импульса переноса Vi-i, который возникает либо при установке одного из предыдущих разрядов, либо при переполнении младших разрядов счетчика, если их предустановка не производится.

Таким образом, сигнал готовности Zi, а, следовательно, и сигналы установки Уг распространяются последовательно от старших разрядов к младшим в каждом цикле деления.

Формула изобретения

Делитель частоты, содержащий последовательный счетчик со счетным триггером, триггером управления и схемой «И-НЕ в каждом разряде, причем, единичный выход счетного триггера соединен с первым входом схемы «И-НЕ своего разряда и со входом установа в ноль триггера управления соседнего, старшего разряда, отличающийся тем, что, с целью повышения надежности и уменьшения числа связей в устройстве, второй вход схемы «И-НЕ соединен с единичным выходом триггера управления соседнего, старшего разряда, выход схемы «И-НЕ соединен с единичным входом триггера управления своего разряда, нулевой выход триггера управления соединен со входом установа в единицу счетного триггера своего разряда, входы управления коэффициентом деления соединены с нулевыми входами триггеров управления, единичный выход триггера управления младшего разряда соединен с выходной шиной.

/г.

&ход

K,7|5w/2

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1972 |

|

SU472463A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Устройство для генерации пачек импульсов | 1984 |

|

SU1234953A1 |

| Цифровое устройство управления широтно-импульсным преобразователем | 1986 |

|

SU1411960A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1213417A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Устройство микропрограммного управления | 1984 |

|

SU1239715A1 |

Авторы

Даты

1976-01-15—Публикация

1973-09-05—Подача