f12397

Изобретение относится к вычислиельной технике и автоматике и может ыть использовано для реализации ра з- ичных уровней управления в специлизированных процессорах, ориенти- 5 ованных на обработку индексированых данных, в частности для формироания адресов операндов при вычислеии быстрых предбразований Фурье, олша и др. а также может использо- Ю ваться в -качестве различных пересчетых- схем е программируемым модулем счетаJ например, при создании синтезаторов частот.

Цель изобретения - повышение бы- 15 стродействия.

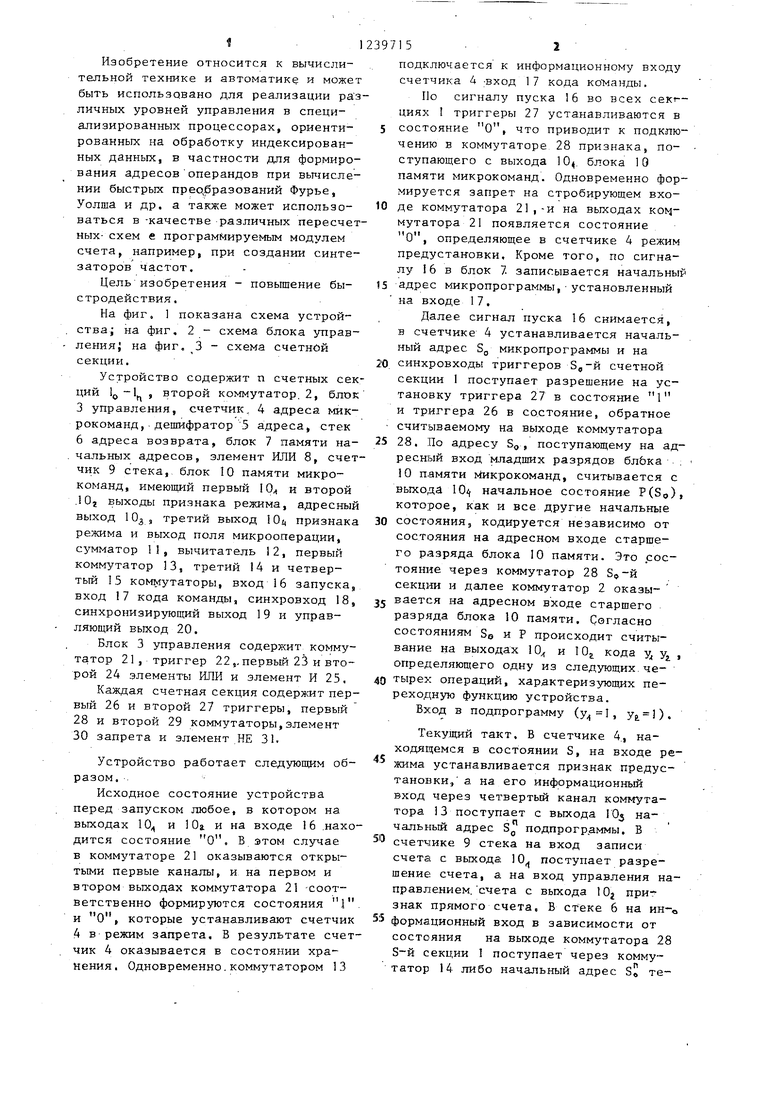

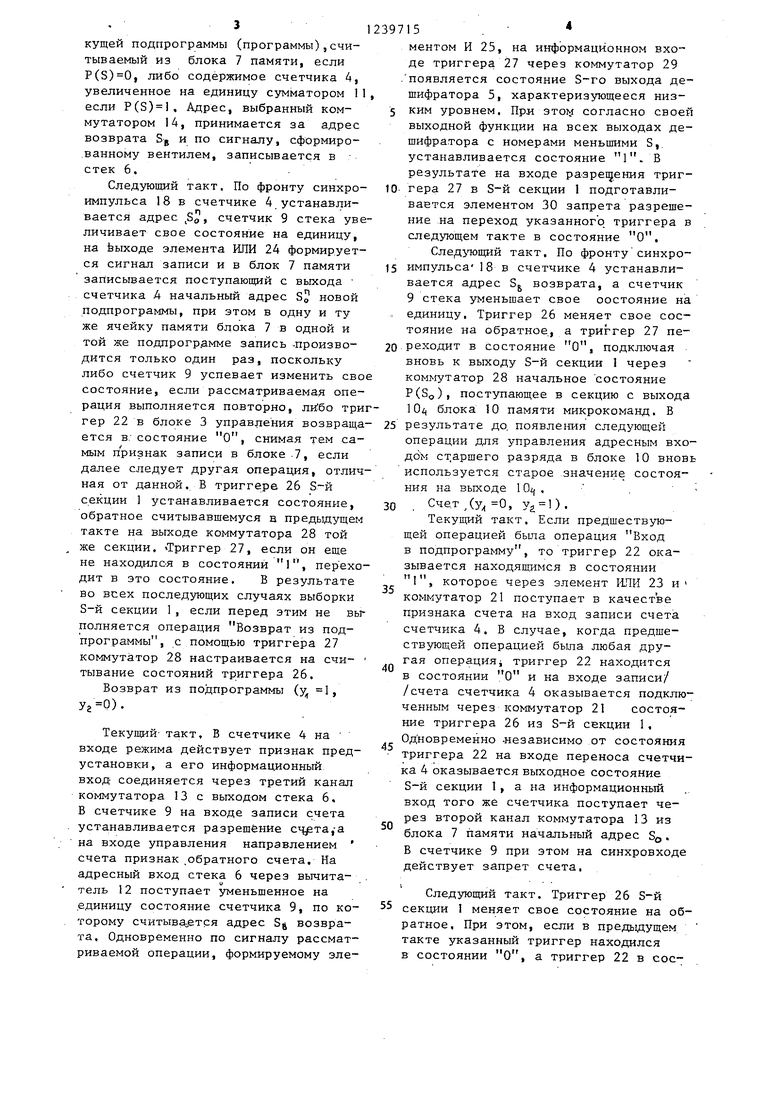

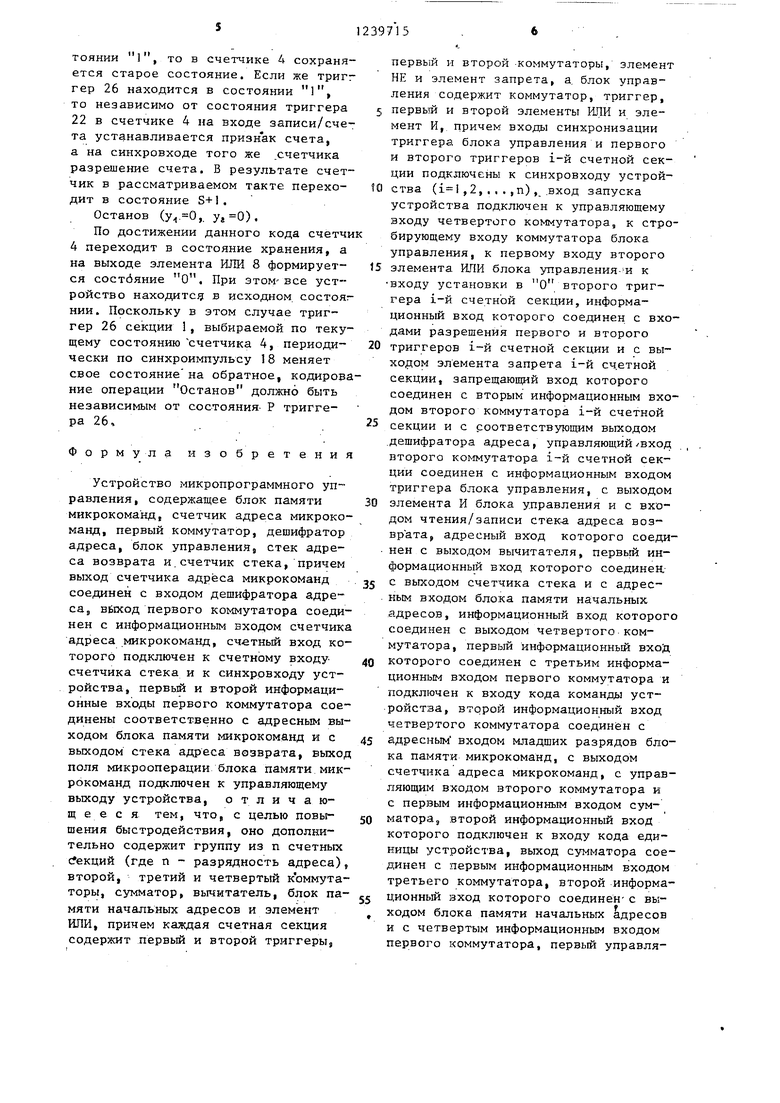

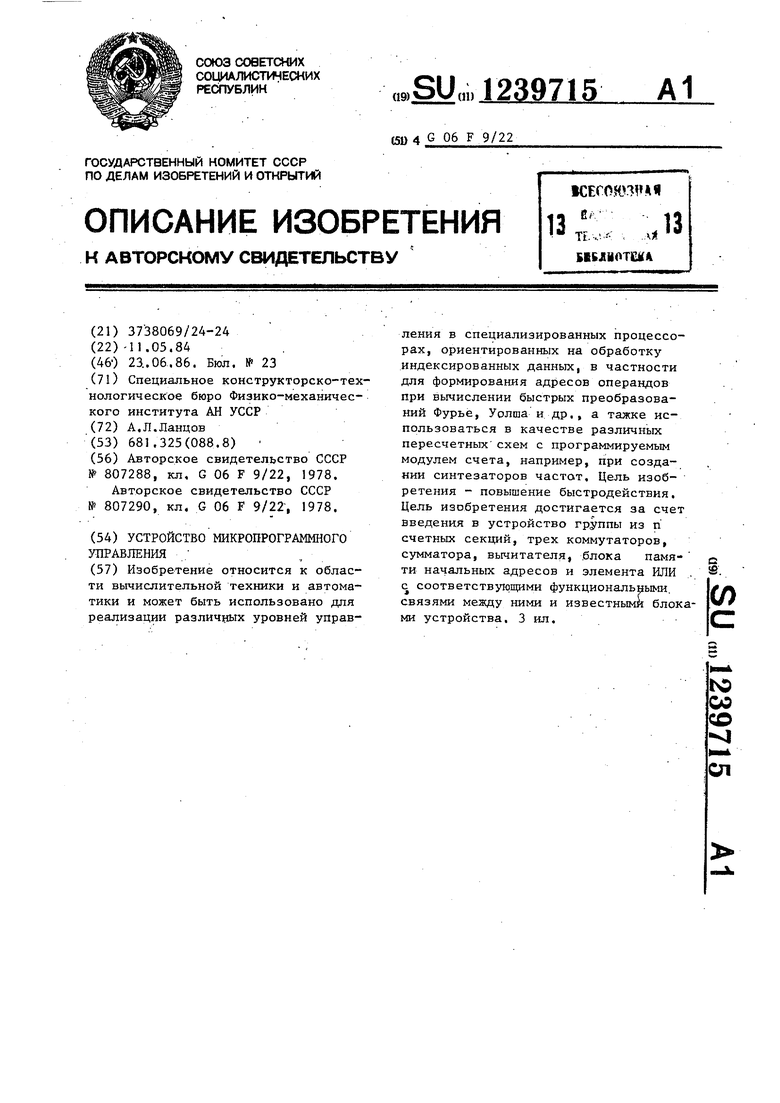

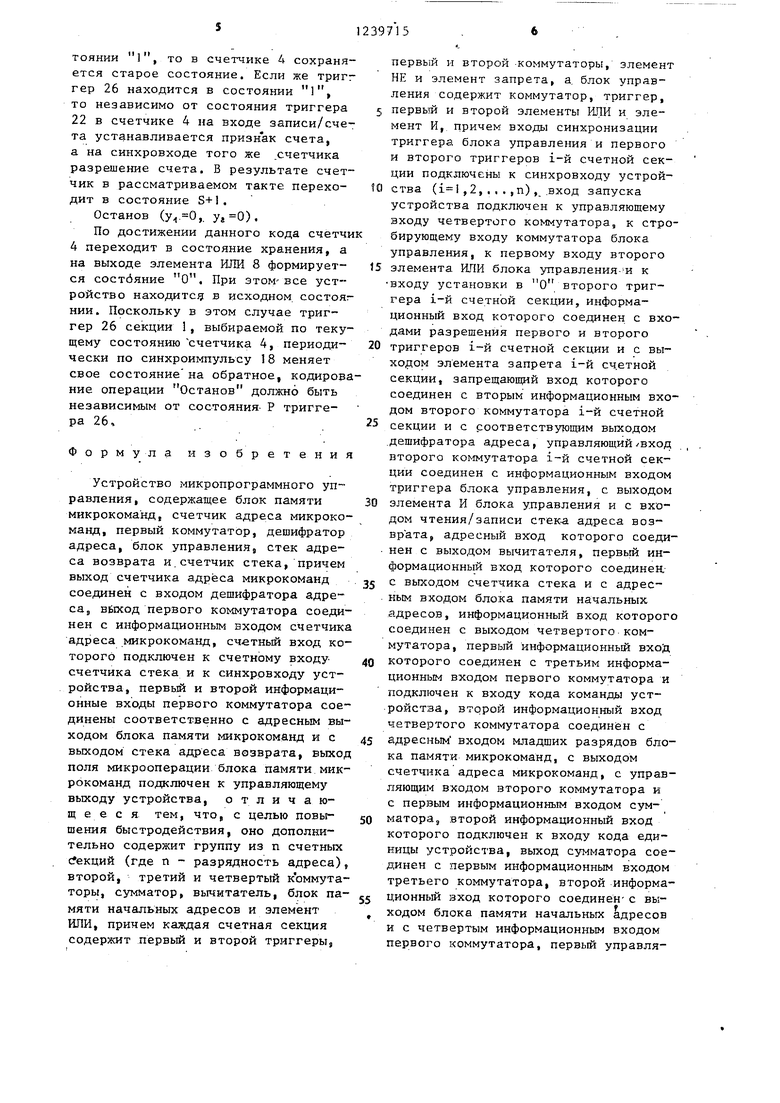

На фиг, 1 показана схема устройства; на фиг. 2 - схема блока управ- ления на фиг. 3 - схема счетной секции.20.

Устройство содержит п счетных секций о L i второй коммутатор. 2, блок 3 управления, счетчик, 4 адреса микрокоманд, - дешифратор 5 адреса, стек 6 адреса возврата, блок 7 памяти на- 25 чальных адресов, элемент ИЛИ 8, счетчик 9 стека, блок 10 памяти микрокоманд, имеющий первый 10 и второй .lOf выходы признака режима, адресный выход Юз, третий выход 0,i, признака 30 режима и выход поля микрооперации, сумматор П, вычитатель 12, первый коммутатор 13, третий 14 и четвертый 15 коммутаторы, вход 16 запуска, вход 17 кода команды, синхровход 18, 35 синхронизирующий выход 19 и управляющий выход 20.

Блок 3 управления содержит коммутатор 21, триггер 22,, первьй 23 и второй 24 элементы РШИ и элемент И 25. 40

Каждая счетная секция содержит первый 26 и второй 27 триггеры, первый 28 и второй 29 коммутаторы,элемент 30 запрета и элемент НЕ 31.

Устройство работает следующим образом. .

Исходное состояние устройства перед запуском любое, в котором на выходах 10 и 10а и на входе 16 .находится состояние О. В этом случае 50 в коммутаторе 21 оказываются открытыми первые каналы, и на первом и втором выходах коммутатора 21 -соответственно формируются состояния 1

и О, которые устанавливают счетчик 4 в режим запрета. В результате счетчик 4 оказывается в состоянии хранения. Одновременно.коммутатором 13

0.

5 0 5

0

0

5

15 2

подключается к информационному входу счетчика 4 -вход 17 кода ко манды.

Но сигналу пуска 16 во всех сек1- циях 1 триггеры 27 устанавливаются в состояние О, что приводит к подключению В; коммутаторе 28 признака, поступающего с выхода 10. блока 10 памяти микрокоманд. Одновременно формируется запрет на стробирующем входе коммутатора 21,-и на выходах кон мутатора 21 появляется состояние О, определяющее в счетчике 4 режим предустановки. Кроме того, по сигналу 16 в блок 7. записывается начальные адрес микропрограммы,установленный на входе 17.

Далее сигнал пуска 16 снимается, в счетчике 4 устанавливается начальный адрес Sg микропрограммы и на синхровходы триггеров S,-и счетной секции I поступает разрешение на установку триггера 27 в со,сто яние 1 и триггера 26 в состояние, обратное считываемому на выходе коммутатора 28. По адресу S,, , поступающему на адресный вход младших разрядов блбка : 10 памяти 1икрокоманд, считывается с выхода 10 начальное состояние P(So), которое, как и все другие начальные состояния, кодируется независимо от состояния на адресном входе старшего разряда блока 10 памяти. Это состояние через коммутатор 28 8(,-й секции и далее коммутатор 2 оказывается на адресном входе старшего разряда блока 10 памяти. Согласно состояниям Se и Р происходит считывание на выходах 10 и 10 кода у, yj, , определяющего одну из следующих.четырех операций, характеризующих переходную функцию устройства.

Вход в подпрограмму (, Уг. ).

Текущий такт. В счетчике 4., находящемся в состоянии S, на входе режима устанавливается признак предустановки, а на его информационный вход через четвертый канал коммутатора 13 поступает с выхода Г0.5 начальный адрес S подпрограммы. В счетчике 9 стека на вход записи счета с выхода 10 поступает разрешение счета, а на вход управления направлением, счета с выхода lOj при знак прямого счета 8 В стеке 6 на ин-в формационный вход в зависимости от состояния на выходе коммутатора 28 S-й секции 1 поступа.ет через коммутатор 14 либо начальный адрес s те3

кущей подпрограммы (программы),считываемый из блока 7 памяти, если P(S)0, либо содержимое счетчика А, увеличенное на единицу сумматором 1 если P(S)1, Адрес, выбранный ком- мутатором 14, принимается за адрес возврата Sg и по сигналу, сформированному вентилем, записывается в стек 6.

Следующий такт. По фронту синхро- импульса 18 в счетчике 4 устанавливается адрес SQ, счетчик 9 стека увеличивает свое состояние на единицу, на Ьыходе элемента ИЛИ 24 формируется сигнал записи и в блок 7 памяти записывается поступающий с выхода счетчика Л начальный адрес S новой подпрограммы, при этом в одну и ту же ячейку памяти блока 7 в одной и той же подпрогрдмне запись -произво- дится только один раз, поскольку либо счетчик 9 успевает изменить сво состояние, если рассматриваемая операция выполняется повторно, тригер 22 в блоке 3 управления возвраща ется в; состояние О, снимая тем самым признак записи в блоке .7, если далее следует другая операция, отличная от данной. В триггере 26 S-й секции 1 устанавливается состояние, обратное считывавшемуся а предьщущем такте на выходе коммутатора 28 той же секции, «Триггер 27, если он еще не находился в состоянии 1, переходит в это состояние. В результате во всех последующих случаях выборки S-й секции 1, если перед этим не выполняется операция Возврат из подпрограммы, с помощью триггера 27 коммутатор 28 настраивается на счн- тывание состояний триггера 26,

Возврат из подпрограммы (у 1, ),

Текущий- такт, В счетчике 4 на входе режима действует признак предустановки, а его информационный вход соединяется через третий канал коммутатора 13 с выходом стека 6. В счетчике 9 на входе записи счета устанавливается разрешение ,-а на входе управления направлением счета признак .обратного счета. На адресный вход стека 6 через вычита- гель 12 поступает уменьшенное на единицу состояние счетчика 9, по которому считыва ется адрес Sj возврата. Одновременно по сигналу рассматриваемой операции, формируемому эле

- s 0 5 о

5

0

5

0

5

15 . ментом И 25, на информационном входе триггера 27 через коммутатор 29 появляется состояние S-ro выхода дешифратора 5, характеризующееся низким уровнем, Прн этом согласно своей выходной функции на всех выходах дешифратора с номерами меньшими S,. устанавливается состояние 1. В результате на входе разрешения триггера 27 в S-й секции 1 подготавливается элементом 30 запрета разрешение на переход указанного триггера в следующем такте в состояние О,

След} тощий такт. По фронту синхроимпульса 18 в счетчике 4 устанавливается адрес Sj возврата, а счетчик 9 стека уменьшает свое оостояние на единицу. Триггер 26 меняет свое состояние на обратное., а триггер 27 переходит в состояние О, подключая вновь к выходу S-й секции 1 через коммутатор 28 начальное состояние P(SO), поступающее в секцию с выхода 1 Oi, блока 10 памяти микрокоманд, В результате до. появления следующей операции для управления адресным входом сггаршего разряда в блоке 10 вновь используется старое значение состояния на выходе Юц , . Сче., Уг 1),

Текущий такт. Если предшествующей операцией бьша операция Вход в подпрограмму, то триггер 22 оказывается находящимся в состоянии I, которое через элемент 1ПИ 23 и коммутатор 21 поступает в качестве признака счета на вхо.д записи счета счетчика 4, В случае, когда предшествующей операцией была любая другая операцияi триггер 22 находится в состоянии О и на входе записи/ /счета счетчика 4 оказывается подключенным через коммутатор 21 состояние триггера 26 из S-й секции 1, Одновременно -независимо от состояния триггера 22 на входе переноса счетчн- ка 4 оказывается выходное состояние S-й секции 1, а на информационный вход того же счетчика поступает через второй канал коммутатора 13 из блока 7 памяти начальный адрес Sg, В счетчике 9 при этом на синхровходе действует запрет счета.

Следующий такт. Триггер 26 S-й секции 1 меняет свое состояние на обратное. При этом, если в предыдущем такте указанный триггер находился в состоянии О, а триггер 22 в соетоянии l, то в счетчике 4 сохраняется старое состояние. Если же тригг гер 26 находится в состоянии 1, то независимо от состояния триггера 22 в счетчике 4 на входе записи/счета устанавливается призн ак счета, а на синхровходе того же .счетчика разрешение счета. В результате счетчик в рассматриваемом такте перехо- дит в состояние S+1.

Останов (у.0,. Уг 0) .

По достижении данного кода счетчи 4 переходит в состояние хранения, а на выходе элемента ИЛИ 8 формирует- ся состояние О. При этом-все устройство находите) в исходном состоянии. Поскольку в этом случае триггер 26 секции 1, выбираемой по текущему состоянию счетчика 4, периоди- чески по синхроимпульсу 18 меняет свое состояние на обратное, кодирование операции Останов должно быть независимым от состояния- Р триггера 26,

Формула изобретения

Устройство микропрограммного управления, содержащее блок памяти микрокома нд, счетчик адреса микрокоманд, первый коммутатор, дешифратор адреса, блок управления, стек адреса возврата и.счетчик стека, причем выход счетчика адреса микрокоманд соединен с входом дешифратора адреса, вбгход первого коммутатора соединен с информационным входом счетчика адреса микрокоманд, счетный вход которого подключен к счетному входу счетчика стека и к синхррвходу устройства, первьй и второй информационные входы первого коммутатора соединены соответственно с адресным выходом блока памяти микрокоманд не выходом стека адреса возврата, выход поля микрооперации блока памяти микрокоманд подключен к управляющему выходу устройства, о т л и ч а ю щ ее с я тем, что, с целью повы- шения быстродействия, оно дополнительно содержит группу из п счетных с екций (где п - разрядность адреса), второй, третий и четвертый коммутаторы, сумматор, вычитатель, блок па- мяти начальных адресов и элемент ИЛИ, причем каждая счетная секция содержит первый и второй триггеры,

первый и второй -коммутаторы, элемент НЕ и элемент запрета, а, блок управления содержит коммутатор, триггер, первый и второй элементы ИЛИ и элемент И,, причем входы синхронизации триггера блока управления и первого и второго триггеров i-й счетной секции подключены: к синхровходу устройства (i 1 ,2, , , . ,п), .вход запуска устройства подключен к управляющему входу четвертого коммутатора, к стро- бирующему входу коммутатора блока управления, к первому входу второго элемента ИЛИ блока управления--и к входу установки в О второго триггера i-й счетной секции, информационный вход которого соединен с входами разрешения первого и второго триггеров i-й счетной секции и с выходом эл емента запрета i-й счетной секции, запрещающий вход которого соединен с вторым информационным входом второго коммутатора 1-й счетной секции и с соответствующим выходом .дешифратора адреса, управляющий/вход второго коммутатора 1-й счетной секции соединен с информационным входом триггера блока управления, с выходом элемента И блока управления и с входом чтения/записи стек-а адреса воз врата, адресный вход которого соединен с выходом вычитателя, первьш информационный вход которого соединен,- с выходом счетчика стека и с адресным входом блока памяти начальных адресов, информационный вход которог соединен с выходом четвертого-коммутатора, первьш информационный вход которого соединен с третьим информа- ционньм входом первого коммутатора и подключен к входу кода команды уст- -ройстза, второй информационный вход четвертого коммутатора соединён с адресным входом младших разрядов блока памяти микрокоманд, с выходом счетчика адреса микрокоманд, с управляющим входом второго коммутатора и с первым информационным входом сумматора, второй информационный вход которого подключен к входу кода единицы устройства, выход сумматора соединен с первым информационным входом третьего коммутатора, второй информа ционньй ;зход которого соединен- с выходом блока памяти начальных адресов и с четвертым информационным входом первого коммутатора, первый управля71

ющий вход которого соединен с первым выходом признака режима блока памяти микрокоманд, с первым входом.элемента И блока управления с первым входом коммутатора блока управления, с пер- вым входом элемента ИЛИ и со счетным входом счетчика стека, вход управле- НИН направлением счета которого соединен с вторым выходом признака режима блока памяти микрокоманд, с вто- рым управляющим входом первого коммутатора, с входом элемента ИЛИ, с вторым информационным входом вычитат еля, с вторым входом элемента И блока уп- равления и с вторым управляющим вхо- дом коммутатора блока управления, первая и вторая группы информационных входов и первый информационный вход третьей группы которого подключены к шине нулевого потенциала уст- ройства, первый и второй информационные входы четвертой группы коммутатора блока управления соединены соответственно с выходом первого элемента ИЛИ блока управления и с вхо- дом единичного потенциала устройства, второй информационный вход третьей группы коммутатора блока управления соединен с вторым входом первого элемента JfflH блока управления, с вы- ходом второго коммутатора, с адрес- ;Ным входом старшего разряда блока памяти микрокоманд и с управляющим входом третьего коммутатора, выход

158 .

которого соединен с информационным входом стека адреса возврата, выход элемента ИЛИ является синхронизирующим выходом устройства, третий выход признака режима блока памяти микрокоманд соединен с первым информационным входом первого коммутатора i-й счетной секции, второй информационный вход которого соединен с выходом первого триггера i-й счётной секции, информационный вход которого соединен с выходом элемента НЕ i-й счетной секции, вход которого соединен с выходом первого коммутатора i-й счетной секции и с i-M информационным входом второ.г.о коммутатора, информационный вход элемента запрета j-й счетной секции соединен . с соответствующим выходом дешифратора адреса (j 2,3,...,пХ, информационный вход элемента запрета первой счетной секции соединен с входом единичного потенциала устройства, выход второго триггера i-й счетной секции соединен с управляющим входом первого ког тутатора i-й счетной секции, вход чтения/записи блока памяти начальных адресов соединен с выходом второго элемента ИЛИ блока управления, второй вход которого соединен с выходом триггера блка управления и с вторым входом первого элемента ИЛИ блока зшравления.

./

z а

23

25

в, Ot

Фиг.2

Jj %

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1304023A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Изобретение относится к области вычислительной техники и автоматики и может быть использовано для реализации различных уровней управления в специализированных процессорах, ориентированных на обработку индексированных данных, в частности для формирования адресов операндов при вычислении быстрых преобразований Фурье, Уолша и др., а тгикке использоваться в качестве различных пересчетных схем с программируемым модулем счета, например, при создании синтезаторов частот. Цель изобретения - повышение быстродействия. Цель изобретения достигается за счет введения в устройство группы из п счетных секций, трех коммутаторов, сумматора, вычитателя, .блока памя- ти начальных адресов и элемента ИЛИ , с соответствующими функциональными, связями между ними и известными блоками устройства. 3 ил. i. (Л ю оо со ел

Составитель Ю.Ланцов Редактор Е.Папп Техред Л.Олейник

.Заказ.3397/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г, Ужгород, ул. Проектная, 4

Корректор Е.Сирохман

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807288A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-05-11—Подача