1

Изобретение относится к вычислительной технике, а именно к устройствам для сравнения чисел.

Известно устройство для сравнения двух fj -разрядных чисел, содержащее блок результата сравнения и формирователи четных и нечетных разрядов вспомО-Тательного кода, причем каждый из формирователей нечетного разряда вспомогательного кода содержит четыре элемента И, соединенных с элементом ИЛИ-НЕ, первые входы первого и второго элементов И соединены с первым входЬм этого формирователя, второй вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы первого и третьего элементов И соединены с третьим входом, а вторые входы второго и четвертого элементов И соединены о четвертым входом того же формирователя, а каждый из формирователей четного разряда вспомогательного кода содержит два элемента И, соединенных с элементом , при этом первый и второй входы первого элемента И соединены с первым и вторым входом четных разрядов формирователя, третий и четвертый входы которогс соединены с первым и вторым входом второго элемента И, блок результата сравнени содержит (tt +1) элементов И, соединенных с элементом ИЛИ-НЕ, причем каждый эле мент И с номером i+1 (i 1 ( ft+1) имеет (1+2} входа, первый из которых соединен с первым входом блока результата сравнения, второй - со вторым входом этого блока I -ый вход соединен с Д /2ым входом, а ( t +1)-ые входы всех, кроме первого, элементов И соединены соответственно с (fl /2 + 1) f ( Г -1) входами блока результата сравнения, П -ый и (/I +1)-ый f входы которого соединены с пер- вым и вторым входами первого элемента И. Известное устройство характеризуется невысоким быстродействием.

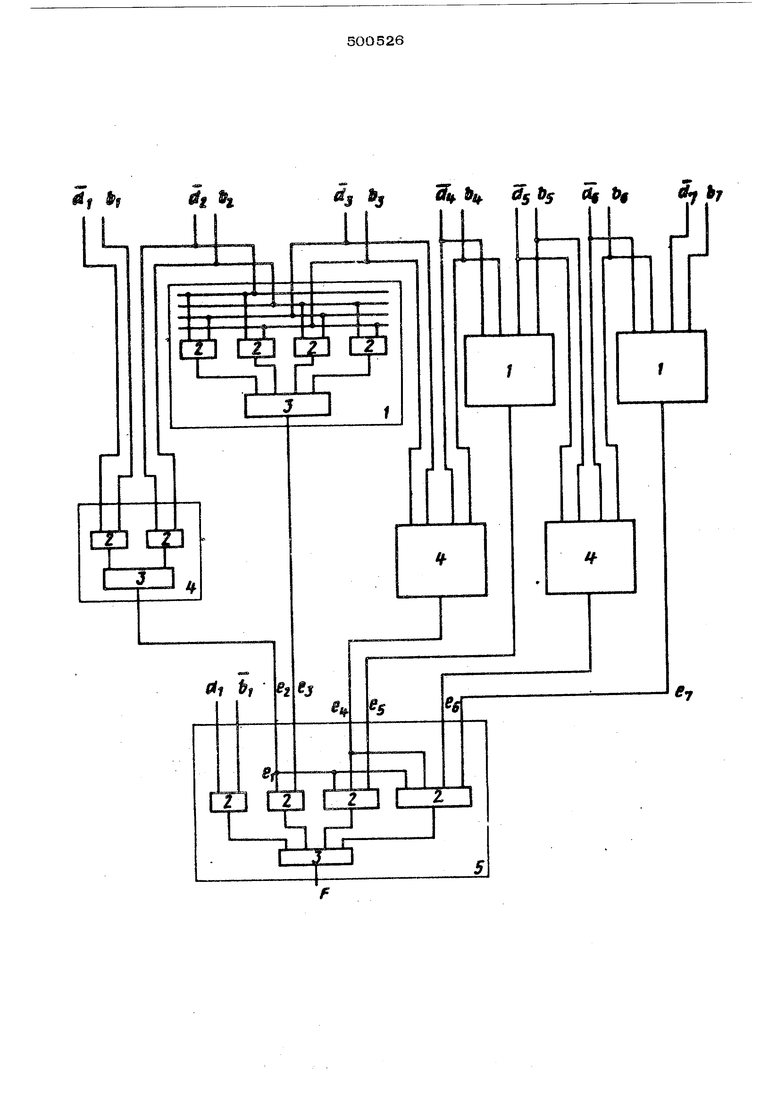

Для увеличения быстродействия в предлагаемом устройстве входы первых (стп)- ших) разрядов сравниваемых чисел соединены соответственно с fl -ым и (f +1)-ым входами блока сравнения результата, иходы любого нечетного, кроме старшого, 1П.зря- да обоих сравниваек ых чисел соолин ны 3. / со вторым и третьим входами соотввтст . вующих формирователей нечетных разрядов и первым и вторым входами соответствующих формирователей четных разрядов , вспсмагатвльного кода, третий и четвертый входы который соединены с соответствующими четными разрядами сравниваемых чисел, соединенными также с первым и вторым входами соответствующих .формирователей нечетных разрядов, . На чертеже изображена блок-схема пре лагаемого устройства. Устройство содержит формирователи 1 .. четных разрядов вспомогательного кода, J; входы которых соединены с шинами двух смежных разрядов, начиная со второго, ft разрядных сравниваемых чисел, из которых состоит из четырех элементов И 2 соединенных с элементом ИЛИ-НЕ 3, реал зующих следующую логическую формулу; e,a-,-d.ai., bi, } где а, Ь - разряды сравниваемых чисе е- выходной сигнал формирова i- номер разряда. Входы каждого формирователя 4 четных разрядов вспомогательного кода соединены с шинами двух смежных разрядов, начиная с первого, сравниваемых чисел. Формирователи 4 содержат по два элем та И 2, соединенных с элементом ИЛИ-Н и реализующих следующую логическую форм лу: ег а., Ь.., +а, bz Блок 5 результата сравнения содержит (fl t-1/2) элементов И 2, соединенных с элементом ИЛИ-НЕ 3, и реализует следую . щую логическую формулу: F--e,,,v...ye2e..e,e где F - выходной сигнал блока и устройстпа;1 1 Работа уст;юнства рассматривается на примере сравнения двух чисел А, В при Устройство работает следующим образо Пусть сравниваемые числа имеют следу ющий вид: . А 1010 J О111; В ото 0101. Вспомогательный код на выходах формиропптелей 1 и 2 е ОО11О11. rivm этом на вход блока 5 результата поступает число е 1О ООО1 1О11. Нл В1,1ходо блока 5 формируется сигнал Г О, что о;(ччает А В. В случае, если А В, выходной сигнал F 1. Задержка устройства составляет 2 Т , где Г - задержка нескольких элементов И. объединенных по схеме ИЛИ-НЕ. Предмет нао.бретен.яя Устройство для сравнения ft -разрядньйс чисел, содержащее блок результата сравнения- в формирователи четных и нечетных paijpfiflOB вспомогатепьнсго ; кода, причем каждый из формирователей нечетного разряда ; вспокюгатепьного кода содержит четыре элемента И, соединенных с элементом ИЛИНЕ, первые входы первого и второго, элементов И соединены с первым входом формирователя нечетных разрядов, второй вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы первого и третьего элементов И со чинены с третьим входом, а вторые входы второго- и четвертого элементов И, соединены с четвертым входом формирователя нечетных разрядов, Каждый из формирователей четного разряда вспомомгательного кода содержит два элемента И, соединенных с элементом ИЛИ-{ НЕ, при этом первый и второй входы первого элемента И соединены с первым и вторым входами четных разрядов формирователя, третий и четвертый входы которого соединены с первым и вторым входами второго элемента И, а блок результата сравнения содержит ( Л +1) элементов И, соединенных с элементом ИЛИ-НЕ, причем каждый элемент И, с номером i +1 ( -(Л +1) имеет / +2 входа, первый из которых соединен с первым входом блока результата сравнения, второй со вторым входом этого блока, i -ый вход соединен и входом, а(1 +1)-ые входы всех, кроме первого элементов И соединены соответственно с ( Л/2+1) (-1) входами блока результата сравнения, Д -и и ( )-ый входы которого соединены с первым и вторым входами первого элемента И, отличающееся тем, что, с целью увеличения быстродействия, старшие разряды сравниваемых чисел соединены соответственно с fi-ым и { П- +1)-ым входами блока сравнения результата, нечетные, кроме стар. шего, разряды сравниваемых чисел соединены со вторым и третьим входами соответствующих формирователей нечетных разрядов и первым и вторым входами соответствующих формирователей четных разрядов вспомогательного кода, третий и четвертый входы которых соединены с соответствующими четными разрядами сравниваемых чисел, соединенными также с первым и вторым входами соответствующих формирователей нечетных разрядов.

f У

j |P|2 frj % 5 (% b;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1978 |

|

SU798809A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| Устройство для упорядочения чисел | 1980 |

|

SU932488A1 |

| ОБНАРУЖИТЕЛЬ ФАЗОКОДИРОВАННЫХ СИГНАЛОВ | 1990 |

|

SU1818985A1 |

| Устройство для определения экстремального числа | 1981 |

|

SU981987A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1474746A2 |

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1978 |

|

SU746528A1 |

I I I I

Г f I f

I rTi 4

f bt

ej

ц.

7

Авторы

Даты

1976-01-25—Публикация

1973-06-06—Подача