11474746

. Изобретение относится к вычислиельной технике, в частности к запоинающим устройствам с автономным онтролем и является усовершенствоваием технического решения по авт.св. 1325570.

Целью изобретения является повышеие достоверности контроля устройста.10

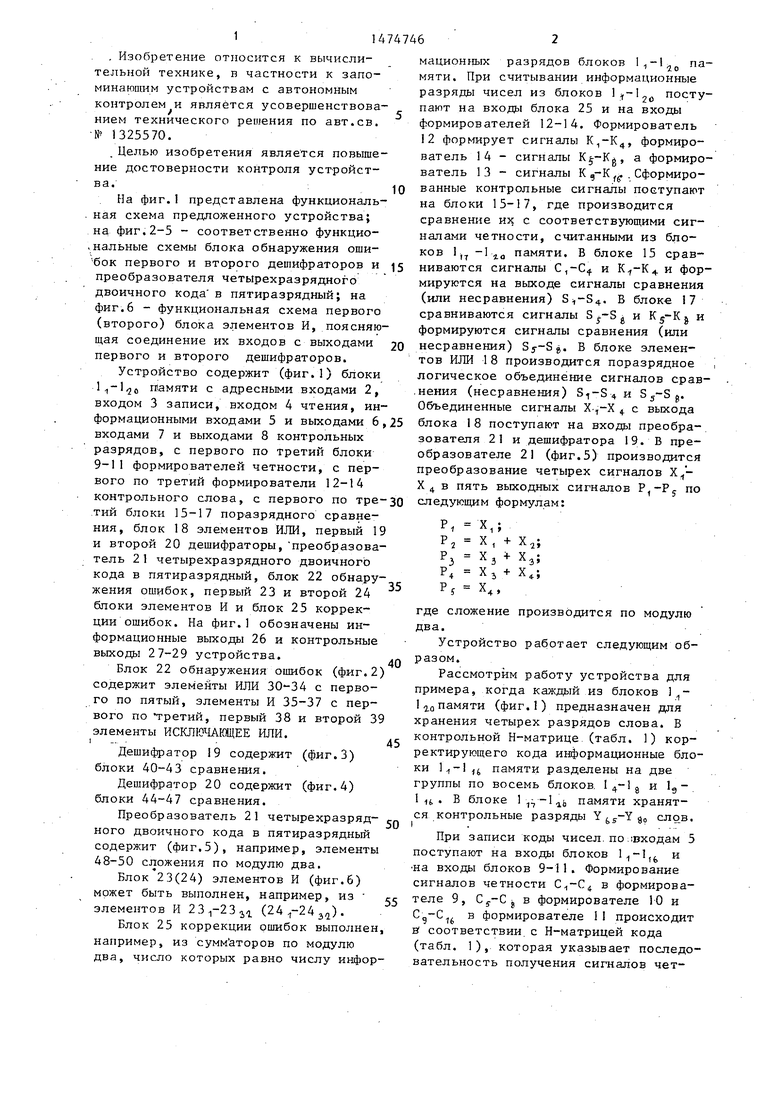

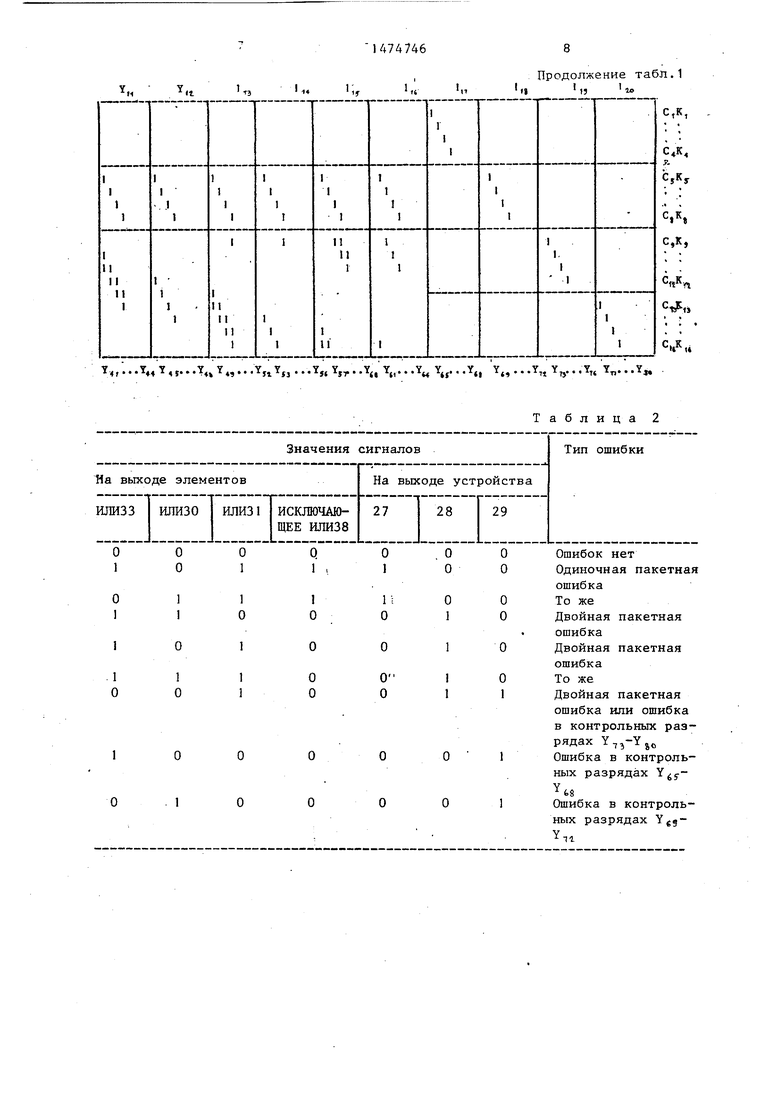

На фиг.1 представлена функциональая схема предложенного устройства; а фиг.2-5 - соответственно функцио- альные схемы блока обнаружения ошиок первого и второго дешифраторов и J5 преобразователя четырехразрядного двоичного кода в пятиразрядный; на фиг.6 - функциональная схема первого (второго) блока элементов И, поясняющая соединение их входов с выходами 20 первого и второго дешифраторов.

Устройство содержит (фиг.1) блоки памяти с адресными входами 2, входом 3 записи, входом 4 чтения, информационными входами 5 и выходами 6,25 входами 7 и выходами 8 контрольных разрядов, с первого по третий блоки 9-11 формирователей четности, с первого по третий формирователи 12-14 контрольного слова, с первого по тий блоки 15-17 поразрядного сравнения, блок 18 элементов ИЛИ, первый 19 и второй 20 дешифраторы, преобразователь 2 1 четырехразрядного двоичного кода в пятиразрядный, блок 22 обнаружения ошибок, первый 23 и второй 24 блоки элементов И и блок 25 коррекции ошибок. На фиг.1 обозначены информационные выходы 26 и контрольные выходы 27-29 устройства.

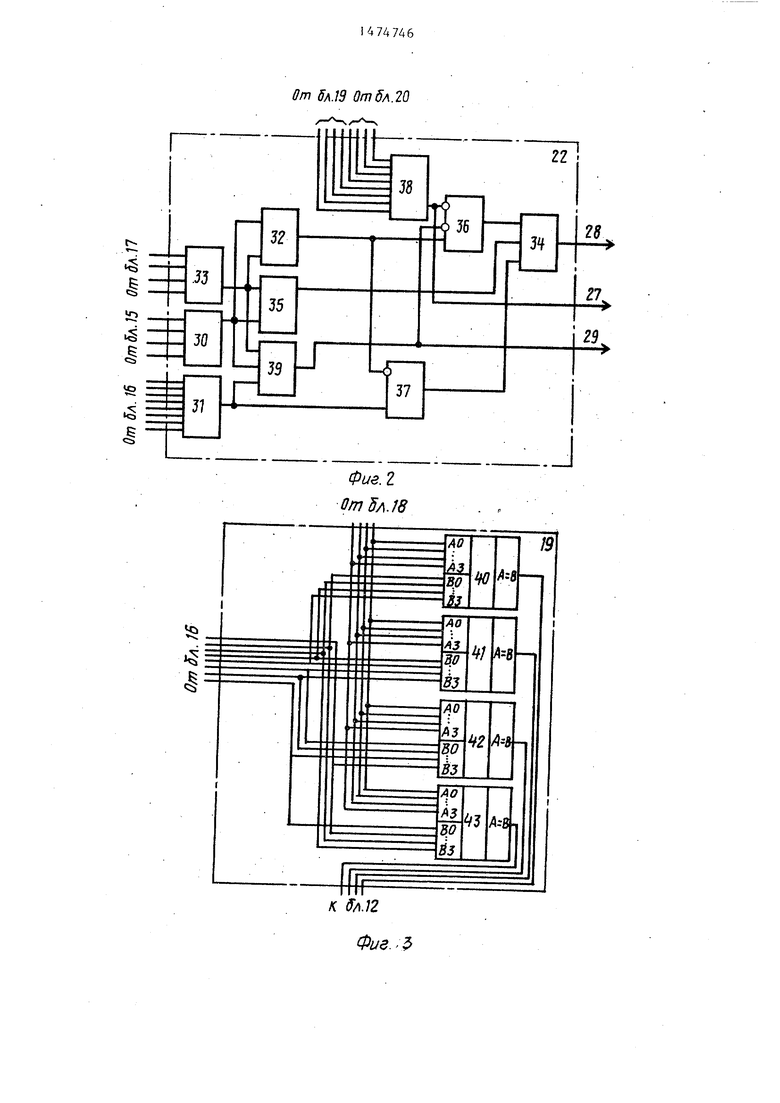

Блок 22 обнаружения ошибок (фиг.2) содержит элементы ИЛИ 30-34 с первого по пятый, элементы И 35-37 с первого по третий, первый 38 и второй 39

элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

i

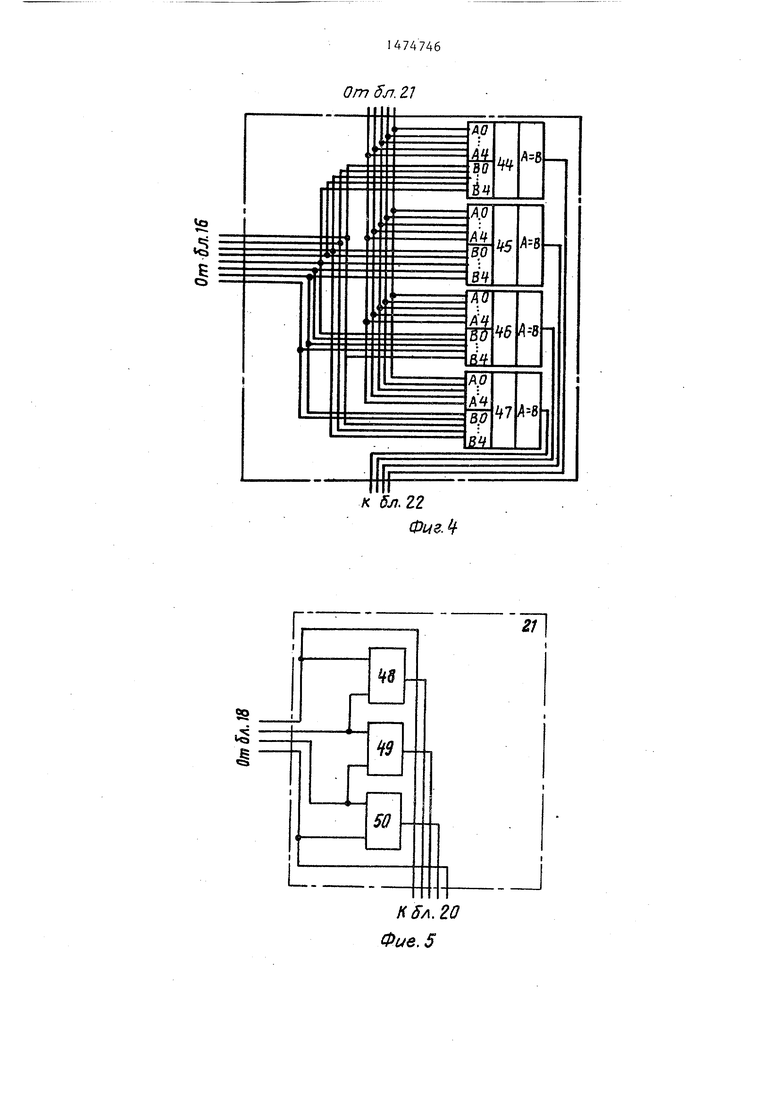

Дешифратор 19 содержит (фиг.З) блоки 40-43 сравнения.

Дешифратор 20 содержит (фиг.4) блоки 44-47 сравнения.

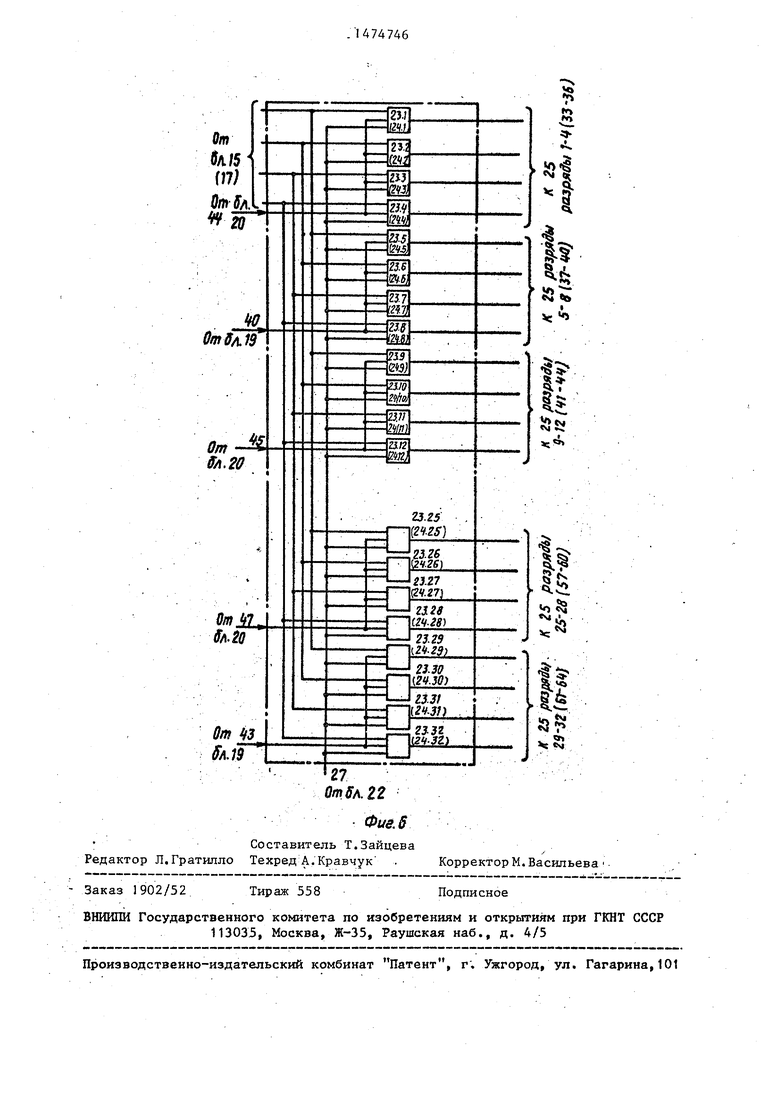

Преобразователь 21 четырехразрядного двоичного кода в пятиразрядный содержит (фиг.5), например, элементы 48-50 сложения по модулю два.

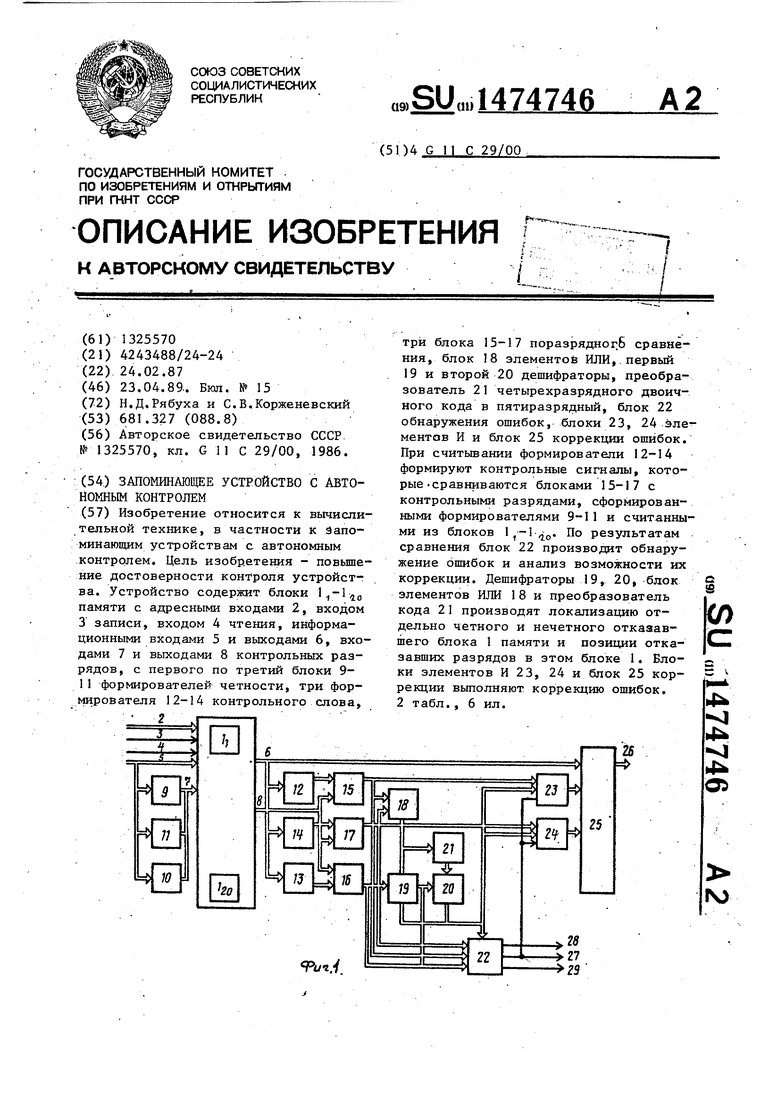

Блок 23(24) элементов И (фиг.б) может быть выполнен, например, из гс элементов И 23 .,-233-1. (24 .,-24 3/1).

Блок 25 коррекции ошибок выполнен, например, из сумматоров по модулю два, число которых равно числу инфор35

40

45

50

1

н

мационных разрядов блоков памяти. При считывании информационные разряды чисел из блоков поступают на входы блока 25 и на входы формирователей 12-14. Формирователь 12 формирует сигналы К1-К4, формирователь 14 - сигналы Kj-Kg, а формирователь 13 - сигналы К ,-К1ff Сформированные контрольные сигналы поступают на блоки 15-17, где производится сравнение их с соответствующими сигналами четности, считанными из блоков 1,7 -1 го памяти. В блоке 15 сравниваются сигналы С,-С4 и Kf-K4 и формируются на выходе сигналы сравнения (или несравнения) S1-S4. В блоке 17 сравниваются сигналы и и формируются сигналы сравнения (или несравнения) Sj-Sg. В блоке элементов ИЛИ 18 производится поразрядное логическое объединение сигналов сравнения (несравнения) S1-S 4 и S5-Se. Объединенные сигналы X,-Х+ с выхода блока I8 поступают на входы преобразователя 21 и дешифратора 19. В преобразователе 21 (фиг.5) производится преобразование четырех сигналов X/- Х4 в пять выходных сигналов Р,Р5 по следующим формулам:

PI Р,

X X

1

:х

х3 +

2 3

Рс X

4

где сложение производится по модулю два.

Устройство работает следующим образом.

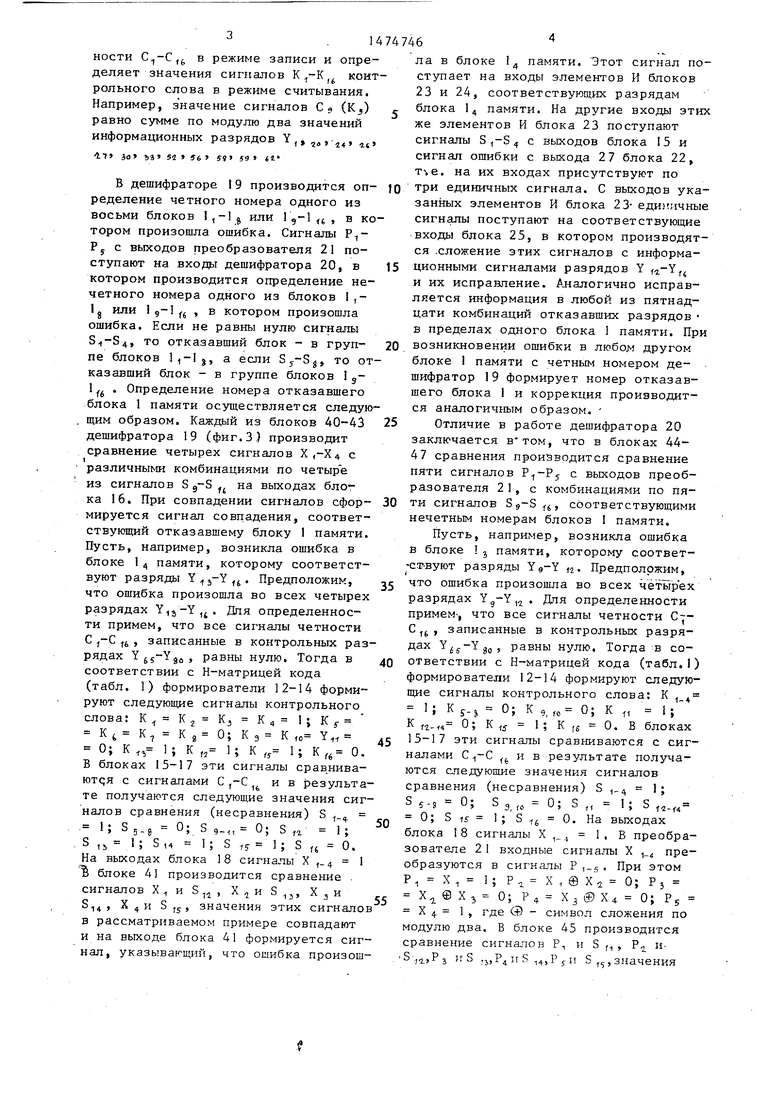

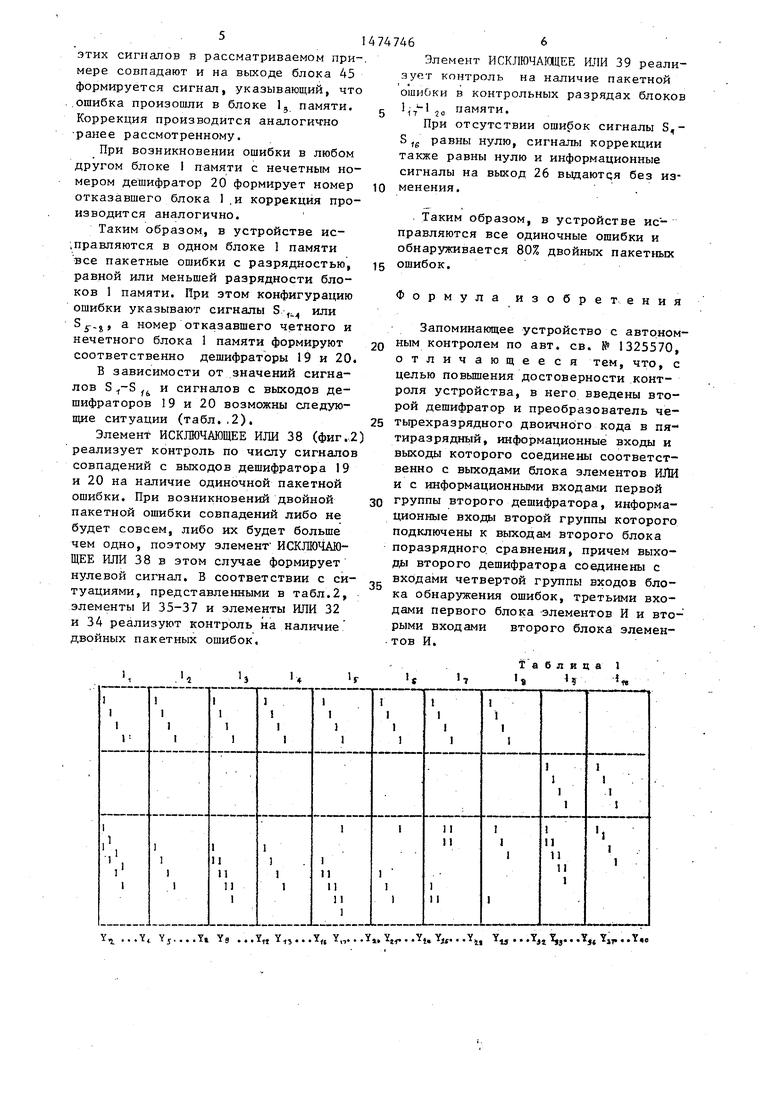

Рассмотрим работу устройства для примера, когда каждый из блоков I1- Iгапамяти (фиг.1) предназначен для хранения четырех разрядов слова. В контрольной Н-матрице (табл. 1) корректирующего кода информационные блоки ,6 памяти разделены на две группы по восемь блоков 14-18 и 19- I u . В блоке 1 17-1а(5 памяти хранятся контрольные разряды Yfes-Y9o слов.

При записи коды чисел по ;входам 5 поступают на входы блоков l.,-l(t и на входы блоков 9-11. Формирование сигналов четности С.,-С4 в формирователе 9, Су-С в формирователе 10 и Сд-С16 в формирователе II происходит и соответствии с Н-матрицей кода (табл. I), которая указывает последовательность получения сигналов четности C1-C,t

в режиме записи и определяет значения сигналов (4 контрольного слова в режиме считывания. Например, значение сигналов С9 (К3) равно сумме по модулю два значений информационных разрядов Y,, 7а, 14, 4

17 40 Ъ4 54 Si, ) « 59 « 4

В дешифраторе 19 производится on- ределение четного номера одного из восьми блоков 1 -1 $ или 1 t в котором произошла ошибка. Сигналы Р1- РУ с выходов преобразователя 21 поступают на входы дешифратора 20, в котором производится определение нечетного номера одного из блоков Iт Ig или 1 9-1 (6 , в котором произошла ошибка. Если не равны нулю сигналы S.,-S4, то отказавший блок - в труп- пе блоков lj-Ij, а если Sj-Sg, то отказавший блок - в группе блоков 1д16

Определение номера отказавшего

блока 1 памяти осуществляется следующим образом. Каждый из блоков 40-43 дешифратора 19 (фиг.З) производит сравнение четырех сигналов Х,-Х4 с различными комбинациями по четыре из сигналов S 9-S 1t на выходах блока 16. При совпадении сигналов сформируется сигнал совпадения, соответствующий отказавшему блоку I памяти. Пусть, например, возникла ошибка в блоке 14 памяти, которому соответствуют разряды . Предположим, что ошибка произошла во всех четырех разрядах Y1S-YU. Для определенности примем, что все сигналы четности С 1Ь , записанные в контрольных раз

рядах Y6s-Y4o, равны нулю. Тогда в соответствии с Н-матрицей кода (табл. 1) формирователи 12-14 формируют следующие сигналы контрольного

К 4 1 ; К f К г 0; К э К ,„ Y

слова: К ,, К 2

Kt

о;

к7

К,у

К нi; к ,5 i; к

«

0.

В блоках 15-17 эти сигналы сравнива- ютс.я с сигналами С 7-С и в результате получаются следующие значения сигналов сравнения (несравнения) S I; S5.g 0; 39-., 0; Sf-2.

S- 1 С1

14 - I 5 Ь 75- - J ;

1Ь

и

1-Я

0.

На выходах блока 18 сиг S блоке 41 производится сигналов X ., и S

14

X .и S

п

X „ и

15

значения

в рассматриваемом примере совпадают и на выходе блока 41 формируется сигнал, указывающий, что ошибка произош5

JQ 152074746ц

ла в блоке 14 памяти. Этот сигнал по25

30

35

40

ступает на входы элементов И блоков 23 и 24, соответствующих разрядам блока 14 памяти. На другие входы этих же элементов И блока 23 поступают сигналы S t-S 4 с выходов блока 15 и сигнал ошибки с выхода 27 блока 22, , на их входах присутствуют по три единичных сигнала. С выходов указанных элементов И блока 23- единичные сигналы поступают на соответствующие входы блока 25, в котором производятся сложение этих сигналов с информационными сигналами разрядов Y «-Yu и их исправление. Аналогично исправляется информация в любой из пятнадцати комбинаций отказавших разрядов в пределах одного блока 1 памяти. При возникновении ошибки в любом другом блоке 1 памяти с четным номером дешифратор 19 формирует номер отказавшего блока 1 и коррекция производится аналогичным образом. Отличие в работе дешифратора 20 заключается , что в блоках 44- 47 сравнения производится сравнение пяти сигналов с выходов преобразователя 21, с комбинациями по пяти сигналов S9-Sf6, соответствующими нечетным номерам блоков 1 памяти.

Пусть, например, возникла ошибка в блоке ъ памяти, которому соответствуют разряды п. Предположим, что ошибка произошла во всех четырех разрядах Y9-Y14. Для определенности примем, что все сигналы четности С-- Сп, записанные в контрольных разрядах Y5j-Y8o, равны нулю, Тогда в соответствии с Н-матрицей кода (табл.1) формирователи 12-14 формируют следующие сигналы контрольного слова: К

1-4

К,.,

0; К ,,„ 0; К f( 1;

К 0; К 5 1 ; К |в 0. В блоках 45 15-17 эти сигналы сравниваются с сигналами С1-С ,, и в результате получаются следующие значения сигналов сравнения (несравнения) S ,,4 I;

0

5

5 0;

Э, О

- Л Я 1 Ч - U , Ь f1 - 1 , и

0; S is I ; S 16 0. На выходах блока I 8 сигналы X ., , I . В преобразователе 2l входные сигналы X Ь4 преобразуются в сигналы Р ,, . При этом Р1 Х1 1;Р-1 Х1@Х2 0;Р3 Ха®Х3 0; Р4 X з © X 4 0; Р5 X 4 I, где ® - символ сложения по модулю два. В блоке 45 производится сравнение сигналов Р, и S

fi

и

1 S , з

и S ,г,Р,пЯ 1+,Pyii

:, значения

этих сигналов в рассматриваемом примере совпадают и на выходе блока 45 формируется сигнал, указывающий, что ошибка произошли в блоке ь памяти. Коррекция производится аналогично ранее рассмотренному.

При возникновении ошибки в любом другом блоке I памяти с нечетным номером дешифратор 20 формирует номер отказавшего блока 1 и коррекция производится аналогично.

Таким образом, в устройстве ис- .правляются в одном блоке 1 памяти все пакетные ошибки с разрядностью, равной или меньшей разрядности блоков 1 памяти. При этом конфигурацию ошибки указывают сигналы S т или , а номер отказавшего четного и нечетного блока 1 памяти формируют соответственно дешифраторы 19 и 20.

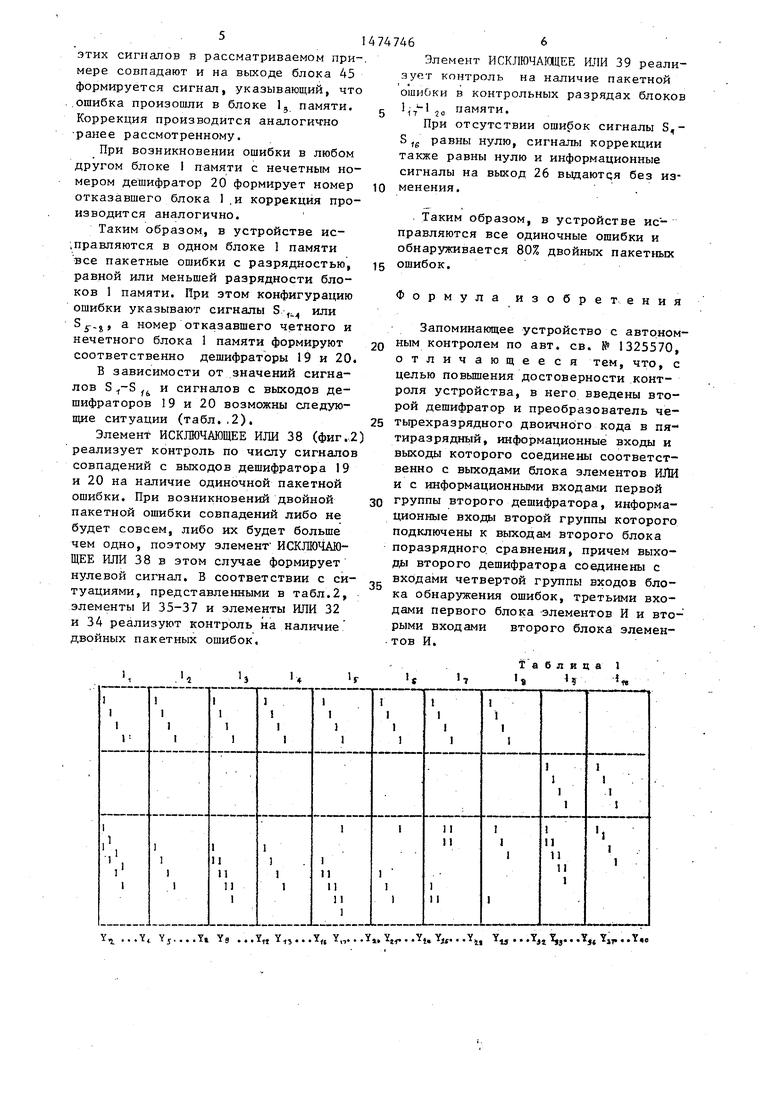

В зависимости от значений сигналов S .,-S f6 и сигналов с выходов дешифраторов 19 и 20 возможны следующие ситуации (табл..2).

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 38 (фиг.2 реализует контроль по числу сигналов совпадений с выходов дешифратора 19 и 20 на наличие одиночной пакетной ошибки. При возникновений двойной пакетной ошибки совпадений либо не будет совсем, либо их будет больше чем одно, поэтому элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 38 в этом случае формирует нулевой сигнал. В соответствии с ситуациями, представленными в табл.2, элементы И 35-37 и элементы ИЛИ 32 и 34 реализуют контроль на наличие двойных пакетных ошибок,

14747466

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 39 реализует контроль на наличие пакетной ошибки в контрольных разрядах блоков

го памяти.

При отсутствии ошибок сигналы S,- S is равны нулю, сигналы коррекции также равны нулю и информационные сигналы на выход 26 выдаются без изменения.

Таким образом, в устройстве исправляются все одиночные ошибки и обнаруживается 807, двойных пакетных 5 ошибок.

Формула изобретения

Запоминающее устройство с автоном- Q ным контролем по авт. св. № 1325570, отличающееся тем, что, с целью повышения достоверности контроля устройства, в него введены второй дешифратор и преобразователь че- 5 тырехразрядного двоичного кода в пятиразрядный, информационные входы и выходы которого соединены соответственно с выходами блока элементов ИЛИ и с информационными входами первой о группы второго дешифратора, информационные входы второй группы которого подключены к выходам второго блока поразрядного сравнения, причем выходы второго дешифратора соединены с входами четвертой группы входов блока обнаружения ошибок, третьими входами первого блока элементов И и вторыми входами второго блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

| Запоминающее устройство с автономным контролем | 1985 |

|

SU1262576A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с автономным контролем. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит блоки 11-12о памяти с адресными входами 2, входом 3 записи, входом 4 чтения, информационными входами 5 и выходами 6, входами 7 и выходами 8 контрольных разрядов, с первого по третий блоки 9-11 формирователей четности, три формирователя 12-14 контрольного слова, три блока 15-17 поразрядного сравнения, блок 18 элементов ИЛИ, первый 19 и второй 20 дешифраторы, преобразователь 21 четырехразрядного двоичного кода в пятиразрядный, блок 22 обнаружения ошибок, блоки 23,24 элементов И и блок 25 коррекции ошибок. При считывании формирователи 12-14 формируют контрольные сигналы, которые сравниваются блоками 15-17 с контрольными разрядами, сформированными формирователями 9-11 и считанными из блоков 11-12о. По результатам сравнения блок 22 производит обнаружение ошибок и анализ возможности их коррекции. Дешифраторы 19,20, блок элементов ИЛИ 18 и преобразователь кода 21 производят локализацию отдельно четного и нечетного отказавшего блока 1 памяти и позиции отказавших разрядов в этом блоке 1. Блоки элементов И 23,24 и блок 25 коррекции выполняют коррекцию ошибок 2 табл. 6 ил.

...Y, YJ....T Уз ..Л,, У„..Л« Y,,.. Л. Y«...Yf « Yu .. Ли V Y r

14 1y 1( Ml

Y4f Y Y4 YJl YJ3 Y5( YJT YH Yt( Y«| Y4« Y1t Y7J YT YT1 YJ

1

0

1

0

1

0

1

0

0 0

Продолжение табл.1

1 и

с.к«

с,к,

с«к ctЈo

ошибка

О О То же

1 0 Двойная пакетная

ошибка

1 0 Двойная пакетная

ошибка

1 0 То же

1 1 Двойная пакетная

ошибка или ошибка в контрольных разрядах Y7,-YSO

0 1 Ошибка в контрольных разрядах Y6f

Y«

О 1 Ошибка в контрольных разрядах YtgY™

От Ш9 Отбл.20

§ I tc

Ј

I

§

Ǥ I

К $л.12 Фив $

-

22

Фие.1 От$л.18

Ј-ЭПф

OZ V9V

L.

12 Щ v

J

XI

г

53

J

CJ

3

S1

4

o

12 -LfQ LUQ

Л.Гратилло

27 OmffA.22

Фиг. 8

Составитель Т.Зайцева Техред А.Кравчук

- Заказ 1902/52

Тираж 558

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

9

fo

«0-1 М §

I

Is Н

s ъ

§5I

Ц

йа ч

ч

|Ј

I&

ай

t

§.

ч5

И

Корректор М. Васильева

Подписное

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-04-23—Публикация

1987-02-24—Подача