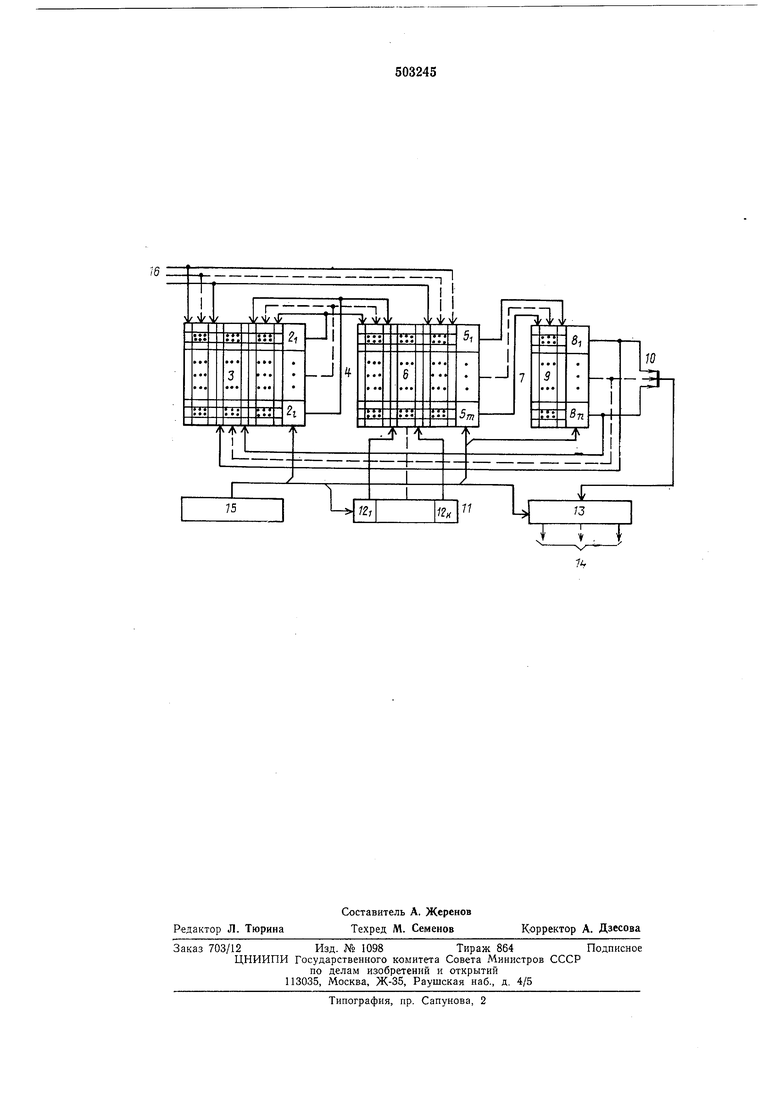

коммутатора 3; однородную арифметическую структуру 4, состоящую из процессоров 5т и коммутатора 6; однородную суммирующую структуру 7, состоящую из многовходовых сумматоров 8i-8п и коммутатора 9; элемент «ИЛИ 10; постоянное запоминающее устройство 11, состоящее из блоков памяти 12i-12fe, коммутатор 13 вывода данных; выход 14 системы, устройство 15 управления и информационный вход 16 системы.

Информация с объекта управления по каналам входной информации ( 16 системы) в цифровом коде поступает чесез коммутатор 3 в оперативные запоминающие устройства 2i-2i и через коммутатор 6 - в процессоры . Каждое оперативное запоминающее устройство, входящее в однородную оперативную запоминающую структуру 1, хранит цифровую информацию, необходимую для выработки числового значения алгоритма управления (регулирования). Постоянное запоминающее устройство 11 хранит константы, требуемые для вычисления алгоритмов управления (регулирования). Все математические операции, при помощи которых формируется алгоритм управления (регулирования), производятся в однородной арифметической структуре 4. Каждый процессор этой структуры настраивается на вычисление определенной составляющей алгоритма управления (регулирования). Окончательное числовое значение вырабатываемого алгоритма управления (регулирования) получается с помощью одного из сумматоров , входящих в однородную суммирующую структуру 7.

Процессоры и многовходовые сумматоры могут быть построены с учетом обработки информации последовательным, параллельным или комбинированным способом. Устройство 15 управления осуществляет управление процессом настройки однородных структур 1, 4 и 7 и устройства И и координирует работу всех узлов системы при -вычислениях алгоритмов управления (регулирования).

Принятая организация системы позволяет реализовывать различные по назначению и сложности алгоритмы управления и регулирования при сохранении структуры системы.

Формула изобретения

Цифровая система для обработки данных,

содержащая постоянное запоминающее устройство, коммутатор вывода данных, выход которого подключен к выходу системы, однородную арифметическую структуру, устройство управления, выход которого соединен с

управляющими входами однородной арифметической структуры, постоянного запоминающего устройства и коммутатора вывода данных, -информациоиный вход системы соединен с первым информационным входом однородной арифметической структуры, отличающаяся тем, что, с целью увеличения быстродействия, упрощения перестройки и повыщения коэффициента использования оборудования, в нее введены элемент «ИЛИ, однородная

оперативная запоминающая структура и однородная суммирующая структура, вход однородной суммирующей структуры соединен с выходом однор- дной арифметической структуры, управляющий вход - с выходом устройства управления, выход - подключен к первому информационному входу однородной оперативной запоминающей структуры и через элемент «ИЛИ - ко входу коммутатора вывода данных, вторые информационные входы

однородной оперативной запоминающей структуры и однородной арифметической структуры подключены к выходу однородной оперативной запоминающей структуры, третий информационный вход которой соединен с информационным входом системы, управляющий вход-с выходом устройства управления, третий информационный вход однородной арифметической структуры соединен с выходом постоянного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное цифровое вычислительное устройство | 1974 |

|

SU600561A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЙ | 1991 |

|

RU2006929C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1988 |

|

SU1840538A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1996 |

|

RU2125290C1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| МНОГОПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2012 |

|

RU2502126C1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

Авторы

Даты

1976-02-15—Публикация

1974-04-08—Подача