Предлагаемое изобретение относится к области вычислительной техники и может быть использовано для сверхбыстрой обработки больших массивов информации в цифровых комплексах высокой надежности.

Известна система по а.с. №1317447 (кл. G06F 15/16, опубл. 15.06.87). Эта система содержит М коммутаторов, М блоков управления коммутаторами, N устройств управления обменом, Q блоков контроля информационных шин, блок опроса, причем m информационных входов-выходов всех коммутаторов являются соответствующими информационными входами-выходами системы.

Недостатком этой системы является ее сложность.

Известна также система по а.с. №1315989 (кл. G06F 15/00, опубл. 07.06.87), содержащая формирователь адреса диспетчера, блок управления страницами, регистр страниц, регистр слов, сдвигатель, сумматор, три элемента И и четыре блока буферной памяти, причем формирователь адреса диспетчера содержит шесть сумматоров, три вычитателя, четыре коммутатора, дешифратор и два сдвигателя.

Недостатком этой системы является сложность процесса синхронизации отдельных устройств системы.

Из известных систем наиболее близкой по назначению и технической сущности к предлагаемой системе является процессорная система, описанная в книге Кагана Б.М. и Сташина В.В. Основы проектирования микропроцессорных устройств автоматики. М.: Энергоатомиздат, 1987, стр.11, которая принята за прототип.

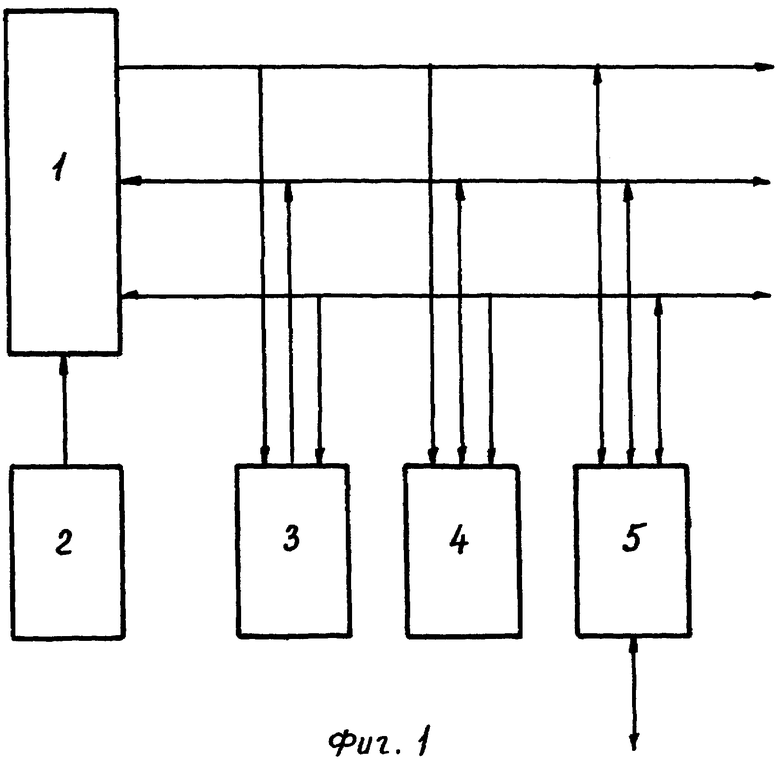

Процессорная система, принятая за прототип, содержит (фиг.1) процессор 1, синхронизатор 2, блок постоянной памяти 3, блок оперативной памяти 4, блок ввода-вывода информации 5. При этом выход синхронизатора 2 соединен с входом процессора 1. Выход адреса процессора 1 соединен с адресными входами блоков постоянной памяти 3, оперативной памяти 4 и ввода-вывода 5 с помощью шины адреса. Вход-выход данных процессора 1 соединен с выходом блока постоянной памяти 3, входами-выходами блоков оперативной памяти 4 и ввода-вывода 5 с помощью шины данных. Вход-выход управления процессора 1 соединен с входами управления блоков постоянной памяти 3, оперативной памяти 4 и входом-выходом управления блока ввода-вывода 5.

Работает данная процессорная система следующим образом. Под действием сигналов синхронизации, поступающих из синхронизатора 2, процессор 1 вырабатывает адрес выполняемой команды и адрес операндов. Код команды и операнды соответственно из блоков постоянной памяти 3 и оперативной памяти 4 поступают в процессор 1, который выполняет необходимые действия над операндами. Операнды в процессор 1 могут поступать из блока оперативной памяти 4 или от внешних устройств через блок ввода-вывода 5.

Недостатком данной процессорной системы является низкое быстродействие, обусловленное многотактным характером выполнения операций, так операция умножения выполняется за 58 тактов, что составляет 39 мкс.

Целью изобретения является повышение быстродействия системы.

Поставленная цель достигается тем, что известная процессорная система, содержащая, как и прототип, процессор, синхронизатор, блоки постоянной памяти, оперативной памяти и ввода-вывода, при этом вход-выход данных процессора соединен с помощью шины данных с входами-выходами данных блоков оперативной памяти и ввода-вывода, вход управления процессора соединен с помощью шины управления с выходами блоков постоянной памяти и ввода-вывода, выход адреса блока постоянной памяти с помощью шины адреса соединен с адресными входами блоков оперативной памяти и ввода-вывода, дополнительно снабжена счетчиком алгоритмов, первый вход которого соединен с выходом синхронизатора 2, второй вход соединен через шину управления с выходом блока ввода-вывода 5, выход соединен с входом блока постоянной памяти 3, а процессор выполнен в виде процессора с настраиваемой структурой и содержит n функционально-соединительных (FC) элементов (n - определяется сложностью решаемого алгоритма).

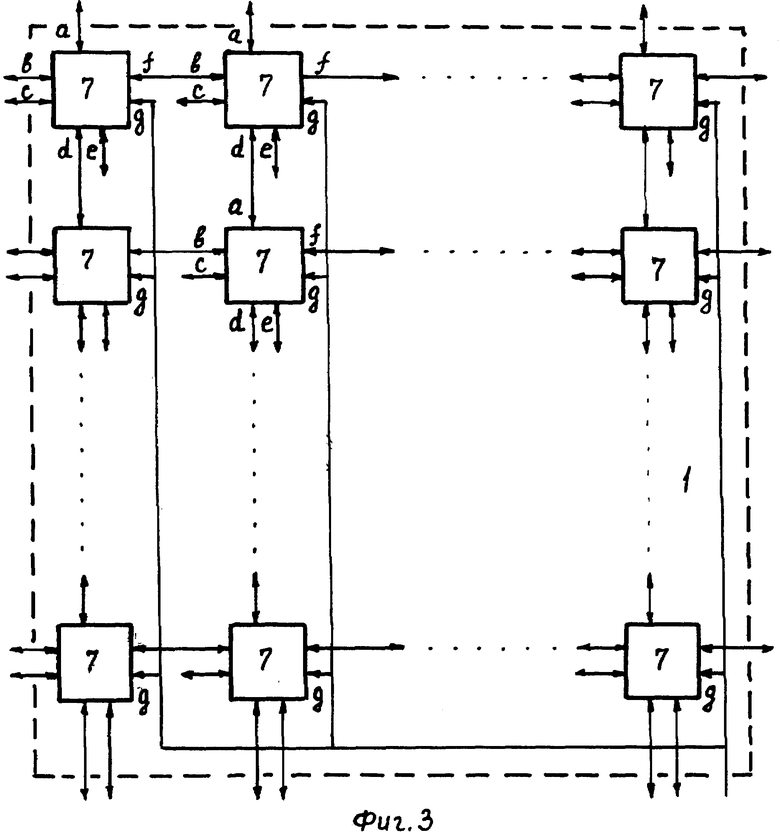

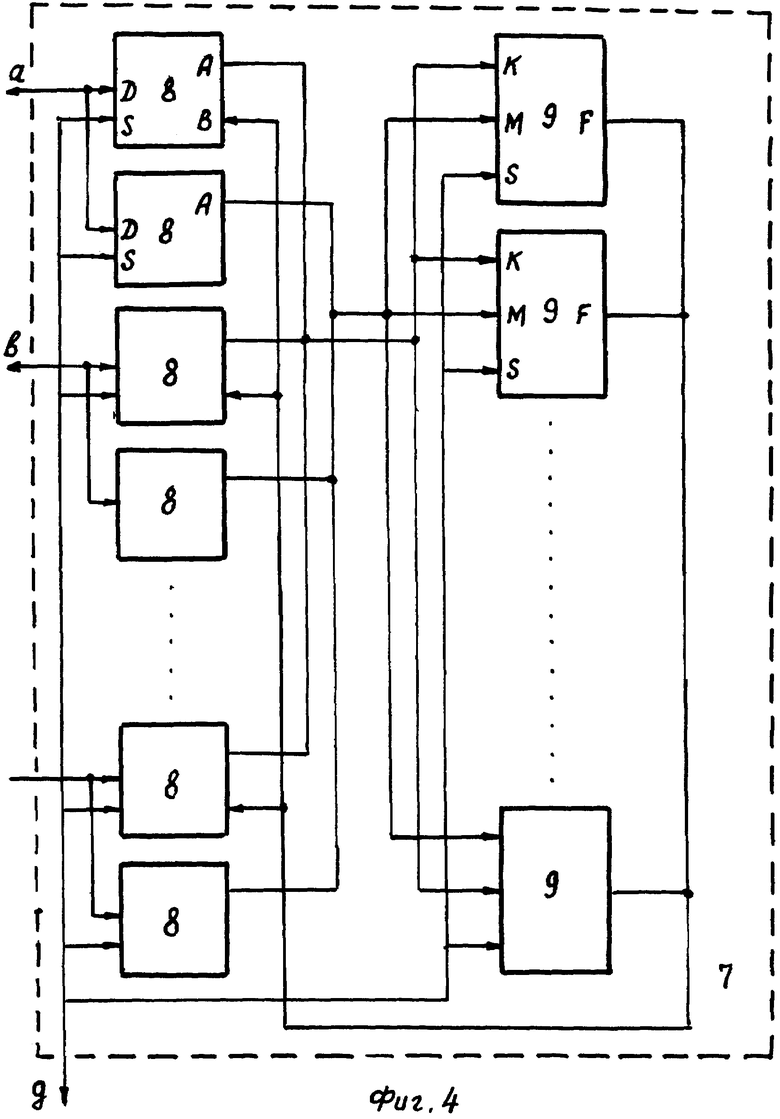

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема известной процессорной системы, на фиг.2 - предлагаемой, на фиг.3 - структурная схема процессора с настраиваемой структурой, на фиг.4 - структурная схема функционально-соединительного (FC) элемента.

В известных технических решениях признаков, сходных с отличительными признаками заявленного технического решения, не обнаружено, вследствие чего можно считать, что предлагаемое техническое решение обладает существенными отличиями.

Предлагаемая процессорная система (фиг.2), как и прототип, содержит процессор 1, синхронизатор 2, блок постоянной памяти 3, блок оперативной памяти 4 и блок ввода-вывода 5.

При этом вход-выход данных процессора 1 соединен с помощью шины данных с входами-выходами данных блоков оперативной памяти 4, ввода-вывода 5. Вход управления процессора 1 соединен с выходами управления блоков постоянной памяти 3 и ввода-вывода 5 с помощью шины управления. Адресный вход блока оперативной памяти 4 соединен с выходом блока постоянной памяти 3 и адресным входом-выходом блока ввода-вывода 5 с помощью шины адреса. В отличие от прототипа процессорная система дополнительно содержит счетчик алгоритмов 6 (фиг.2), первый вход которого соединен с выходом синхронизатора 2, второй вход соединен через шину управления с выходом блока ввода-вывода 5, а выход соединен с входом блока постоянной памяти 3.

Кроме того, процессор 1 выполнен в виде процессора с настраиваемой структурой (фиг.3), состоящего из n функционально-соединительных элементов 7.

При этом входы-выходы данных c, e функционально-соединительных элементов 7 (фиг.3) объединены в шину данных и через эту шину соединены с входами-выходами блоков оперативной памяти 4 и ввода-вывода 5 (фиг.2). Входы-выходы a, b, d, f соединены с соответствующими входами-выходами других функционально-соединительных элементов 7 (фиг.3). Входы g объединены в шину управления и соединены с выходами управления блоков постоянной памяти 3 и ввода-вывода 5 (фиг.2). Функционально-соединительный элемент 7 (фиг.4) состоит из шинных формирователей 8 (по два на каждый вход-выход данных) и m программируемых запоминающих устройств 9, каждое из которых реализует одну из m заданных функций. Такими функциями являются - умножение, деление, сложение, вычитание и так далее.

При этом входы-выходы a, b, c, d, e, f являются входами-выходами D шинных формирователей 8. Выходы A шинных формирователей 8 объединены по парно (фиг.4) в две шины, которые соединены соответственно с входами K, M программируемых запоминающих устройств 9. Входы управления S шинных формирователей 8 и программируемых запоминающих устройств 9 объединены в шину управления (фиг.4). Выходы F программируемых запоминающих устройств 9 объединены в шину, через которую они соединены с входами 6 шинных формирователей 8.

Синхронизатор 2 процессорной системы (фиг.2) реализован на микросхеме 133ЛАЗ, шинный формирователь 8 (фиг.4) - на микросхеме 589АП16, блок ввода-вывода 5 (фиг.2) может быть выложен на микросхемах 589ИР12. Параметры данных микросхем приведены в книге Березенко А.И., Корягина Л.Н. Микропроцессорные комплекты повышенного быстродействия. М.: Радио и связь. 1981 г., стр.11, 52, 55, 58.

Программируемое запоминающее устройство 9 может быть выполнено на микросхемах 556PT16. Сведения о данной микросхеме содержатся в журнале Микропроцессорные средства и системы. 1987 г. № 3, стр.90.

Счетчик алгоритмов 6 собран на микросхемах 133ИЕ7. Блоки постоянной памяти 3 и оперативной памяти 4 (фиг.2) могут быть выполнены соответственно на микросхемах 556РТ5 и 541РУ2. Параметры данных микросхем и структурные схемы блоков приведены в книге Высоцкого Б.Ф. Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах. М.: Радио и связь. 1984 г., стр.46, 54, 55.

Работает процессорная система следующим образом. Счетчик алгоритмов 6 (фиг.2) осуществляет под действием сигналов синхронизации, поступающих из синхронизатора 2 или сигналов с выхода блока ввода-вывода 5, переход к следующему вычисляемому алгоритму. Код с выхода счетчика алгоритмов 6 поступает на вход блока постоянной памяти 3, который формирует код настройки элементов процессора 1 и оперативной памяти 4. Код настройки через шину управления поступает на входы S шинных формирователей 8 и программируемых запоминающих устройств 9 (фиг.4), определяя по какому входу-выходу a, b, c, d, e, f операнд поступит на выбранный вход K или M программируемого запоминающего устройства 9, а также определяет какую функцию реализует данный функционально-соединительный элемент 7 (фиг.3). Код настройки управляет режимами работы блока оперативной памяти 4 (запись-чтение информации), а через шину адреса выбирает операнды, которые по шине данных поступают в процессор 1 (фиг.2).

После этапа настройки происходит однотактный вычислительный процесс, причем за один такт реализуется целый алгоритм, а не отдельная операция. Результаты вычисления алгоритма могут быть записаны в блок оперативной памяти 4 и выведены через блок ввода-вывода 5 на внешние устройства. Управление сменой алгоритмов может осуществлять внешнее устройство. В этом случае внешнее устройство через блок ввода-вывода 5 и шину управления записывает в счетчик алгоритмов 6 необходимый код алгоритма.

Положительный технический эффект от использования предлагаемой процессорной системы, по сравнению с прототипом, заключается в увеличении быстродействия выполнения сложных алгоритмов за счет применения функционально-соединительных (FC) элементов и однотактным характером выполнения вычислений.

Для примера рассмотрим алгоритм вычисления базовой операции быстрого преобразования Фурье, приведенный в книге Высоцкого Б.Ф. Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах. М.: Радио и связь. 1984, стр.65. Данный алгоритм содержит четыре операции умножения и шесть операций сложения. В этом устройстве время выполнения алгоритма 164 мкс (стр.131). Для реализации данного алгоритма в предлагаемой процессорной системе процессор с настраиваемой структурой содержит десять функционально-соединительных (FC) элементов, при этом они соединены так, что сначала выполняются одновременно четыре операции умножения, затем две операции сложения и далее еще четыре операции сложения, т.е. получается трехступенчатая структура.

Задержка прохождения информации через шинный формирователь 7 составляет:

tзшф=tз1+tз2=40 нс,

где tз1, tз2 - задержка в прямом и обратном направлении.

Задержка программируемого запоминающего устройства равна tзПЗУ=85 нс. Суммарная задержка функционально-соединительного (FC) элемента определяется:

tзFC=tзшф+tзПЗУ=125 нс.

Время записи-чтения блока оперативной памяти 4 составляет 200 нс, тогда время выполнения алгоритма составляет

tA=tзп/чт+3tзFC≈600 нс.

Таким образом, предлагаемая процессорная система по сравнению с прототипом позволяет увеличить быстродействие вычисления рассмотренного алгоритма в 270 раз.

Предлагаемая процессорная система обладает высокой надежностью, которая достигается тем, что в случае неисправности одного из функционально-соединительного (FC) элемента процессора система сможет с ограничениями выполнять вычисления, исключив неисправный элемент из структуры путем перенастройки структуры процессора. Для прототипа выход из строя элемента процессора приводит к отказу всей системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Устройство для исследования электрических цепей | 1985 |

|

SU1332340A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

| ОБЩЕСТВЕННЫЙ КОМПЬЮТЕР | 2014 |

|

RU2571575C1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

Изобретение относится к области вычислительной техники и может быть использовано для сверхбыстрой обработки больших массивов информации в цифровых комплексах высокой надежности. Техническим результатом является повышение быстродействия. Устройство содержит блок постоянной памяти (БПП), синхронизатор, счетчик алгоритмов (СА), блок анализа данных (БАД), блок оперативной памяти (БОП) и блок ввода-вывода. БАД соединен двухсторонними информационными связями с БОП и блоком ввода-вывода, первый выход которого подключен к управляющему входу БАД. Счетный вход СА соединен с выходом синхронизатора, установочный вход - с первым выходом блока ввода-вывода, а выход подключен к адресному блоку БПП. Первый выход БПП соединен с управляющим входом блока анализа данных и входом записи чтения БОП. Второй выход БПП подключен к адресным входам БОП и блока ввода-вывода, второй выход которого соединен с адресным входом БОП. 2 з.п. ф-лы, 4 ил.

| Авт | |||

| свид | |||

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Б.М.Каган и В.В.Сташин "Основы проектирования микропроцессорных устройств автоматики, стр.11, М.: Энергоатомиздат, 1987. | |||

Авторы

Даты

2007-05-27—Публикация

1988-03-04—Подача