Изобретение относится к цифровой технике и может быть использовано в различных устройствах дискретной автоматики, вычислительной техники и системах программного управления объектами.

Известно пересчетное устройство коррекцией результата счета, состоящее из трех счетчиков импульсных сигналов, входы управления цепями обнуления и параллельной записи которых подключены к соответствующим шинам, а выходы - к входам соответствующих схем поразрядного голосования.

Однако, для обеспечения выдачи правильных результатов необходимо, чтобы два счетчика из трех работали правильно, без сбоев; только один из трех счетчиков может периодически корректироваться. В известном устройстве велик объем вспомогательного оборудования, предназначенного для исправления ошибок и выдачи достоверной информации, что приводит к понижению надежности работы и увеличению стоимости устройства.

С целью повышения надежности контроля счетчиков и упрощения устройства в него введены элементы И и статический регистр, первые входы которых подключены к прямым и инверсным выходам соответствующих схем поразрядного голосования, вторые входы подключены к шине запрещающего строба, а выходы подключены ко входам установки в «О и «1 соответствующих триггеров статического регистра, а единичные выходы триггеров подключены ко входам параллельной записи одноименных разрядов всех счетчиков и к выходным щинам устройства.

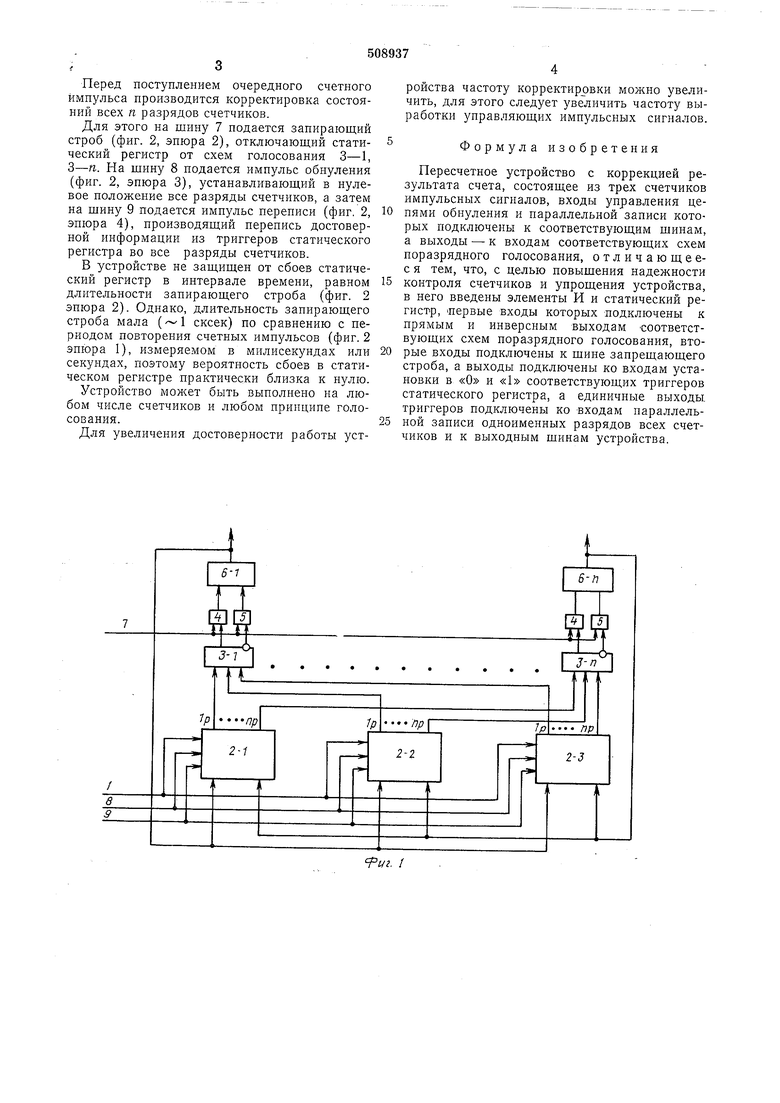

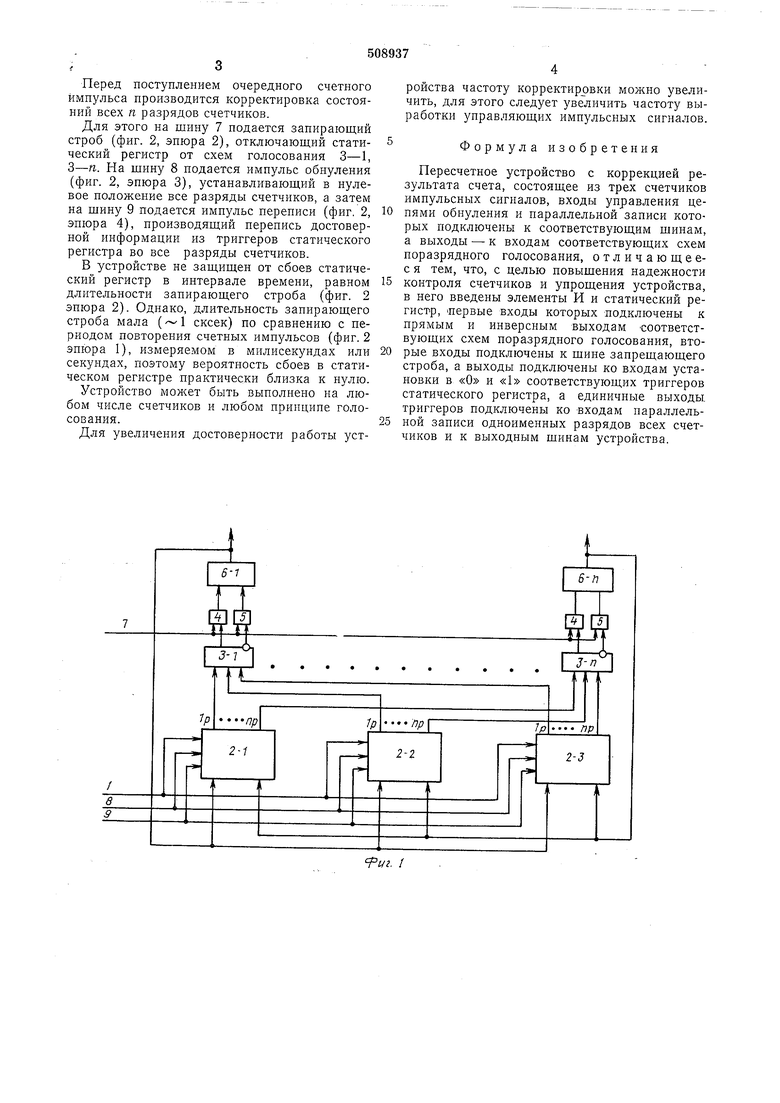

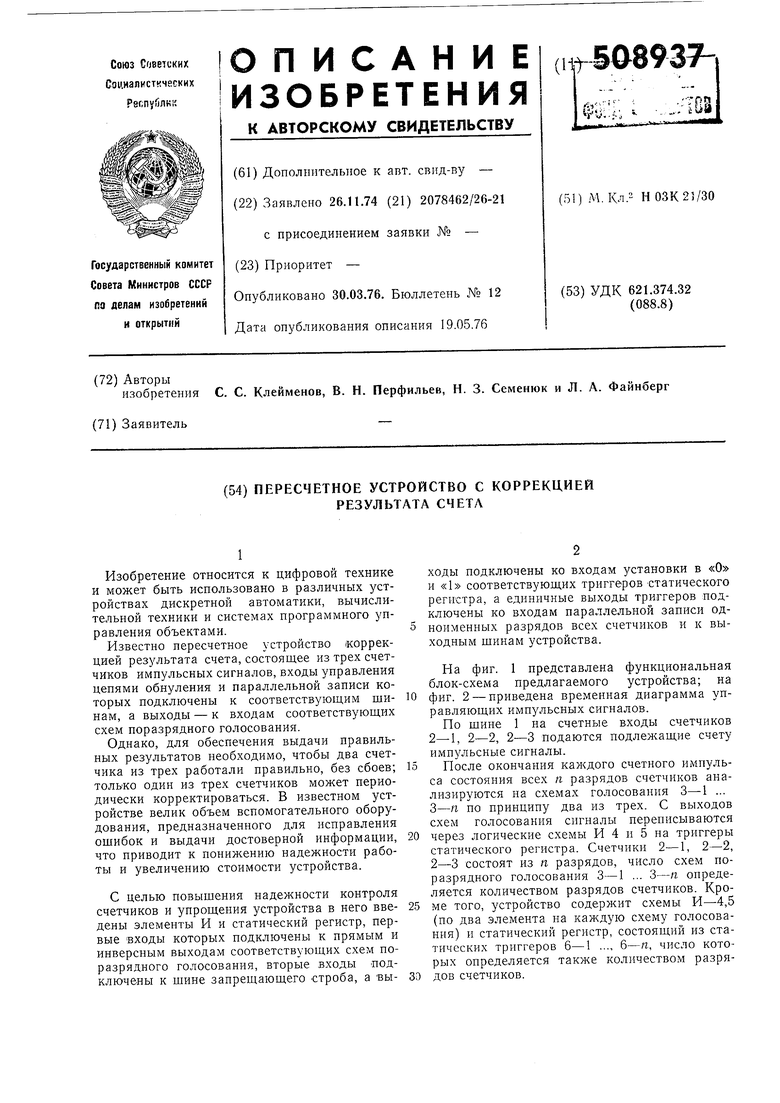

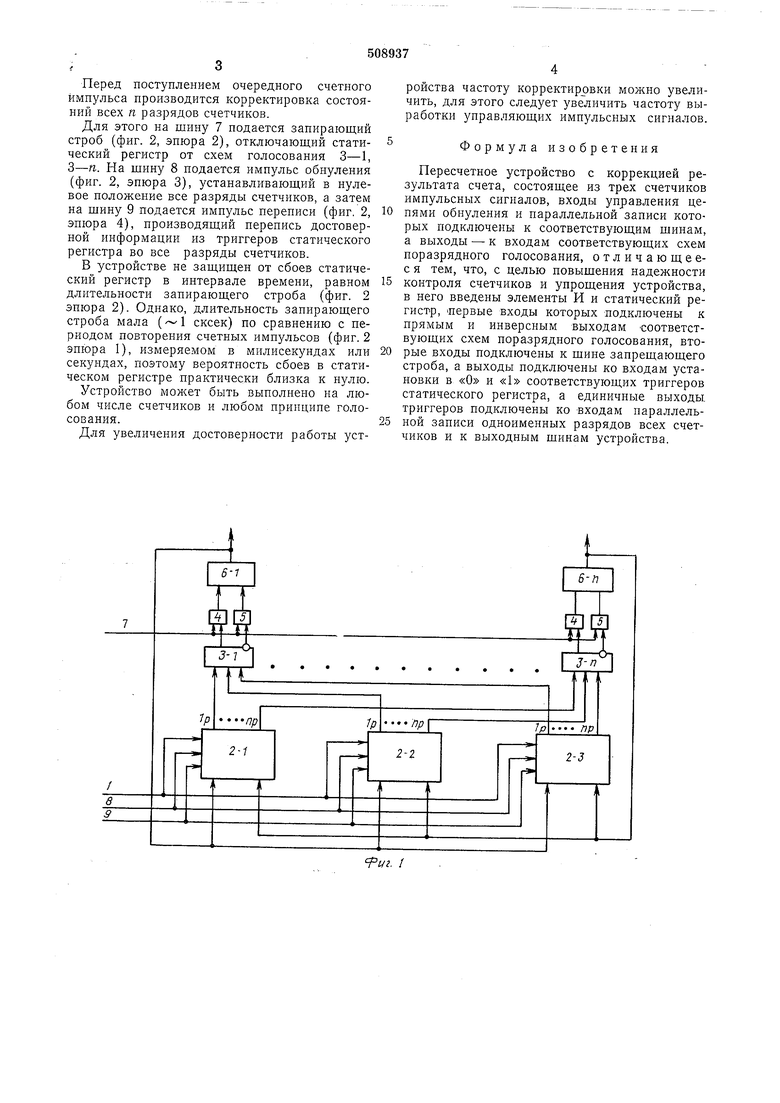

На фиг. 1 представлена функциональная блок-схема предлагаемого устройства; на фиг. 2 - приведена временная диаграмма управляющих импульсных сигналов.

По шине 1 на счетные входы счетчиков 2-1, 2-2, 2-3 подаются подлел :ащие счету импульсные сигналы.

После окончания каждого счетного импульса состояния всех п разрядов счетчиков анализируются на схемах голосования 3-1 ... 3-п по принципу два из трех. С выходов схем голосования сигналы переписываются через логические схемы И 4 и 5 на триггеры статического регистра. Счетчики 2-1, 2-2, 2-3 состоят из п разрядов, число схем поразрядного голосования 3-1 ... 3-п определяется количеством разрядов счетчиков. Кроме того, устройство содержит схемы И-4,5 (по два элемента на каждую схему голосования) и статический регистр, состоящий из статических триггеров 6-1 ..., 6-п, число которых определяется также количеством разрядов счетчиков.

Перед поступлением очередного счетного импульса производится корректировка состояний всех я разрядов счетчиков.

Для этого на шину 7 подается запирающий строб (фиг. 2, эпюра 2), отключающий статический регистр от схем голосования 3-1, 3-п. На щину 8 подается импульс обнуления (фиг. 2, эпюра 3), устанавливающий в нулевое положение все разряды счетчиков, а затем на щину 9 подается импульс переписи (фиг. 2, эпюра 4), производящий перепись достоверной информации из триггеров статического регистра во все разряды счетчиков.

В устройстве не защищен от сбоев статический регистр в интервале времени, равном длительности запирающего строба (фиг. 2 эпюра 2). Однако, длительность занирающего строба мала ( сксек) по сравнению с периодом повторения счетных импульсов (фиг. 2 эпюра 1), измеряемом в милисекундах или секундах, поэтому вероятность сбоев в статическом регистре практически близка к нулю.

Устройство может быть выполнено на любом числе счетчиков и любом принципе голосования.

Для увеличения достоверности работы устройства частоту корректировки можно увеличить, для этого следует увеличить частоту выработки управляющих импульсных сигналов.

Формула изобретения

Пересчетное устройство с коррекцией результата счета, состоящее из трех счетчиков импульсных сигналов, входы управления цепями обнуления и параллельной записи которых подключены к соответствующим щинам, а выходы - к входам соответствующих схем поразрядного голосования, отличающеес я тем, что, с целью повышения надежности

контроля счетчиков и упрощения устройства, в него введены элементы И и статический регистр, Первые входы которых подключены к прямым и инверсным выходам соответствующих схем поразрядного голосования, вторые входы подключены к щине запрещающего строба, а выходы подключены ко входам установки в «О и «1 соответствующих триггеров статического регистра, а единичные выходы, триггеров подключены ко входам нараллельной записи одноименных разрядов всех счетчиков и к выходным щинам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный счетчик импульсов | 1977 |

|

SU641656A1 |

| Устройство для формирования временных интервалов | 1982 |

|

SU1070532A1 |

| Устройство для записи цифровой информации | 1984 |

|

SU1157569A1 |

| Устройство селекции импульсов по длительности | 1990 |

|

SU1758863A1 |

| Устройство для измерения частоты и ритмичности сердечных сокращений | 1984 |

|

SU1219048A1 |

| Цифро-частотный интегратор | 1983 |

|

SU1089580A1 |

| Цифровой частотно-фазовый дискриминатор | 1982 |

|

SU1027798A1 |

| Устройство для воспроизведения цифровой информации многодорожечной магнитной записи | 1989 |

|

SU1686475A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

л

П

Авторы

Даты

1976-03-30—Публикация

1974-11-26—Подача