Э vl

WJ2

D

;;л

х ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

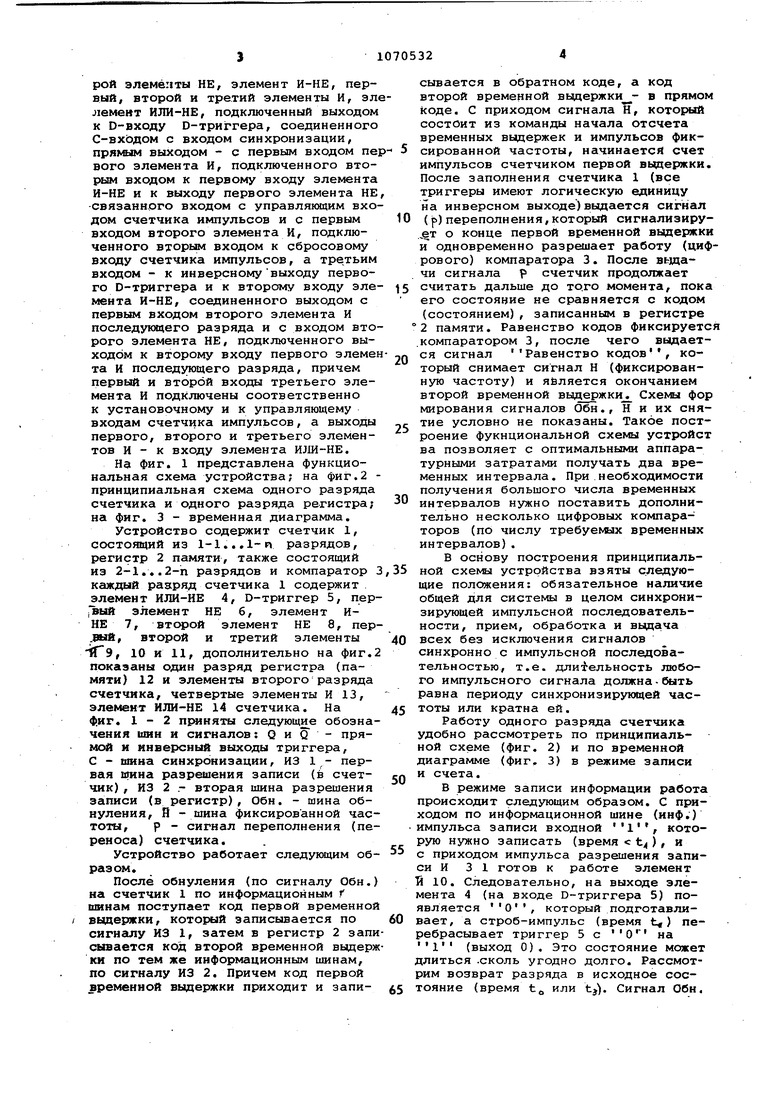

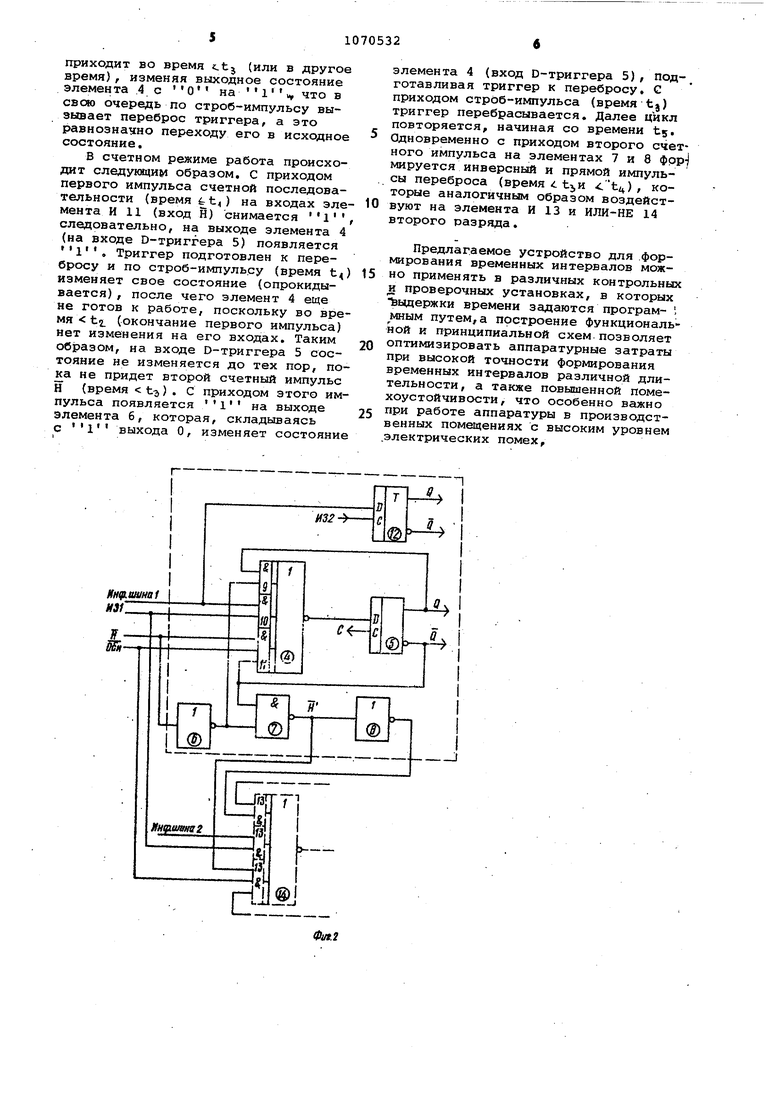

1. УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ, содержащее счетчик импульсов, подключенный сбросовьвя входом к шине обнуления, информаци(Я1Мые шины, шину фиксированней частоты, отличающеес я тем, что, с целью повышения помехоустойчивости устройства, в него введены регистр памяти, шина синхронизации, первая и вторая шины разрешения записи, шина переполнения, компаратор, подключенный первыми входами к выходам каждого разряда счетчика импульсов, сбросовым входом - к шине переполнения, а вторыми входами - к соответствующим выходам регистра памяти, связанного установочными входами с соответствующими информационными шинами, подключенными к информационным входам соответствующих разрядов счетчика Импульсов, соединенных входом синхронизации, счетным входом, управляющим входом соответственно с .шиной синхронизации, с шиной фиксированной частоты и с первой шиной разрешения записи, при-чем управляющий вход регистра памя- ц ти подключен к второй шине разреше(О ния записи, а выход последнего разряда - к шине переполнения.

РаВенстВв .t /

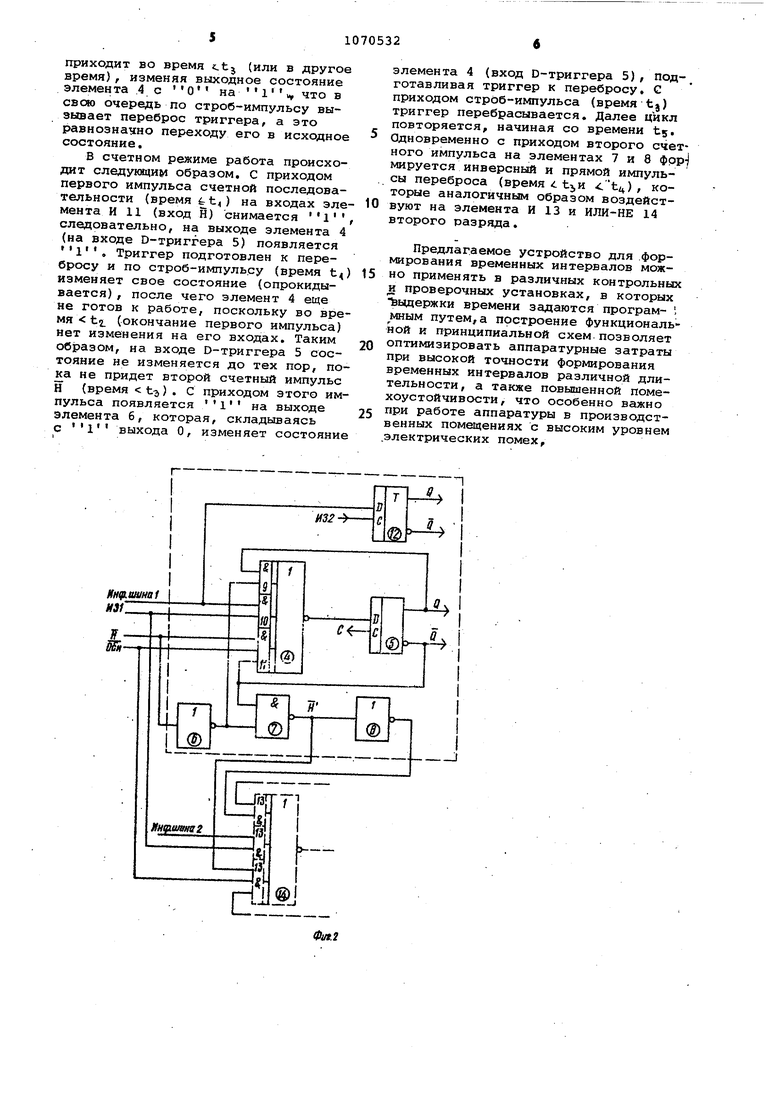

ченного вторым входом к сбросовому входу счетчика импульсов, а третьим входом - к инверсному выходу первого Ь-триггера и к второму вхсду элемента И-НЕ, соединенного выходом с первым входом второго элемента И последующего разряда и с входом второго элемента НЕ, подключенного выходом к второму входу первого элемента И последующего разряда, причем первый и второй входы третьего элемента И подключены соответственно к установочному и управляющему входам счетчика импульсов, а выходы первого, второго и третьего элементов и - к входу элемента ИЛИ-НЕ. а выходы дополнительных элементов И подключены к S-входам дoпoлнитeльныx RS-триггеров 2. Недостаток устройства заключается в отсутствии общей сквозной синхронизации, что, приводит к труднообнаруживаемым и еще более трудноустраняемым сбоям, особенно по З-входам триггеров, Цель изобретения - повышение помехоустойчивости устройства. Поставленная цель достигается тем, что в устройство для формирования временных интервалов, содержащее счетчик импульсов, подключенный сбросовым входом к шине обнуления, информационные шины, шину фиксированной частоты, введены регистр памяти, шина синхронизации, первая и вторая шины разрешения записи, шина переполнения, компаратор, подключенный первыми входами к выходам каждого разряда счетчика импульсов, сбросовым входом - к шине переполнения, а вторыми входами - к соответствующим выходам регистра памяти, связанного установочными входами с соответствующими информационными шинами/ подключенншчи к информационным входам соответствуквдих разрядов, счетчика импульсов, соединенных входом синхронизации, счетным входом, управляющим входом соответственно с ишной синхронизации, с шиной фиксированной частоты и с первой шиной разрешения записи, причем управляющий вход регистра памяти подключен к второй шине разрешения записи, а выход последнего разряда - k шине переполнения. Каждый разряд счетчика импульсов содержит D -триггер, первый и второй элементы НЕ, элемент И-НЕ, первый, второй и третий элементы И, эл лемент ИЛИ-НЕ, подключенный выходом к D-входу D-триггера, соединенного С-вхЬдом с входом синхронизации, прякблм выходом - с первым входом пе вого элемента И, подключенного вторым входом к первому входу элемента И-НЕ и к выходу первого элемента НЕ свяэанного входом с управляющим вхо дом счетчика импульсов и с первым входом второго элемента И, подключенного вторым входом к сбросовому входу счетчика импульсов, а тре,тьим входом - к инверсномувыходу первого D-триггера и к второму входу эле мента И-НЕ, соединенного выходом с первым входом второго элемента И последукяцего разряда и с входом вто рого элемента НЕ, подключенного выходом к второму входу первого элеме та И последующего разряда, причем первый и второй входы третьего элемента И подключены соответственно к установочному и к управляющему входам счетчика импульсов, а выходы первого, второго и третьего элементов И - к входу элемента ИЛИ-НЕ. На фиг. 1 представлена функциональная схема устройства; на фиг.2 принципиальная схема одного разряда счетчика и одного разряда регистра; на фиг. 3 - временная диаграмма. Устройство содержит счетчик 1, состоящий из 1-1...1-п разрядов, регистр 2 памяти, также состоящий из 2-1...2-п разрядов и компаратор каждый разряд счетчика 1 содержит элемент ИЛИ-НЕ 4, D-триггер 5, пер |вый элемент НЕ б, элемент ИНЕ 7, втсфой элемент НЕ 8, пер .вый, второй и третий элементы М 9, 10 и 11, дополнительно на фиг. показаны один разряд регистра (памяти) 12 и элементы второго разряда счетчика, четвертые элементы И 13, элемеит ИЛИ-НЕ 14 счетчика. На фиг. 1-2 п{жняты следующие обозна чения шин и сигналов: Q и О - прямой и инверсный выходы триггера, С - шина синхронизации, ИЗ первая ишна разрешения записи (ё счетчик) , ИЗ 2 .- вторая шина разрешения записи (в регистр), Обн. - шина обиуления, Я - шина фиксированной частоты, р - сигнал переполнения (переноса) счетчика. Устройство работает следующим образом. После обнуления (по сигналу Обн.) на счетчик 1 по информационным f шинам поступает код первой временной / вЕЗдержки, который записывается по сигналу ИЗ 1, затем в регистр 2 запи сывается код второй временной вьщерж ки по тем же информационным шинам, по сигналу ИЗ 2. Причем код первой временной выдержки приходит и записывается в обратном коде, а код второй временной вьвдержки - в прямом коде. С приходом сигнала If, который состоит из команды начала отсчета временных вьвдержек и импульсов фиксированной частоты, начинается счет импульсов счетчиком первой вьщержки. После заполнения счетчика 1 (все триггеры имеют логическую единицу на инверсном выходе)выдается сигнал (р)переполнения,который сигнализируjeT о конце первой временной вьщержки и одновременно разрешает работу (цифрового) компаратора 3. После вьщачи сигнала Р счетчик продолжает считать дальше до того момента, пока его состояние не сравняется с кодом (состоянием), записанным в регистре 2 памяти. Равенство кодов фиксируется .компаратором 3, после чего выдается сигнал Равенство кодов, который снимает сигнал Н (фиксированную частоту) и является окончанием второй временной выдержки Схеьш фор мирования сигналов Обн., Н и их снятие условно не показаны. Такое построение фукнциональной схемы устройст ва позволяет с оптимальными аппаратурными затратами получать два временных интервала. При.необходимости получения большого числа временных интервалов нужно поставить дополнительно несколько цифровых компараторов (по числу требуелих временных интервалов). В основу построения принципиальной cxeNfij устройства взяты следующие положения: обязательное наличие общей для систег и в целом синхронизирующей импульсной последовательности, прием, обработка и вьщача всех без исключения сигналов синхронно с импульсной последовательностью, т.е. длительность любого импульсного сигнала должна-быть равна периоду синхронизирукицей частоты или кратна ей. Работу одного разряда счетчика удобно рассмотреть по принципиальной схеме (фиг. 2) и по временной диаграмме (фиг, 3) в режиме записи и счета. В режиме записи информации работа происходит следующим образом. С приходом по информационной шине (инф.) мпульса записи входной , которую нужно записать (время t), и с приходом импульса разрешения записи И 31 готов к работе элемент 10. Следовательно, на выходе элеента 4 (на входе D-триггера 5) появляется О , который подготавлиает, а строб-импульс (время t) пеебрасывает триггер 5с на (выход 0). Это состояние может литься .сколь угодно долго. Рассмотим возврат разряда в исходное сосояние (время to или tj). Сигнал Обн.

приходит во время ctj (или в другое время), изменяя выходное состояние элемента 4с О на 1 и, что в свсяо очередь по строб-импульсу вызывает переброс триггера, а это равнозначно переходу его в исходное состояние.

В счетном режиме работа происходит следующим образом, С приходом первого импульса счетной последовательности (время tt4) на входах элемента И И (вход Н) снимается , следовательно, на выходе элемента 4 (на входе D-триггера 5) появляется . Триггер подготовлен к перебросу и по строб-импульсу (время t) изменяет свое состояние (опрокидывается) , после чего элемент 4 еще не готов к работе, поскольку во время tj. (окончание первого импульса) нет изменения на его входах. Таким образом, на входе D-триггера 5 состояние не изменяется до тех пор, пока не придет второй счетный импульс Н (время t,) . С приходом этого имна выходе

пульса появляется

элемента б, которая, складываясь

с выхода О, изменяет состояние

HI @

I .л-г элемента 4 (вход D-триггера 5), под-, готавливая триггер к перебросу. С приходом строб-импульса (время tj) триггер перебрасывается. Далее цикл повторяется, начиная со времени ts.

Одновременно с приходом второго счетного импульса на элементах 7 и 8 фрр-j мируется инверсный и прямой импульсы переброса (время i tJ,и t) , которые аналогичным образом воздействуют на элемента И 13 и ИЛИ-НЕ 14 второго разряда.

Предлагаемое устройство для формирования временных интервалов можно применять в различных контрольных и проверочных установках, в которых Ьыдержки времени задаются програм- , мным путем,а построение функциональной и принципиальной схем позволяет

оптимизировать аппаратурные затраты при высокой точности формирования временных интервалов различной длительности, а также повышенной помехоустойчивости, что особенно важно

при работе аппаратуры в производственных помещениях с высоким уровнем .электрических помех.

t2h

tl

ts

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННЫХИНТЕРВАЛОВ | 1972 |

|

SU434401A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования временныхиНТЕРВАлОВ | 1979 |

|

SU798773A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-30—Публикация

1982-08-20—Подача