1

Изобретение относится к технике обработки информапии и может быть использовано в системах с импульсно-кодовой модуляцией, а также в системах передачи дискретных сообщений.

Известно устройство для синхронизации по циклам, содержащее два регистра сдвига, выходы разрядов каждого из которых подключены через последовательно соединенные дешифратор и решающий блок к формирователю импульсов, причем вход устройства соединен со вторым входом решающего блока, а выход формирователя импульсов подключен к установочным входам разрядов обоих регистров сдвига. Недостатком такого устройства является большое время вхождения в синхронизм.

Для сокращения времени вхождения в синхронизм при произвольном распределении синхрогруппы любого вида по позициям цикла в предлагаемом устройстве между выходами регистров сдвига с одной стороны и их входами с другой стороны включен преобразователь кода, который дополнительно соединен с выходом решающего блока, а также со входом устройства непосредственно и через последовательно соединенные блок выделения команд и блок коммутации, выход которого одновременно подключен к дополнительному входу дешифратора.

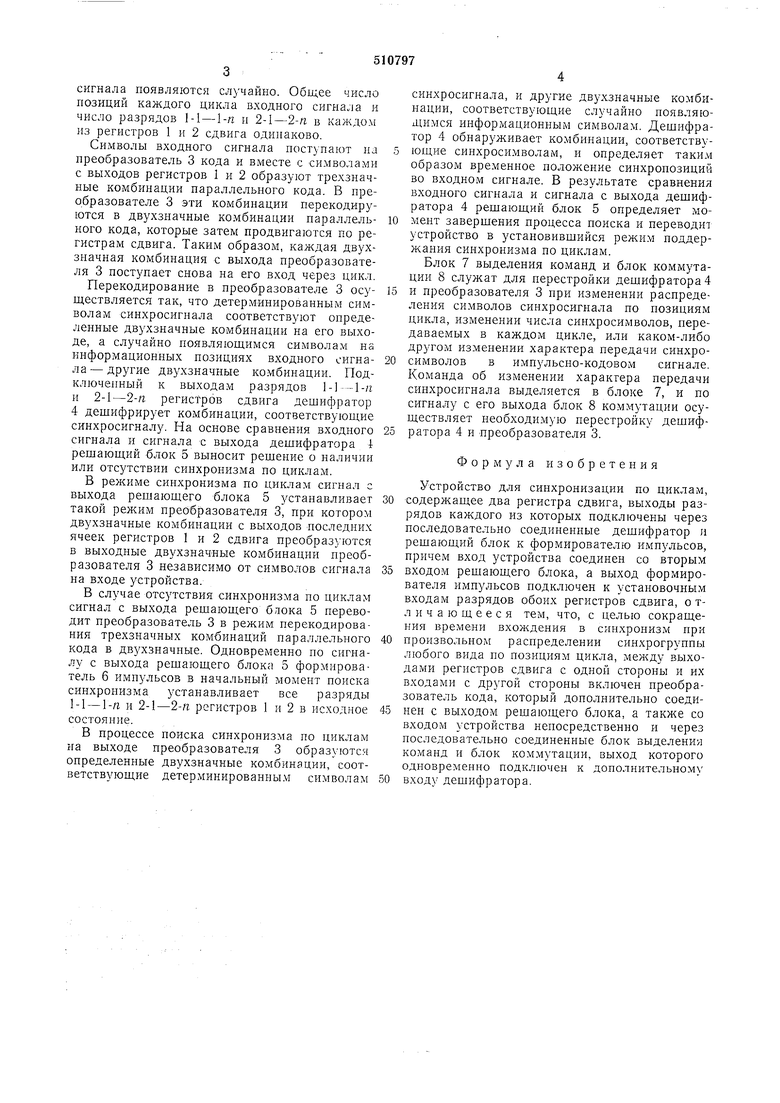

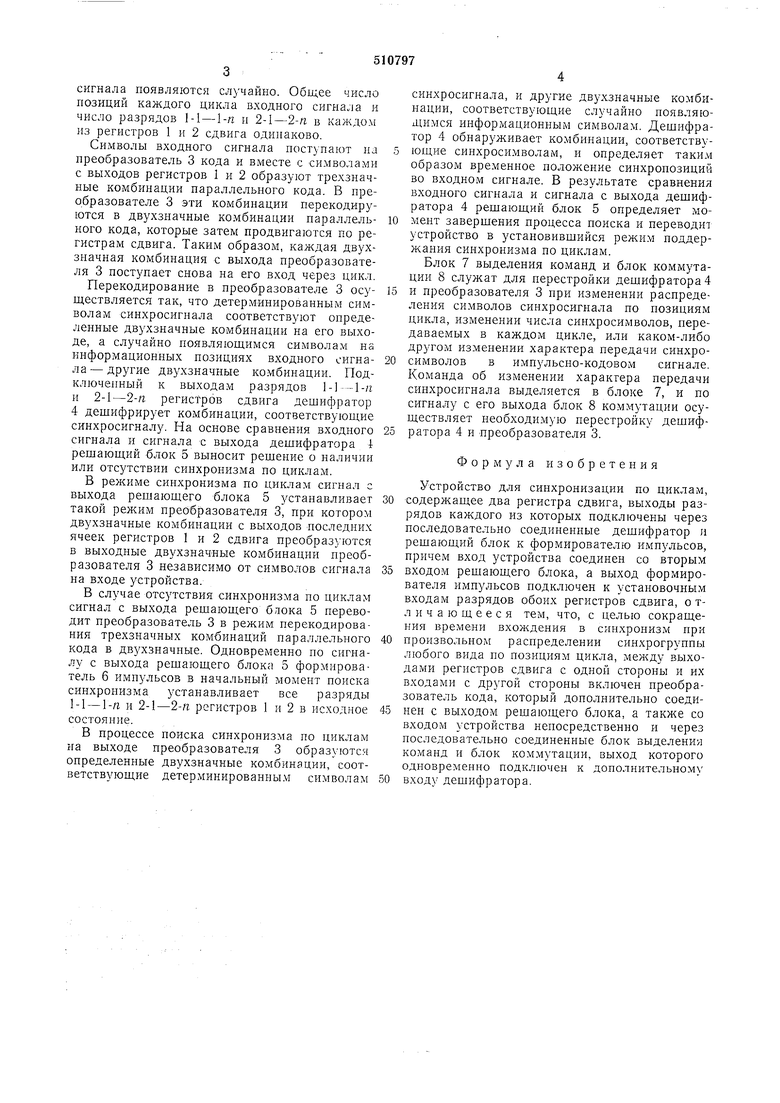

На чертеже дана структурная электрическая схема описываемого устройства.

Устройство содержит подключенные к его входу регистры 1 и 2 сдвига, между выходами которых с одной стороны и входами с другой стороны включен преобразователь 3 кода. Выходы разрядов 1-1 - 1-/г и 2-1-2-п, где я - число разрядов, каждого из регистров сдвига подключены через последовательно

соединенные дешифратор 4 и решающий блок 5 к формирователю 6 импульсов. Вход устройства соединен -со вторым входом решающего блока 5, а выход формирователя 6 импульсов подключен к установочным входам разрядов 1-1 -1-11 и 2-1-2-11 обоих регистров сдвига. Преобразователь 3 кода дополнительно соединен с выходом решающего блока 5, а также со входом устройства непосредственно и через последовательно соединенные

блок 7 выделения команд и блок 8 коммутации, выход которого одновременно подключен к дополнительному входу дешифратора 4. Выход дешифратора 4 соединен с выходом устройства.

Устройство работает следующим образом. На вход устройства поступает сигнал, в котором с частотой следования циклов на синхропозициях повторяются детерминированные символы синхросигнала. На остальных (информационных) позициях циклов символы

сигнала появляются случайно. Общее число позиций каждого цикла входного сигнала и число разрядов 1-1 - 1-п и 2-1-2-л в каждом из регистров 1 и 2 сдвига одинаково.

Символы входного сигнала поступают па преобразователь 3 кода и вместе с си.мволами с выходов регистров 1 и 2 образуют трехзначные комбинации параллельного кода. В преобразователе 3 эти комбинации перекодируются в двухзначные комбинации параллелького кода, которые затем продвигаются по регистрам сдвига. Таким образом, каждая двухзначная комбинация с выхода преобразователя 3 поступает снова на его вход через цикл.

Перекодирование в преобразователе 3 осуществляется так, что детерминированным символам синхросигнала соответствуют определенные двухзначные комбинации на его выходе, а случайно появляющимся символам на информационных позициях входного сигнала - другие двухзначные комбинации. Подключенный к выходам разрядов 1- --1-/г и 2-1-2-я регистров сдвига дещифратор 4 дешифрирует ко.мбкнации, соответствующие синхросигналу. Па основе сравнения входного сигнала и сигнала с выхода дешифратора 4решающий блок 5 выносит рещение о наличии или отсутствии синхронизма по циклам.

В режиме синхронизма по циклам сигнал с выхода решающего блока 5 устанавливает такой режим преобразователя 3, при котором двухзначные комбинации с выходов последних ячеек регистров 1 и 2 сдвига преобразуются в выходпые двухзначные комбинации преобразователя 3 независимо от символов сигнала на входе устройства.

В случае отсутствия синхропизма но циклам сигнал с выхода решающего блока 5 переводит преобразователь 3 в режим перекодирования трехзначных комбинаций параллельного кода в двухзначные. Одновременно по сигналу с выхода решающего блока 5 формирователь 6 импульсов в начальный момент ноиска синхронизма устанавливает все разряды 1-1 - -п и 2-1-2-п регистров 1 и 2 в исходное состояние.

В процессе поиска синхронизма но циклам на выходе преобразователя 3 образуются определенные двухзначные комбинации, соответствующие детерминированны.1 символам

синхросигнала, и другие двухзначные комбинации, соответствующие случайно появляющимся информационным символам. Дешифратор 4 обнаруживает комбинации, соответствующие синхросимволам, и определяет таким образом временное положение синхропозиций во входном сигнале. В результате сравнения входного сигнала и сигнала с выхода дешифратора 4 решающий блок 5 определяет момент завершения процесса поиска и переводит устройство в установившийся режим поддержания синхронизма по циклам.

Блок 7 выделения команд и блок коммутации 8 служат для перестройки дешифратора 4 и преобразователя 3 при изменении раснределения символов синхросигнала по позициям цикла, изменении числа синхросимволов, передаваемых в каждом цикле, или каком-либо другом изменении характера передачи синхросимволов в импульспо-кодовом сигнале. Команда об изменении характера передачи синхросигнала выделяется в блоке 7, и по сигналу с его выхода блок 8 коммутации осуществляет необходи.мую перестройку дешифратора 4 и преобразователя 3.

Формула изобретения

Устройство для синхронизации по циклам, содержащее два регистра сдвига, выходы разрядов каждого из которых подключены через последовательно соединенные дешифратор и решающий блок к формирователю импульсов, причем вход устройства соединен со вторым входом рещающего блока, а выход формирователя импульсов подключен к установочным входам разрядов обоих регистров сдвига, о тл и чающееся тем, что, с целью сокращения времени вхол-сдения в синхронизм при произвольпом распределении синхрогруппы любого вида по позициям цикла, между выходами регистров сдвига с одной стороны и их входами с другой стороны включен нреобразователь кода, который дополнительно соединен с выходом решающего блока, а также со входом устройства непосредственно и через иоследовательно соединенные блок выделения команд и блок коммутации, выход которого одновременно подключен к дополнительному входу дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

Авторы

Даты

1976-04-15—Публикация

1971-11-29—Подача