1

Изобретение относится к радиотехнике и

может использоваться в источниках питания, в приемниках информации для обеспечения синхронизма.

Известно устройство синхронизации по циклам.содержащее последовательно соединенные делитель, элемент ИЛИ и регистр сдвига, вход и выходы которого соединены с соответствующими входами блока опробования и памяти, выходы которого через блок управления соединены с управляющим входом делителя и вторым входом элемента ИЛИ 1.

Однако в этом устройстве при неравновероятных позициях начала поиска синхронизма требуется больщое время на его восстановление.

Цель изобретения - уменьщение времени вхождения в синхронизм.

Для этого в устройство синхронизации по циклам, содержащее последовательно соединенные делитель, элемент ИЛИ и регистр сдвига, вход и выходы которого соединены с соответствующими входами блока опробования и памяти, выходы которого через блок угфавления соединены с управляющим входом делителя и вторым входом элемента ИЛИ, введены коммутируемый счетчик, два

элемента И, триггер, счетчик .ощибок и узел

формирования сигналов «Сброс, при это.м дополнительный вход делителя через последовательно соединенные первый элемент И, счетчик ощибок и узел формирования сигналов «Сброс подключен к входам «Сброс

блока опробования и памяти, триггера,счетчика ошибок и коммутируемого счетчика, к двум другим входам которого подключены управляющие выходы блока управления, а выход подключен ко входу триггера и ко второму входу узла формирования сигналов «Сброс, причем ко входам второго элемента И подключены соответственно выход одного из разрядов регистра сдвига и дополнительный вход делителя, управляющий вход которого подключен к третьему входу узла формирования сигналов «Сброс, а выход - к первому дополнительному входу блока управления, к второму дополнительному входу которого подключен первый выход триггера, а второй выход триггера соединен с входом первого элемента И, второй вход которого соединен с дополнительным выходом блока опробования и памяти. Кроме того узел формирования сигналов «Сброс состоит из трех выходных формирователей импульсов , двух ключей и триггера, причем выходы триггера подключены

к одному из входов двух КЛЮчеи, Д)

входы которых объединены и яи.Шкпся входом узла формирования сигналов «(брос, выход первого ключа является одним из выходов «Сброс узла формирования сигиалов «Сброс, а выход второго ключа нодключен к одному из входов иервого, второго выходных формирователей импульсов и триггера, другой вход которого объединен с управляющим входом первого ключа и входом третьего выходного формирователя импульсов и является вторым входом узла формирования сигналов «Сброс, а второй вход первого выходного формирователя импульсов является третьим входом узла формирования сигналов «Сброс.

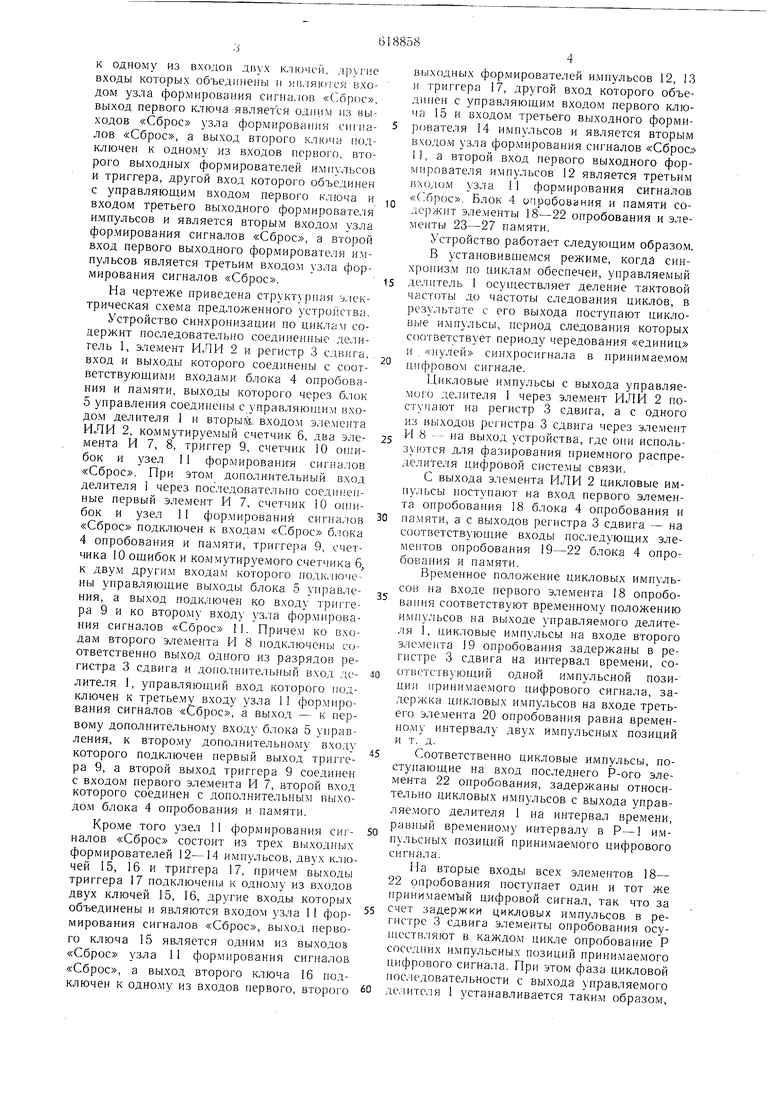

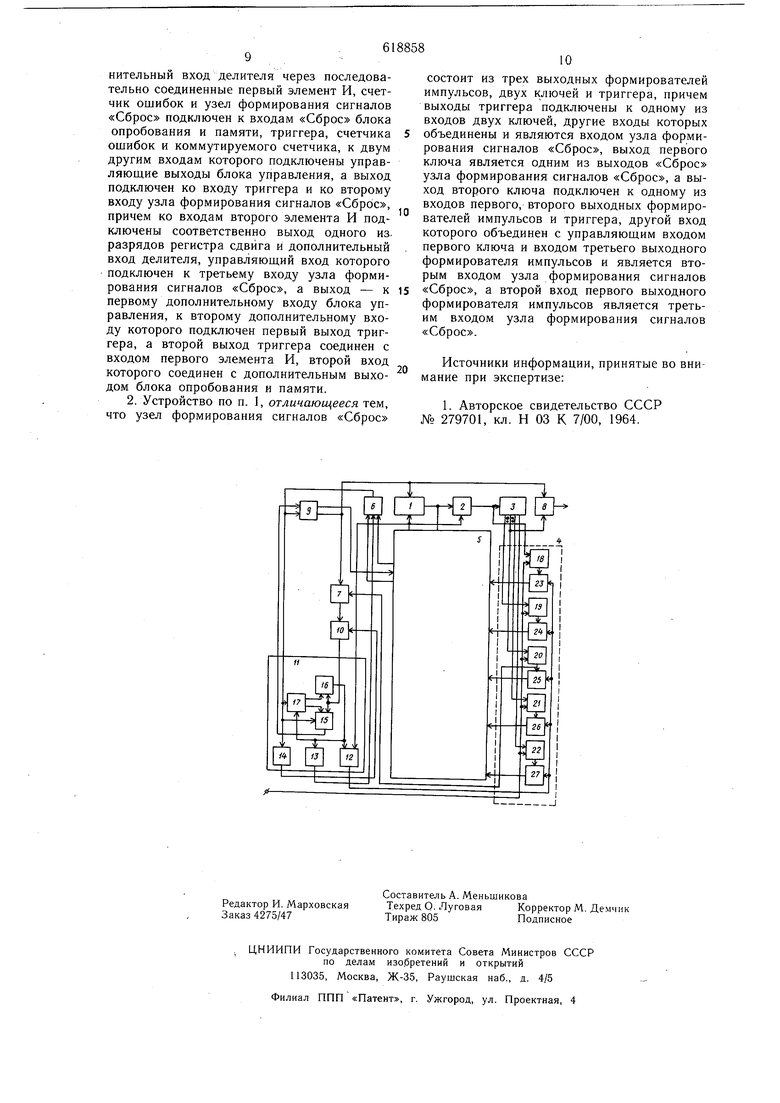

На чертеже приведена структурная : лектрическая схема предложенного устройства.

Устройство синхронизации по циклам содержит последовательно соединенные делигель 1, элемент ИЛИ 2 и регистр 3 сдв.ига, вход и выходы которого соедине Нз1 с соответствующими входами блока 4 опробования и памяти, выходы которого через блок 5 управления соединены с унравляюни-1м входом делителя 1 и вторыК входо.м эле.ме1гта ИЛИ 2, коммутируемый счетчик 6, два элемента И 7, 8, триггер 9, счетчик 10 OHJHбок и узел 11 формирования сигналов «Сброс. При этом дополнительный вход делителя I через последовательно соединенные первый элемент И 7, счетчик 10 ошибок и узел 11 формирования сигна.юв «Сброс подключен к входа.м «Сброс блока 4 опробования и памяти, триггера 9, счетчика 10 ощибок и коммутируемого счетчика б, к дву.м другим входам которого Г1одк,1ючены управляющие выходы блока 5 управления, а выход нодключен ко входу триггера 9 и ко второму входу узла формирования сигналов «Сброс 11. Причем ко входам второго элемента И 8 подключены соответственно выход одного из разрядов регистра 3 сдвига и дополнительный вход делителя 1, управляющий вход которого нодключен к третьему входу узла 11 формирования сигналов «Сброс, а выход - к первому дополнительному входу блока 5 управления, к второ.му дополнительному входу которого подключен первый выход трипера 9, а второй выход триггера 9 соединен с входом первого эле.мента И 7, второй вход которого соединен с дополнительным выходом блока 4 опробования и памяти.

Кро.ме того узел 11 формирования сигналов «Сброс состоит из трех выходных формирователей 12-14 импульсов, двух ключей 15, 16 и триггера 17, причем выходы триггера 17 подключены к одно.му из входов двух ключей 15, 16, другие входы которых объединены и являются входо.м узла 11 формирования сигналов «Сброс, выход первого ключа 15 является одним из выходов «Сброс узла 11 формирования сигналов «Сброс, а выход второго ключа 16 нодключен к одному из входов первого, второго

выходных фор.мирователей и.мпульсов 12, 13 и триггера 17, другой вход которого объединен с управляющим входом первого ключа 15 и входом третьего выходного форми5 р(вателя 14 и.чпульсов и является вторым входом узла формирования сигналов «Сброс 11, а второй вход нервого выходного формирователя и.мпульсов 12 является третьим входом узла 11 формирования сигналов «(брос. Блок 4 огфобования и памяти содержит элементы 18-22 опробования и эле.менты 23-27 памяти.

Устройство работает следующим образом. В установивщемся режиме, когда синхронизм но циклам обеспечен, управляемый

5 1 осупгествляет деление тактовой частоты до частоты следования циклов, в )езу;1ьтате с его выхода поступают цикловые имнульсы, период следования которых соответствует периоду чередования «единиц и . «)1улей синхросигнала в принимае.мом

цифровом сигнале.

Цикловые и.мпульсы с выхода управляемого делителя I через элемент ИЛИ 2 поступают на регистр 3 сдвига, а с одного из выходов ре1истра 3 сдвига через эле.мент И 8 - на выход устройства, где они используются для фазирования нриемного распределителя цифровой систе.мы связи.

С выхода элемента ИЛИ 2 цикловые имну;1ьсы поступают на вход первого элемента онробоваЕ ия 18 блока 4 опробования и

0 па.мяти, а с вьгходов регистра 3 сдвига - на соответствующие входы последующих элементов опробования 19-22 блока 4 опробования и памяти.

Временное положение цикловых импульсов на входе первого элемента 18 опробования соответствуют вре.менно.му положению импульсов на выходе управляемого делителя 1, цикловые имнульсы на входе второго эле.мента 19 онробования задержаны в регистре 3 сдвига на интервал вре.мени, соответствующий одной импульсной позиции принимаемого цифрового сигнала, задержка цикловых и.мпульсов на входе третьего эле.мента 20 онробования равна временно.му интервалу двух импульсных позиций и т. д.

5Соответственно цикловые импульсы, поступающие на вход последнего Р-ого элемента 22 опробования, задержаны относительно цикловых импульсов с выхода управляемого делителя 1 на интервал времени, равный вре.менно.му интервалу в Р-1 и.мпульсных позиций принимаемого цифрового сигнала.

На вторые входы всех элементов 18- 22 опробования поступает один и тот же принимаемый цифровой сигнал, так что за

5 счет задержки цикловых импульсов в регистре 3 сдвига элементы опробования осуН1сствляют в каждом цикле опробование Р соседних импульсных позиций принимаемого цифрового сигнала. При этом фаза цикловой последовательности с выхода управляемого

делителя 1 устанавливается таким образом.

что в установившемся режиме символы синхросигнала оиробуются средним элементом 20 опробования, а остальные элементы иробования опробуют имнульсные позинии при.нимаемого цифрового сигнала, соседние синхропозиции справа и слева.

В устаиовиви емся режиме сигналы с выхода триггера 9 обеспечивают ноступление цикловых импульсов через э,:1емент И 8 па выход устройства и прохождение импульсов ошибок с выхода среднего элемента 20 опробования через элемент И 7 на вход счетчика 10 онжбок.

Каждый из элементов опробования работает таким образом, что импульсы спгр1ала ошибки на его выходе отс тствуют только при строгом чередовании «единиц и «нулей на ..опробуемых импульсных позициях прииимаемого ци()р( вого сигна.ла. Каждое нарушение чередования, т. е. появлепие подряд на опробуемых позициях двух символов «единица или двух С1.мво.лов «нуль, вызь1вает появление на выходе элеме1Г1а опробования импульса сигнала ои:ибки.

В установившемся режиме ноддержания синхронизма но цик.чам через каждые Л циклов, где М - емкость ко.ммутируе.;ого счетчпка 6, с его выхода пс ступают импульсы, которые пройдя формирователь 14 импульсов, осунествляют сброс счетчика 10 ошибок, емкость которого меньн1е Л . Поэтому в установившемся pe/Kiii -e отдельные нарушения чередования спнхросимволов, обусловленные воздействием помех иа принимаемый rpynnoBoii сигпал, как нрави.ю, не приводят к появ.кнню и.миул1)Са на вьгходе счетчика 10 ош-ибок.

Если же за отмеряем1)1Й коммутируемым счетчиком 6 шггервал времени в М циклов будет иметь месте; N ошибок че)едования, то на выходе счетчпка 10 оишбок образуется импульс, который ноступает на узел 11 формирования сигналов «Сброс. В узле 11 формирования cni4ia;iOH триггер 17 переключения установ/кч имг1ул1А-ом с выхода коммутируемого счетчика 6 в такое положение, при котором открыт к.поч 16 п закрыт ключ 15. Соответственно импульс с выхода счетчика 10 он ибок проходит ключ 16 и через формирователи импульсов 12, 13 осуп1ествляет сброс к().1Л|утируемого ечетчика 6 и элементов 23--27 памяти и устанавливает триггер 17 пе|:1еключения в положение, при котором закрывается ключ 16 и открывается ключ 15.

Если появление и.мпульса на выходе счетчика 10 ошибок произоп1ло не из-за потери синхронизма, а из-за опшбок черелТования синхросигнала, обусловленных помехами, то маловероятно, что в следуюгцем от.меряемом коммутируемым счетчиком 6 временном интервале в М циклов опять будет обнаружено N ошибок чередования синхросимволов. И если этого не происходит, то есть, если на выходе счетчика 10 огнибок не образуется импульс, то импульс с выхода коммути

руемого счетчика 6 возврашает триггер 17 переключения в прежпее положепие, при котором открывается ключ 16 и закрывается ключ 15.

Импульс с выхода ко.ммутируемого счетчика 6, пройдя через формирователь ДА импульсов, осушествляет также сброс счетчика 10 опшбок. Если же имеет .место потеря циклового сипхронпзма, то после появления на выходе счетчика 10 ошибок первого импульса еледует ожидать, что на М циклов будет снова обнаружено не менее чем N оцшбок, чередования символов на позициях, опробуемых третьим элементом 20 пробовапия. В этом случае сигнал с выхода счетчика

10 О1пибок позволяет пройти импульсу с выхода ком.мутируемого счетчика 6 через ключ 15 и переключить триггер 9 в положение, соответствующее режиму поиска. Элементы

23-27 памяти при этом не сбрасываются, и, таким образом, в момент переключения триггера 9 в режим поиска элементы 23--27 памяти содержат информацию о том, имели или не имели место ошибки чередования символов на импульсных позициях, опробуемых элементами 18-22 опробования в течение предшествующих М циклов.

В режиме поиска сигналы с выхода триггера 9 запреп.1ают прохождение импульсов через элементы И 7, 8 и разрешают прохождение через блок 5 управления и.мпульсов списывания на вход ко.ммутируемого счетчика 6. Коммутируемый счетчик 6 в режиме поиска осупхествляет подсчет числа чередования «единиц и «нулей на позициях, опробуемых первым элементом 18 опробоваПИЯ.

Если в мо.мент переключения триггера 9 в режим поиска какой-либо элемент памяти 23-27 зафиксировал чередование «единиц и «нулей в течение предшествующих М циклов, то в режиме поиска корректирование управляе.мого делителя 1 ос}ш.ествляется таки.м образом, чтобы цосле корректирования позицию, где имело место чередование «единиц и «нулей, опробовал бы первый элемент 18 опробования. При это.м если чередование символов обнаружено д,вумя или несколькими элементами памяти, нервый элемент 18 опробования начинает опробовать позицию, на которой ранее было обнаружено чередование си.мволов элементом опробования с меньши.м номером.

Корректирование управляе.мого делителя 1 осуществляется блоком 5 управления на столько импульсных позиций, сколько эледментов опробования обнаружат ошибки чередования символов, причем в результате корректирования первый эле.мент 18 опробования начинает опробовать ту из импульсных позиций прини.маемого цифрового сигнала, из которой ранее было обнаружено чередование символов элементом опробования с меньшим но.мером. Если после потери циклового синхронизма новое положение синхронизма оказывается вблизи прежнего, то соответствующий из элементов 18-22 опробования в течение М циклов, предшествующих переключению триггера 9 в режим поиска, не обнаружит ошибок чередования. Соответственно после переключения триггера 9 в режим поиска и поступления с его выхода разрешающего сигнала на узел управления 5 осуществляется корректирование управляемого делителя 1, после чего синхросигнал начинает опробовать первый элемент 18 опробования. Через М циклов коммутируемый счетчик 6 фиксирует чередование символов на позиции, опробуемой элементом 18 опробования. При отсутствии в течение М циклов ошибок чередования с элемента 18 опробования на выходе коммутируемого счетчика 6 появляется импульс, переключающий триггер 9 в установившийся режим синхронизма по циклам. При этом переключении триггера 9 сигпал с выхода этого триггера, поступающий на управляемый делитель 1, осуществляет скачкообразную установку делителя 1 таким образом, чтобы далее в установившемся режиме синхросигнал опробовался средним элементом 20 опробования. Если же при потере циклового синхронизма оказывается, что новое положение синхронизма не лежит в окрестности прежнего, то после обнаружения этого факта по данным элементов 23-27 памяти начинается ускоренный поиск нового положение синхронизма. Если в режиме поиска все элементы 23- 27 памяти зафиксировали отсутствие чередования и пропустили сигналы ощибок чередования с выходов элементов 18-22 опробования через блок 5 управления к управляемому делителю 1, то осуществляется корректирование управляемого делителя 1 на Р и.маульсных позиций. Кроме того, в формирователе импульсов 12 «Сброса формируется импульс после последнего корректирующего импульса с выхода блока 5 управления, осуществляющий сброс элементов 23-27 памяти. Импульс с выхода схемы блока 5 управления, пройдя через элемент ИЛИ 2 и регистр 3 сдвига на входы элементов опробования 18-22 обеспечивает то, что начало опробования новых позиций принимаемого цифрового сигнала осуществляется в том же цикле, что и корректирование управляемого делителя 1 сигналами ощибок чередования. На вновь опробуемых позициях поиск синхросигнала осуществляется таким же образом. Элементы 18-22 опробования выявляют ошибки чередования символов на опробуемых позициях, причем импульсы ошибок с их выхода обеспечивают корректирование управляемого делителя 1 на столько импульсных позиций, сколько элементов опробования подряд обнаружили отсутствие чередования символов. Процесс поиска продолжается до тех пор, пока первый элемент опробования не будет опробовать чередующиеся символы в течение М циклов подряд. После этого на выходе коммутируемого счетчика 6 появляется импульс, переключающий триггер 9 в установивщийся режим поддержания синхрониз:М а. Затем по сигналу переключения с триггера 9 на управляемом делителе 1 осуществляется скачкообразная подстройка для того, чтобы в установившемся режиме синхропозиции принимаемого цифрового сигнала опробовались средним элементом 20 опробования. В установивщемся режиме с выхода триггера 9 на элементы И 7, 8 подаются разрешающие сигналы, а коммутируемый счетчик 6 переключается в режим счета цикловых импульсов с выхода блока 5 управления. Предлагаемое устройство позволяет обеспечить быстрое восстановление синхронизма по циклам как в тех случаях, когда новое положение циклового синхронизма находится вблизи прежнего, так и в случаях резких изменений фазы синхросигнала в принимаемом цифровом сигнале. Положительный эффект ускорения времени восстановления циклового синхронизма предлагаемым устройством достигается .а счет введения новых узлов и связей, а не за счет какого-либо ухудшения других основных показателей установления или поддержания синхронизма. В отличие от устройств содержащих несколько элементов с пробования и осуществляющих с их помощью параллельный анализ позиций циклов принимаемого сигнала, вероятность ложной фиксации состояния синхронизма не возрастает пропорционально числу используе :ыx элементов опробования. Это происходит потому, что как и в известном устройстве, фиксация нового состояния синхронизма осуществляется по результатам безошибочного опробования чередования символов только одним (первым) элементом опробования. Формула изобретения 1. Устройство синхронизации по циклам, содержащее последовательно соединенные делитель, элемент ИЛИ и регистр сдвига, вход и выходы которого соединены с соотв тствующими входами блока опробования и памяти, выходы которого через блок управления соединены с управляющим входом делителя и вторым входом элемента ИЛИ, отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм, введены коммутируемый счетчик, два элемента И, триггер, счетчик ошибок и узел формировг1ния сигналов «Сброс, при этом дополнительныи вход делителя через последовательно соединенные первый элемент И, счетчик ошибок и узел формирования сигналов «Сброс подключен к входам «Сброс блока опробования и памяти, триггера, счетчика ошибок и коммутируемого счетчика, к двум другим входам которого подключены управляющие выходы блока управления, а выход подключен ко входу триггера и ко второму входу узла формирования сигналов «Сброс, причем ко входам второго элемента И подключены соответственно выход одного из. разрядов регистра сдвига и дополнительный вход делителя, управляющий вход которого подключен к третьему входу узла формирования сигналов «Сброс, а выход - к первому дополнительному входу блока управления, к второму дополнительному входу которого подключен первый выход триггера, а второй выход триггера соединен с входом первого элемента И, второй вход которого соединен с дополнительным выходом блока опробования и памяти. 2. Устройство по п. 1, отличающееся тем, что узел формирования сигналов «Сброс состоит из трех выходных формирователей импульсов, двух ключей и триггера, причем выходы триггера подключены к одному из входов двух ключей, другие входы которых объединены и являются входом узла формирования сигналов «Сброс, выход первого ключа является одним из выходов «Сброс узла формирования сигналов «Сброс, а выход второго ключа подключен к одному из входов первого, второго выходных формирователей импульсов и триггера, другой вход которого объединен с управляющим входом первого ключа и входом третьего выходного формирователя импульсов и является вторым входом узла формирования сигналов «Сброс, а второй вход первого выходного формирователя импульсов является третьим входом узла формирования сигналов «Сброс. Источники информации, принятые во внимание при экспертизе: 1 Авторское свидетельство СССР № 279701, кл. Н 03 К 7/00, 1964.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1431074A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU300955A1 |

Авторы

Даты

1978-08-05—Публикация

1976-06-01—Подача